AMERICAN DATA AQUISITION CORPORATION

5525MF, 5550MF

|

Card Type |

Data Aquisition |

|

Chip Set |

Unidentified |

|

Maximum Onboard Memory |

Unidentified |

|

I/O Options |

Analog input, digital input |

|

Hard Drives supported |

None |

|

Floppy drives supported |

None |

|

Data Bus |

8-bit ISA |

|

Card Size |

Full-length |

|

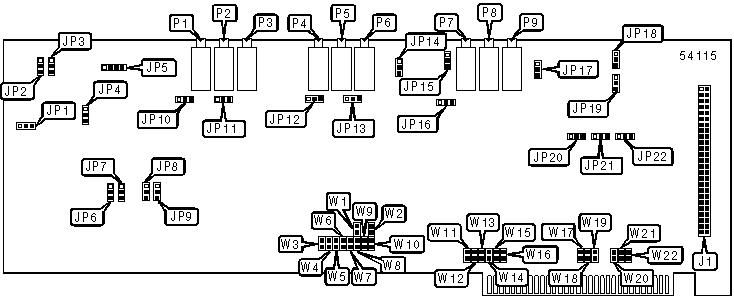

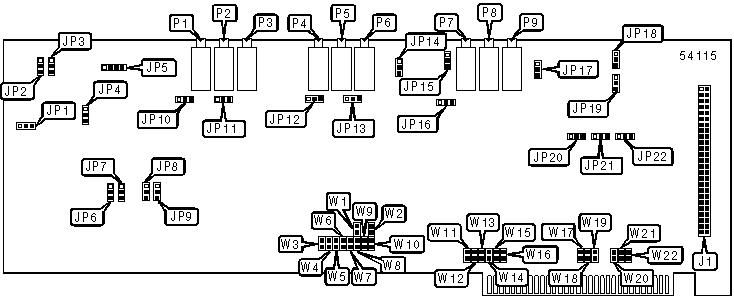

CONNECTIONS |

|||

|

Function |

Label |

Function |

Label |

|

50-pin analog/digital signals connector |

J1 |

DAC1 bipolar offset selector |

P5 |

|

DACO converter gain selector |

P1 |

DAC1 unipolar offset selector |

P6 |

|

DAC0 bipolar offset selector |

P2 |

A/D converter gain selector |

P7 |

|

DAC0 unipolar offset selector |

P3 |

A/D bipolar offset selector |

P8 |

|

DAC1 converter gain selector |

P4 |

A/D unipolar offset selector |

P9 |

|

USER CONFIGURABLE SETTINGS |

|||

|

Function |

Label |

Position |

|

|

» |

Counter 0 out hardware trigger source |

JP2 |

Pins 1 & 2 closed |

|

|

TRIG/GATE input hardware trigger source |

JP2 |

Pins 2 & 3 closed |

|

» |

Mux address lines disabled |

W1 |

Open |

|

|

Mux address lines enabled |

W1 |

Closed |

|

» |

Mux control lines disabled |

W2 |

Open |

|

|

Mux control lines enabled |

W2 |

Closed |

|

COUNTER SOURCE SETTINGS |

||||

|

Counter |

Setting |

Label |

Position |

|

|

» |

Counter 2 clock source |

External (clock 2) |

JP1 |

Pins 2 & 3 closed |

|

|

Counter 2 clock source |

1.00 MHz oscillator |

JP1 |

Pins 1 & 2 closed |

|

» |

Counter 1 clock source |

1.00 MHz oscillator |

JP3 |

Pins 1 & 2 closed |

|

|

Counter 1 clock source |

External (clock 1) |

JP3 |

Pins 2 & 3 closed |

|

» |

Counter 0 gate source |

External (gate 0) |

JP4 |

Pins 2 & 3 closed |

|

|

Counter 0 gate source |

Counter 1 out INV |

JP4 |

Pins 1 & 2 closed |

|

POWER CONFIGURATION SELECTION |

|||

|

Signal |

Label |

Position |

|

|

» |

Clock 2 |

JP20 |

Pins 1 & 2 closed |

|

|

+12V (fused) |

JP20 |

Pins 2 & 3 closed |

|

» |

Out 2 |

JP21 |

Pins 1 & 2 closed |

|

|

AGND |

JP21 |

Pins 2 & 3 closed |

|

» |

Gate 2 |

JP22 |

Pins 1 & 2 closed |

|

|

-12V (fused) |

JP22 |

Pins 2 & 3 closed |

|

ERROR INTERRUPT SELECTION |

||

|

Setting |

JP5 |

|

|

» |

Interrupt disabled |

Pins 1 & 2 closed |

|

|

Software control via ADCSR0 bit 6 |

Pins 2 & 3 closed |

|

|

Interrupt enabled |

Pins 3 & 4 closed |

|

Note: Error conditions include clock overrun, polled I/O data overrun and DMA overrun on A/D converter. |

||

|

DMA CHANNEL SELECTION |

|||||||

|

Channel |

W17 |

W18 |

W19 |

W20 |

W21 |

W22 |

|

|

|

1 |

Closed |

Open |

Open |

Closed |

Open |

Open |

|

|

2 |

Open |

Closed |

Open |

Open |

Closed |

Open |

|

» |

3 |

Open |

Open |

Closed |

Open |

Open |

Closed |

|

ANALOG OUTPUT CONFIGURATION (DAC0) |

||||||

|

Data Coding |

Polarity |

Range |

JP8 |

JP10 |

JP11 |

|

|

» |

Two's compliment |

Bipolar |

-10V to +10V |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 |

|

|

Two's compliment |

Bipolar |

-5V to +5V |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 2 & 3 |

|

|

Straight/offset binary |

Unipolar |

0V to +10V |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 |

|

Note: DAC0 and DAC1 may be configured independently. Pins designated are in the closed position. |

||||||

|

ANALOG OUTPUT CONFIGURATION (DAC1) |

||||||

|

Data Coding |

Polarity |

Range |

JP9 |

JP12 |

JP13 |

|

|

» |

Two's compliment |

Bipolar |

-10V to +10V |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 |

|

|

Two's compliment |

Bipolar |

-5V to +5V |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 2 & 3 |

|

|

Straight/offset binary |

Unipolar |

0V to +10V |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 |

|

Note: DAC0 and DAC1 may be configured independently. Pins designated are in the closed position. |

||||||

|

ANALOG INPUT REFERENCE CONFIGURATION |

|||||

|

Setting |

JP6 |

JP7 |

JP18 |

JP19 |

|

|

» |

Pseudo differential (PD) |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

|

|

Single ended (SE) |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 2 & 3 |

|

|

Fully differential (DI) |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 2 & 3 |

Open |

|

Note: Pins designated are in the closed position. |

|||||

|

ANALOG INPUT RANGE CONFIGURATION |

||||||

|

Polarity |

Range |

JP14 |

JP15 |

JP16 |

JP17 |

|

|

» |

Bipolar |

-10V to +10V |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 |

|

|

Bipolar |

-5V to +5V |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 2 & 3 |

Pins 2 & 3 |

|

|

Unipolar |

0V to +10V |

Pins 2 & 3 |

Pins 1 & 2 |

Pins 2 & 3 |

Pins 1 & 2 |

|

Note: Pins designated are in the closed position. |

||||||

|

BASE I/O ADDRESS SELECTION |

|||||||||

|

Setting |

W3 |

W4 |

W5 |

W6 |

W7 |

W8 |

W9 |

W10 |

|

|

|

000h |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

|

|

020h |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

|

|

040h |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

|

|

060h |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Closed |

|

|

080h |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

|

» |

200h |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

|

|

F60h |

Closed |

Closed |

Closed |

Closed |

Closed |

Open |

Closed |

Closed |

|

|

F80h |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Open |

Open |

|

|

FA0h |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Open |

Closed |

|

|

FC0h |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Open |

|

|

FE0h |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

|

Note: A total of 256 base address settings are available. The jumpers are a binary representation of the decimal memory addresses. W3 is the Most Significant Bit and jumper W10 is the Least Significant Bit. The jumpers have the following decimal values: W3=4096, W4=2048, W5=1024, W6=512, W7=256, W8=128, W9=64, W10=32. Turn off the switches and add the values of the switches to obtain the correct memory address. (Close=1, Open=0) |

|||||||||

|

IRQ INTERRUPT SELECTION |

|||||||

|

IRQ |

W11 |

W12 |

W13 |

W14 |

W15 |

W15 |

|

|

|

IRQ2 |

Closed |

Open |

Open |

Open |

Open |

Open |

|

|

IRQ3 |

Open |

Closed |

Open |

Open |

Open |

Open |

|

|

IRQ4 |

Open |

Open |

Closed |

Open |

Open |

Open |

|

|

IRQ5 |

Open |

Open |

Open |

Closed |

Open |

Open |

|

|

IRQ6 |

Open |

Open |

Open |

Open |

Closed |

Open |

|

» |

IRQ7 |

Open |

Open |

Open |

Open |

Open |

Open |