DECISION COMPUTER INTERNATIONAL CO., LTD.

IPC8255/8254

|

Card Type |

Data acquisition |

|

Chipset |

8254/8255 |

|

I/O Options |

Digital I/O lines (24) |

|

Data Bus |

IPCCPU expansion bus |

|

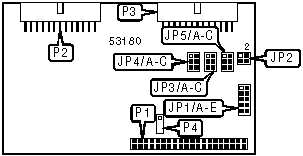

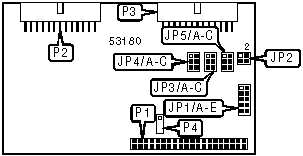

CONNECTIONS | |||

|

Function |

Label |

Function |

Label |

|

IPCCPU expansion bus |

P1 |

8254 clock signals (see pinout below) |

P3 |

|

8255 digital I/O lines 1-24 (see pinout below) |

P2 |

Unidentified |

P4 |

|

P2 PINOUT | |||

|

Function |

Pin |

Function |

Pin |

|

Channel 0 bit 0 |

1 |

Channel 1 bit 5 |

14 |

|

Channel 0 bit 1 |

2 |

Channel 1 bit 6 |

15 |

|

Channel 0 bit 2 |

3 |

Channel 1 bit 7 |

16 |

|

Channel 0 bit 3 |

4 |

Channel 2 bit 0 |

17 |

|

Channel 0 bit 4 |

5 |

Channel 2 bit 1 |

18 |

|

Channel 0 bit 5 |

6 |

Channel 2 bit 2 |

19 |

|

Channel 0 bit 6 |

7 |

Channel 2 bit 3 |

20 |

|

Channel 0 bit 7 |

8 |

Channel 2 bit 4 |

21 |

|

Channel 1 bit 0 |

9 |

Channel 2 bit 5 |

22 |

|

Channel 1 bit 1 |

10 |

Channel 2 bit 6 |

23 |

|

Channel 1 bit 2 |

11 |

Channel 2 bit 7 |

24 |

|

Channel 1 bit 3 |

12 |

Ground |

25 |

|

Channel 1 bit 4 |

13 |

+5V DC power |

26 |

|

P3 PINOUT | |||

|

Function |

Pin |

Function |

Pin |

|

Channel 1 bit 0 |

1 |

Clock signal 1 in |

8 |

|

Clock signal 0 in |

2 |

Channel 1 bit 4 |

9 |

|

Channel 1 bit 1 |

3 |

Gate signal 1 out |

10 |

|

Gate signal 0 out |

4 |

Channel 1 bit 5 |

11 |

|

Channel 1 bit 2 |

5 |

Clock signal 1 out |

12 |

|

Clock signal 0 out |

6 |

Channel 1 bit 6 |

13 |

|

Channel 1 bit 3 |

7 |

Clock signal 2 in |

14 |

|

P3 PINOUT (CON’T) | |||

|

Function |

Pin |

Function |

Pin |

|

Channel 1 bit 7 |

15 |

4.9152MHz clock signal |

21 |

|

Gate signal 2 out |

16 |

Inverse of clock signal 1 out |

22 |

|

TO1 signal |

17 |

2.4576MHz clock signal |

23 |

|

Clock signal 2 out |

18 |

Inverse of clock signal 2 out |

24 |

|

9.8304MHz clock signal |

19 |

Ground |

25 |

|

Inverse of clock signal 0 out |

20 |

+5V DC power |

26 |

|

USER CONFIGURABLE SETTINGS | |||

|

Setting |

Label |

Position | |

| » |

Card is first card |

JP2 |

Pins 3 & 4 closed |

|

Card is second card |

JP2 |

Pins 1 & 2 closed | |

|

BASE I/O ADDRESS SELECTION | ||||||

|

Setting |

JP1/A |

JP1/B |

JP1/C |

JP1/D |

JP1/E | |

|

90h |

Closed |

Open |

Open |

Open |

Open | |

|

A0h |

Open |

Closed |

Open |

Open |

Open | |

| » |

B0h |

Open |

Open |

Closed |

Open |

Open |

|

C0h |

Open |

Open |

Open |

Closed |

Open | |

|

E0h |

Open |

Open |

Open |

Open |

Closed | |

|

CLOCK 0 RATE SELECTION | ||||

|

Setting |

JP3/A |

JP3/B |

JP3/C | |

| » |

2.4576MHz |

Open |

Open |

Closed |

|

4.9152MHz |

Open |

Closed |

Open | |

|

9.8304MHz |

Closed |

Open |

Open | |

|

CLOCK 1 RATE SELECTION | ||||

|

Setting |

JP4/A |

JP4/B |

JP4/C | |

| » |

2.4576MHz |

Open |

Open |

Closed |

|

4.9152MHz |

Open |

Closed |

Open | |

|

9.8304MHz |

Closed |

Open |

Open | |

|

CLOCK 2 RATE SELECTION | ||||

|

Setting |

JP5/A |

JP5/B |

JP5/C | |

| » |

2.4576MHz |

Open |

Open |

Closed |

|

4.9152MHz |

Open |

Closed |

Open | |

|

9.8304MHz |

Closed |

Open |

Open | |

|

MISCELLANEOUS TECHNICAL NOTES |

|

This card is designed to be used with Decision Computer International Co., Ltd.’s IPCCPU board. See this document for more information. |