QUATECH, INC.

MPA-200/300

|

Card Type |

I/O controller |

|

Chipset/Controller |

Intel |

|

I/O Options |

Serial port |

|

Maximum DRAM |

N/A |

|

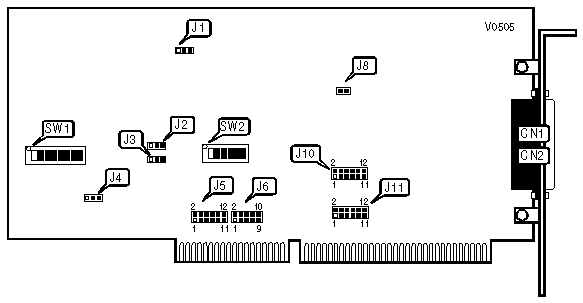

CONNECTIONS | |

|

Purpose |

Location |

|

Female D-25 serial port - data communications equipment |

CN1 |

|

(Optional) Male D-25 serial port - data terminal equipment |

CN2 |

|

Note: The MPA 200 is either DCE or DTE port equipped, but not both | |

|

CLOCK SPEED SELECT | ||

|

Speed |

J1 | |

| » |

8MHz |

Pins 1 & 2 closed |

|

6MHz |

Pins 2 & 3 closed | |

|

INTERRUPT SHARING | |

|

Setting |

J4 |

|

Enabled |

Pins 1 & 2 closed |

|

Disabled |

Pins 2 & 3 closed |

|

INTERRUPT SELECTION | ||

|

IRQ |

J5 |

J6 |

|

IR/FONT> |

Pins 1 & 7 closed |

Open |

|

IRQ3 |

Pins 2 & 8 closed |

Open |

|

IRQ4 |

Pins 3 & 9 closed |

Open |

|

IRQ5 |

Pins 4 & 10 closed |

Open |

|

INTERRUPT SELECTION | ||

|

IRQ |

J5 |

J6 |

|

IRQ6 |

Pins 5 & 11 closed |

Open |

|

IRQ7 |

Pins 6 & 12 closed |

Open |

|

IRQ10 |

Open |

Pins 1 & 6 closed |

|

IRQ11 |

Open |

Pins 2 & 7 closed |

|

IRQ12 |

Open |

Pins 3 & 8 closed |

|

IRQ14 |

Open |

Pins 4 & 9 closed |

|

IRQ15 |

Open |

Pins 5 & 10 closed |

|

DMA TRANSMIT CHANNEL | |

|

Setting |

J10 |

|

Channel 1 |

Pins 1 & 7, 2 & 8 closed |

|

Channel 2 |

Pins 3 & 9, 4 & 10 closed |

|

Channel 3 |

Pins 5 & 11, 6 & 12 closed |

|

DMA RECEIVE CHANNEL | |

|

Setting |

J11 |

|

Channel 1 |

Pins 1 & 7, 2 & 8 closed |

|

Channel 2 |

Pins 3 & 9, 4 & 10 closed |

|

Channel 3 |

Pins 5 & 11, 6 & 12 closed |

|

Note: Do not use the same channel for both DMA transmit and receive functions. Closing the same Pins on J10 and J11 will result in damage to the system. | |

|

LINE DRIVER CONTROL | |

|

Setting |

J7 |

|

Drivers and receivers always enabled |

Pins 1 & 2, 4 & 5 closed |

|

Drivers and receivers controlled by programming register |

Pins 2 & 3, 5 & 6 closed |

|

Note: Location of J7 is not specified on manufacturer documentation. | |

|

SYNCA/RLEN CONFIGURATION | |

|

Setting |

J8 |

|

SYNCA |

Closed |

|

RLEN |

Open |

|

I/O ADDRESS CONFIGURATION | ||

|

Address |

SW1 |

SW2 |

|

300h |

1, 2, 3, 4, 5 & 6 on |

1, 2, 3, 4, 5 & 6 on |

|

240h |

1, 2, 3, 4, 5, 6 & 8 on |

1, 3, 4, 5 & 6 on |

|

6FC4h |

1 & 4 on |

3, 4 & 5 on |

|

Note:The address range for the DMM-100 is from 0 to FFFFh. The switches are a binary representation of the addresses. The switches have the following decimal values: SW1/1=8, SW1/2=4, SW1/3=2, SW1/4=1, SW1/5=8, SW1/6=4, SW1/7=2, SW1/8=1, SW2/1=8, SW2/2=4, SW2/3=2, SW2/4=1, SW2/5=8, SW2/6=4. | ||

|

FACTORY CONFIGURED SETTINGS | |

|

Jumper |

Setting |

|

J2 |

N/A |

|

J3 |

N/A |