FREE COMPUTER TECHNOLOGY, INC.

80486L-EISA

|

Processor |

80486SX/80487SX/80486DX/80486DX2 |

|

Processor Speed |

20/25/33/50(internal)/50/66(internal)MHz |

|

Chip Set |

SIS |

|

Max. Onboard DRAM |

128MB |

|

SRAM Cache |

64/128/256/512KB |

|

BIOS |

Phoenix |

|

Dimensions |

330mm x 218mm |

|

I/O Options |

32-bit L-ISA local bus card slot |

|

NPU Options |

None |

|

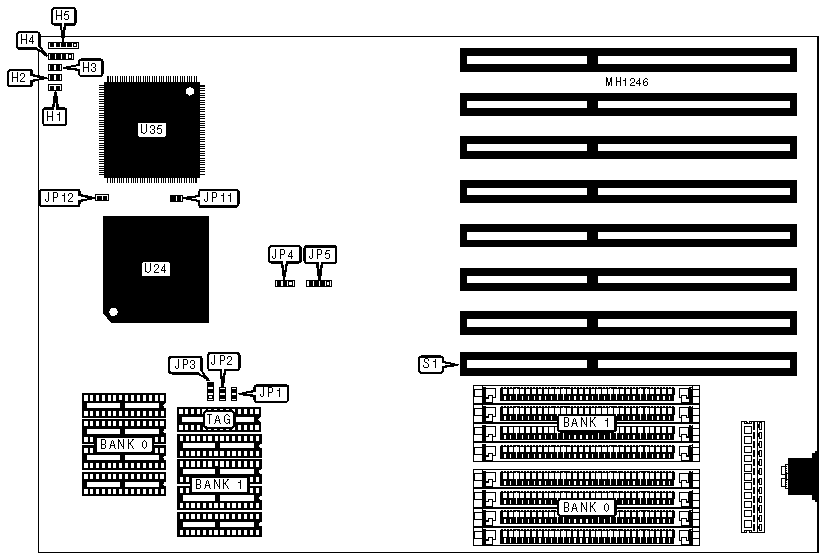

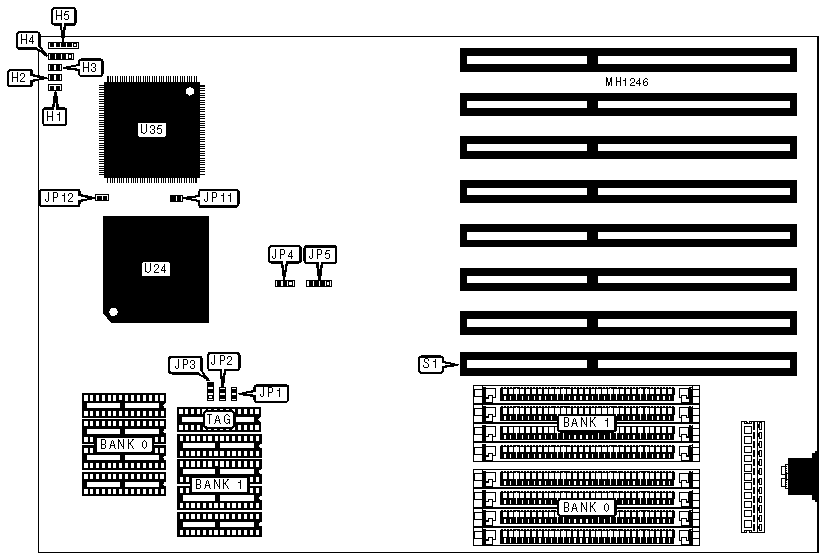

C ONNECTIONS | |||

|

Purpose |

Location |

Purpose |

Location |

|

Turbo LED |

H1 |

Speaker |

H4 |

|

Reset switch |

H2 |

Power LED & keylock |

H5 |

|

Turbo switch |

H3 |

32-bit L-ISA local bus card |

S1 |

|

CPU TYPE CONFIGURATION | |||||

|

U24 |

U35 |

JP4 |

JP5 |

JP11 |

JP12 |

|

80486DX2 |

80486SX/DX |

pins 1 & 2 |

pins 1 & 2 and 3 & 4 |

open |

closed |

|

80487SX |

80486SX/DX |

pins 2 & 3 |

pins 1 & 2 and 3 & 4 |

open |

closed |

|

80486SX |

80486SX/DX |

open |

pins 2 & 3 |

open |

closed |

|

NONE |

80486SX/DX |

pins 1 & 2 |

pins 1 & 2 and 3 & 4 |

closed |

open |

|

Note:Pins designated should be in the closed position. U35 is a surface mount CPU that may or may not have been installed at the factory. U24 is a socketed CPU that has been installed at the factory, or can be installed by the user. | |||||

|

DRAM CONFIGURATION | ||

|

Size |

Bank 0 |

Bank 1 |

|

1MB |

(4) 256K x 9 |

NONE |

|

2MB |

(4) 256K x 9 |

(4) 256K x 9 |

|

4MB |

(4) 1M x 9 |

NONE |

|

8MB |

(4) 1M x 9 |

(4) 1M x 9 |

|

16MB |

(4) 4M x 9 |

NONE |

|

20MB |

(4) 1M x 9 |

(4) 4M x 9 |

|

32MB |

(4) 4M x 9 |

(4) 4M x 9 |

|

64MB |

(4) 16M x 9 |

NONE |

|

128MB |

(4) 16M x 9 |

(4) 16M x 9 |

|

SRAM JUMPER CONFIGURATION | |||

|

Size |

JP1 |

JP2 |

JP3 |

|

64KB |

open |

open |

open |

|

128KB |

open |

closed |

pins 1 & 2 closed |

|

256KB |

open |

closed |

pins 2 & 3 closed |

|

512KB |

closed |

closed |

pins 1 & 2 closed |

|

SRAM CONFIGURATION | |||

|

Size |

Cache SRAM |

Location |

TAG |

|

64KB |

(8) 8K x 8 |

Banks 0 & 1 |

(1) 8K x 8 |

|

128KB |

(4) 32K x 8 |

Bank 0 |

(1) 8K x 8 |

|

256KB |

(8) 32K x 8 |

Banks 0 & 1 |

(1) 32K x 8 |

|

512KB |

(4) 128K x 8 |

Bank 0 |

(1) 32K x 8 |