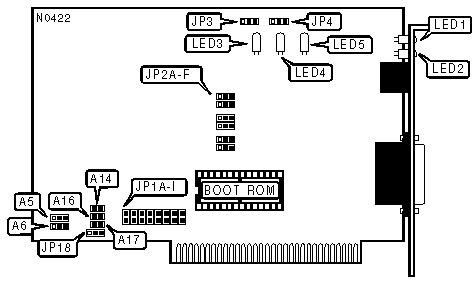

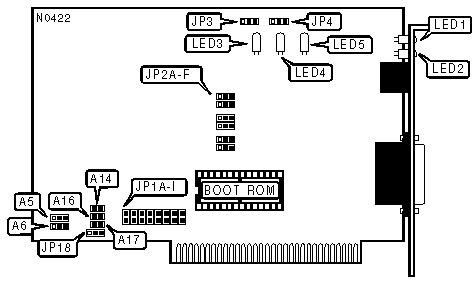

INTELLICOM, INC.

TPAIR-8T

|

NIC Type |

Ethernet |

|

Transfer Rate |

10Mbps |

|

Data Bus |

8-bit ISA |

|

Topology |

Star |

|

Wiring Type |

Unshielded twisted pair AUI transceiver via DB-15 port |

|

Boot ROM |

Available |

|

I/O BASE ADDRESS | ||

|

Address |

A5 |

A6 |

|

300 - 31Fh |

Pins 1 & 2 closed |

Pins 1 & 2 closed |

|

320 - 33Fh |

Pins 1 & 2 closed |

Pins 2 & 3 closed |

|

340 - 35Fh |

Pins 2 & 3 closed |

Pins 1 & 2 closed |

|

360 - 37Fh |

Pins 2 & 3 closed |

Pins 2 & 3 closed |

|

BOOT ROM ADDRESS | ||||

|

Address |

A14 |

A16 |

A17 | |

| » |

C8000h |

Closed |

Closed |

Closed |

|

CC000h |

Open |

Closed |

Closed | |

|

D8000h |

Closed |

Open |

Closed | |

|

DC000h |

Open |

Open |

Closed | |

|

E8000h |

Closed |

Closed |

Open | |

|

EC000h |

Open |

Closed |

Open | |

|

INTERRUPT REQUEST | |||||

|

IRQ |

JP1A |

JP1B |

JP1C |

JP1D | |

|

2 |

Closed |

Open |

Open |

Open | |

| » |

3 |

Open |

Closed |

Open |

Open |

|

4 |

Open |

Open |

Closed |

Open | |

|

5 |

Open |

Open |

Open |

Closed | |

|

DMA CHANNEL | |||||

|

Channel |

JP1E |

JP1F |

JP1H |

JP1I | |

| » |

Disabled |

Open |

Open |

Open |

Open |

|

DMA1 |

Closed |

Open |

Closed |

Open | |

|

DMA3 |

Open |

Closed |

Open |

Closed | |

|

CABLE TYPE | |

|

Type |

JP2A - JP2F |

|

Shielded/Unshielded twisted pair |

Pins 2 & 3 closed |

|

AUI transceiver via DB-15 port |

Pins 1 & 2 closed |

|

LINK INTEGRITY TEST | ||

|

Setting |

JP3 | |

| » |

Enabled |

Pins 2 & 3 closed |

|

Disabled |

Pins 1 & 2 closed | |

|

Note:The link integrity test is valid only when the cable type is shielded/unshielded twisted pair. If using a LattisNet network Link Integrity must be disabled (JP3 Pins 1 & 2 closed)

| ||

|

SIGNAL QUALITY ERROR (SQE) TEST | ||

|

Setting |

JP4 | |

| » |

Enabled |

Pins 2 & 3 closed |

|

Disabled |

Pins 1 & 2 closed | |

|

Note:Signal Quality Error (SQE) is an internal test of the collision circuitry and path. If using a LattisNet network SQE must be disabled (JP4 Pins 1 & 2 closed)

| ||

|

BOOT ROM | ||

|

Setting |

JP18 | |

| » |

Disabled |

Pins 2 & 3 closed |

|

Enabled |

Pins 1 & 2 closed | |

|

FACTORY CONFIGURED SETTINGS | |

|

Jumper |

Setting |

|

JP1G |

Open |

|

DIAGNOSTIC LED(S) | ||

|

LED |

Status |

Condition |

|

LED1 |

On |

Data is being transmitted |

|

LED1 |

Off |

Data is not being transmitted |

|

LED2 |

On |

Twisted pair network connection is good |

|

LED2 |

Off |

Twisted pair network connection is broken |

|

LED3 |

On |

Data is being received |

|

LED3 |

Off |

Data is not being received |

|

LED4 |

On |

Card is transmitting constantly (Jabber) |

|

LED4 |

Off |

Normal operation |

|

LED5 |

On |

Collision detected on network |

|

LED5 |

Off |

No collisions detected on network |