# Digital Technical Journal

Digital Equipment Corporation

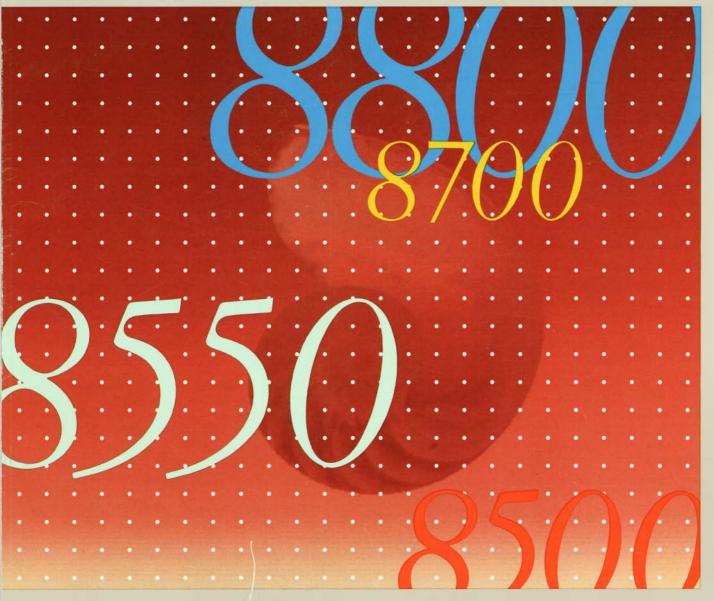

# Cover Design

This issue features the VAX 8800 family. Our cover depicts the growth of a chambered nautilus as a metaphor for the growth of the VAX family. As those chambers spiral from the center, so the power of the VAX family grows from the MicroVAX systems, through the VAX 8200 and 8300 CPUs, to the new VAX 8800 multiprocessor. The image was created using the Lightspeed system.

The cover was designed by Deborah Falck, Eddie Lee and Tsuneo Taniuchi of the Graphic Design Department.

#### **Editorial Staff**

Editor - Richard W. Beane

#### **Production Staff**

Production Editor — Jane C. Blake

Designer — Charlotte Bell

Interactive Page Makeup — Leslie K. Schoemaker

#### **Advisory Board**

Samuel H. Fuller, Chairman Robert M. Glorioso John W. McCredie Mahendra R. Patel F. Grant Saviers William D. Strecker

The *Digital Technical Journal* is published by Digital Equipment Corporation, 77 Reed Road, Hudson, Massachusetts 01749.

Changes of address should be sent to Digital Equipment Corporation, attention: Media Response Manager, 200 Baker Ave., CFO1-1/M94, Concord, MA 01742.

Comments on the content of any paper are welcomed. Write to the editor at Mail Stop HL02-3/K11 at the published-by address. Comments can also be sent on the ENET to RDVAX::BEANE or on the ARPANET to BEANE%RDVAX.DEC@DECWRL.

Copyright © 1987 Digital Equipment Corporation. Copying without fee is permitted provided that such copies are made for use in educational institutions by faculty members and are not distributed for commercial advantage. Abstracting with credit of Digital Equipment Corporation's authorship is permitted. Requests for other copies for a fee may be made to the Digital Press of Digital Equipment Corporation. All rights reserved.

The information in this journal is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

ISBN 1-55558-001-7

Documentation Number EY-6711E-DP

The following are trademarks of Digital Equipment Corporation: DEC, DECnet. the Digital logo, LN03 Plus, MicroVAX I, MicroVAX II, NMI, PDP-11, PDP-11/24, PDP-11/44, RSX, RSX-11M, RSX-11M-PLUS, SBI, UNIBUS, VAX, VAX-11/750, VAX-11/780, VAX-11/782, VAX 8200, VAX 8300, VAX 8500, VAX 8550, VAX 8600, VAX 8650, VAX 8700, VAX 8800, VAXBI, VAXBI 78732, VAXcluster, VAXstation, VAXstation II, VMS

ADA is a registered trademark of the U.S. Government Data General is a registered trademark of Data General Corporation

Harris is a trademark of Harris Corporation

IBM is a registered trademark of International Business Machines Corporation

Lightspeed is a trademark of Lightspeed Computers, Inc.

Motorola is a registered trademark of Motorola, Inc. SCALDSystem and ValidGED are trademarks of Valid Logic, Inc.

TK!Solver is a trademark of Software Arts, Inc.

UNIX is a trademark of American Telephone & Telegraph Company Bell Laboratories

Book production was done by Educational Services Media Communications Group in Bedford, MA.

# **Contents**

| 8 | Foreword     |       |  |

|---|--------------|-------|--|

|   | Donald J. Mc | Innis |  |

**New Products**

- 10 An Overview of the Four Systems in the VAX 8800 Family Robert M. Burley

- 20 The VAX 8800 Microarchitecture Sudhindra N. Mishra

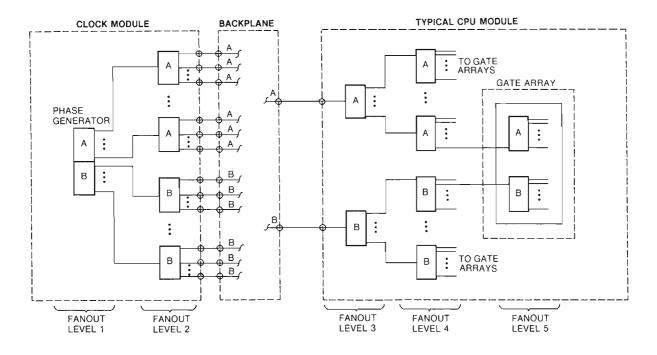

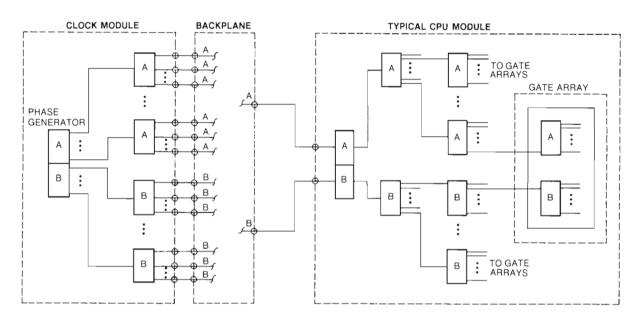

- The CPU Clock System in the VAX 8800 Family William A. Samaras

- 41 Aspects of the VAX 8800 C Box Design John Fu, James B. Keller, and Kenneth J. Haduch

- 52 **The Memory System in the VAX 8800 Family**Paul J. Natusch, David C. Senerchia, and Eugene L. Yu

- 62 Floating Point in the VAX 8800 Family

John H.P. Zurawski, Kathleen L. Pratt, and Tracey L. Jones

- 72 The VAX 8800 Input/Output System James P. Janetos

- 81 The VAXBI Bus A Randomly Configurable Design

Paul C. Wade

- 88 A Logical Grounding Scheme for the VAX 8800 Processor Michael W. Kement and Gerald J. Brand

- 100 The Simulation of Processor Performance for the VAX 8800 Family Cheryl A. Wiecek

- 111 VMS Multiprocessing on the VAX 8800 System Stuart J. Farnham, Michael S. Harvey, and Kathleen D. Morse

- 120 A Parallel Implementation of the Circuit Simulator SPICE on the VAX 8800 System Gabriel P. Bischoff and Steven S. Greenberg

- 129 The Impact of VAX 8800 Design Methodology on CAD Development Dennis T. Bak

- 136 On-line Manufacturing Data Access on the VAX 8800 Project Andrew J. Matthews

Richard W. Beane Editor

This issue features papers about the design of the VAX 8800 family of CPUs, written by members of the design team. The technology used in Digital's latest high-end machine, the VAX 8800 multiprocessor, also forms the basis for the other three family members: the 8700, 8550, and 8500 CPUs.

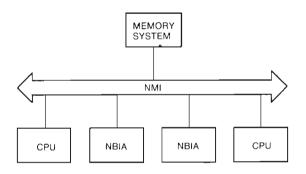

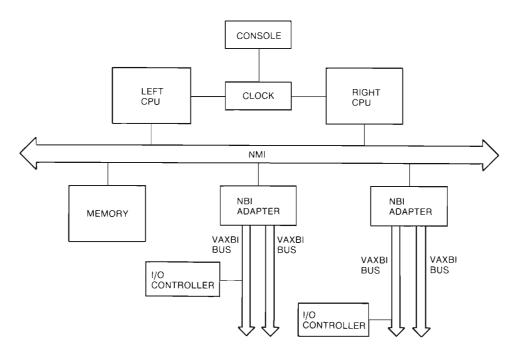

Bob Burley's overview relates the processes used in the 8800 design and the functions of the memory interconnect (NMI), the VAXBI I/O bus, and the four logic boxes forming the five-stage pipeline. The early discovery of design flaws and the use of automated tools helped to achieve an aggressive completion schedule.

The micromachine implements the microarchitecture and contains four of the five pipeline stages. Sudhin Mishra describes how microinstructions are handled, emphasizing the use of microbranches and microtraps to ensure coherency.

The VAX 8800 clock system, discussed by Bill Samaras, was designed using an automated timing verifier. He describes the trade-off between using the verifier and maximizing the accuracy of timing signals by minimizing their skew.

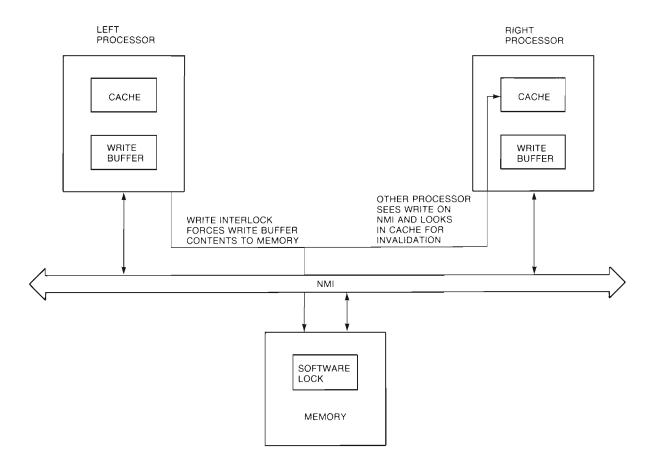

The C Box and the M Box are two parts of the pipeline. John Fu, Jim Keller, and Ken Haduch describe the C Box's no-write allocate cache and the delayed-write algorithm that ensures correct write-through. The C Box must also handle pipeline stall conditions and maintain data coherency between processors. The M Box handles read and write requests for the memory arrays. Paul Natusch, Dave Senerchia, and Gene Yu explain how the designs of the NMI and the

cache affected their design, and why they used TTL in the memory controller.

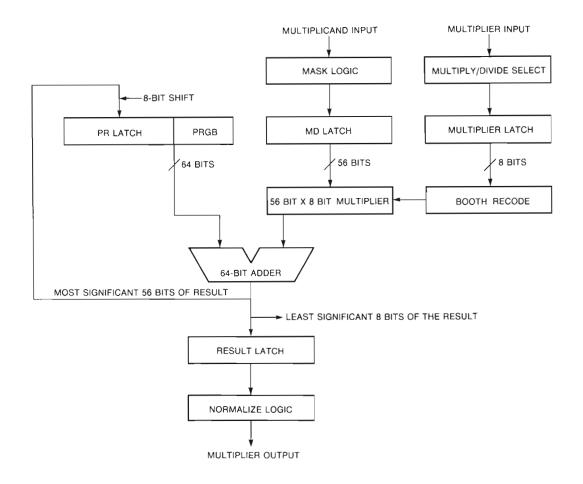

The VAX 8800 family does not have a separate floating point accelerator. As John Zurawski, Kathy Pratt, and Tracey Jones point out, however, a custom ECL unit achieves high performance through the normal datapaths. Thus less hardware is needed, and operands are fetched faster.

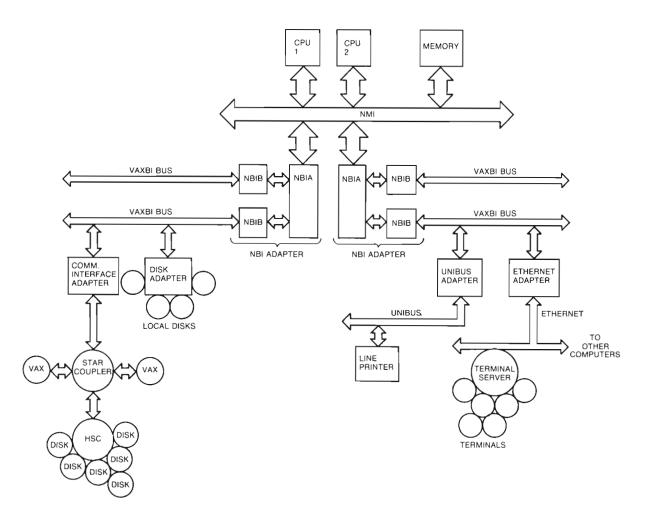

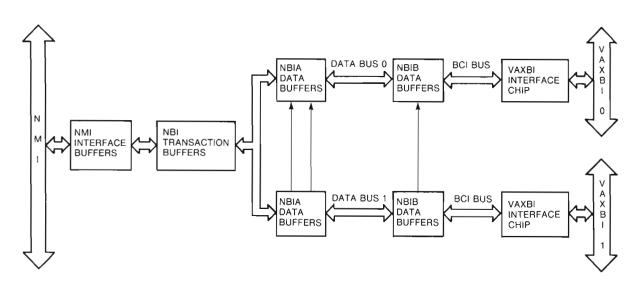

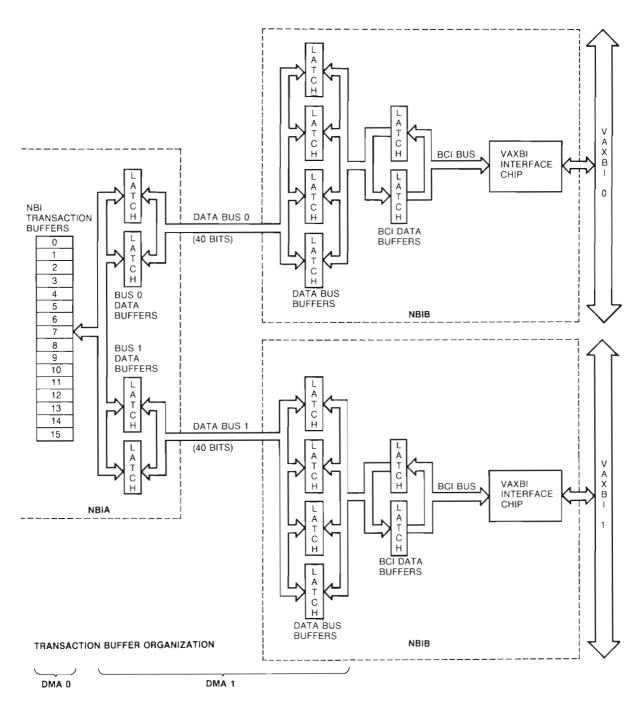

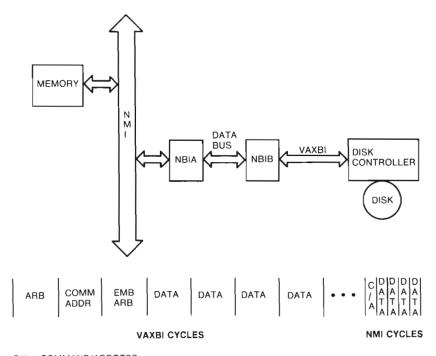

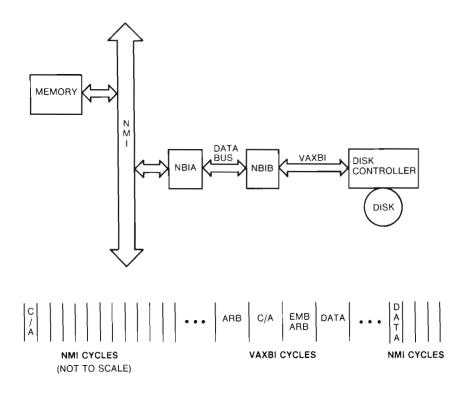

I/O devices are linked to the CPU by the VAXBI bus. In his paper, Jim Janetos discusses the NBI adapter, which contains logic to handle CPU references and DMA requests. Then Paul Wade describes how the VAXBI design team had to abandon the traditional approach and use a variety of techniques to specify the bus. Some chip problems were resolved only after a thorough analysis of the physical configuration.

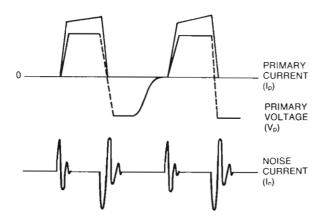

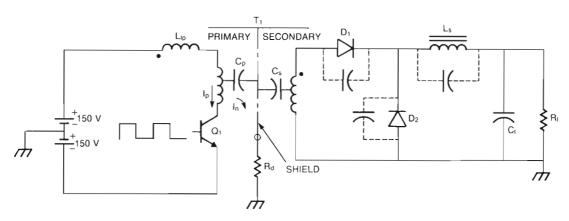

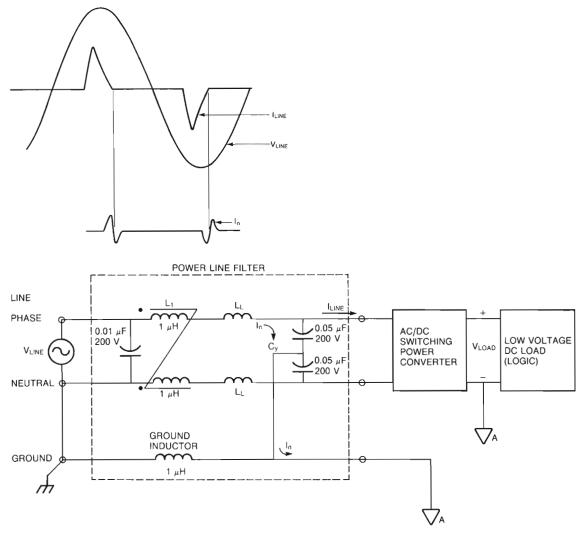

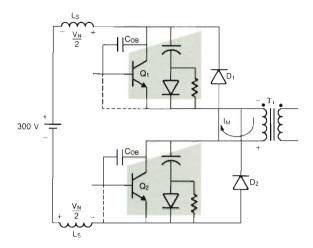

Jerry Brand and Mike Kement discuss the importance of using ground correctly as a signal conductor to achieve high performance. They describe the sources of ground-related noise in the CPU, and what they did to isolate and control those sources.

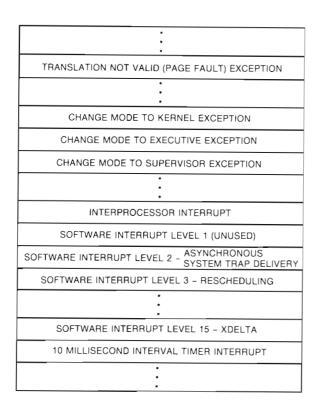

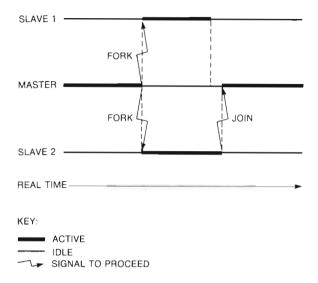

Many VMS features support multiprocessing. Stu Farnham, Mike Harvey, and Kathy Morse first describe the hardware that supports multiprocessing, then the interlocked instructions, exception handlers, and traps that implement VMS multiprocessing. To show how multiprocessing decreases execution time, Gabriel Bischoff and Steve Greenberg converted the SPICE circuit simulator into CAYENNE, a parallel program. They created master and slave processes that ran CAYENNE 1.7 times faster than SPICE.

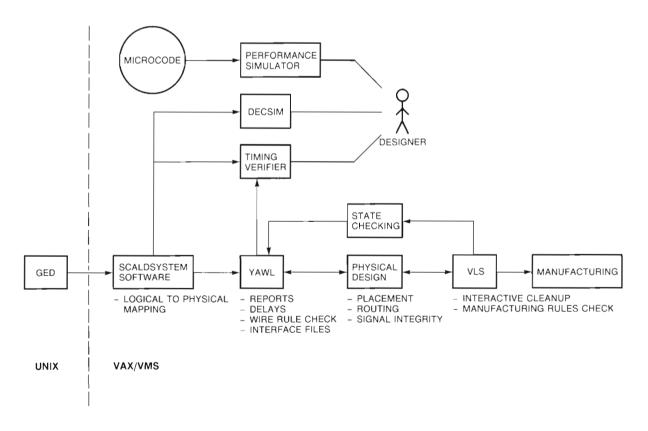

The final two papers relate some of the automated tools and techniques used on the 8800 project. Dennis Bak first describes building the CAD suite from existing tools, newly developed ones, and modifications. The methodology was truly innovative, serving as a framework for future projects. Then Andy Matthews discusses the on-line system that transformed CAD data into specifications used by Manufacturing. This system minimized the product start-up time by eliminating paperwork.

Dick Beane

# **Biographies**

**Dennis T. Bak** Dennis Bak is a principal software engineer in the Advanced VAX Development Group. As a project leader, he is currently developing new CAD tools to improve designer productivity on future design projects. In other positions, Dennis performed configuration testing for PDP-11 and VAX systems. Prior to joining Digital in 1980, he worked as a research engineer at Ford Motor Company, doing advanced development on electronic engine-control systems. Dennis earned a B.S. degree in electrical engineering from the University of Michigan in 1974.

Gabriel P. Bischoff In 1985, Gabriel Bischoff joined Digital after receiving a Diploma of Engineer and a Diploma of Advanced Studies in device physics from the Ecole Centrale de Lyon (1980) and a Ph.D. degree in E.E. from Cornell University (1985). As a senior software engineer in the Semiconductor Engineering Group, he is investigating the application of parallel computing architectures for VLSI CAD tools, particularly circuit simulators. Gabriel developed a parallel version of the circuit simulator SPICE for shared-memory multiprocessors. A member of IEEE, he has published papers on device modeling and circuit simulation.

Gerald J. Brand Jerry Brand is a principal engineer currently developing high-density, high-availability power systems. Prior to working on the power and packaging team for the VAX 8800 family, he designed two MPS power modules that are widely used in Digital's products. Before joining Digital in 1980, Jerry worked for over 14 years in disciplines ranging from oceanography to gas-turbine instrumentation. He holds a B.S.E.E. degree from the University of Illinois and participated in the M.S.E.E. program at the University of New Hampshire. Jerry teaches circuit analysis and electronics in the continuing education program at the University of Lowell.

Robert M. Burley As a senior product management manager, Bob Burley was the engineering product manager for the four systems in the VAX 8800 family. As a program manager in the LSI Acquisition and Test Group, he was responsible for relations with external vendors and acquiring technologies for the advanced gate arrays used in new CPU designs. Prior to joining Digital in 1980, Bob was a product and business development manager at Colt Industries, Inc., and a product and manufacturing manager at Scott Paper Company. He earned his B.S. degree in mathematics and economics from Hobart College in 1965.

**Stuart J. Farnham** As a principal software engineer in the VMS Development Group, Stu Farnham is currently working on future directions in multiprocessing. Earlier, he provided VMS support at the corporate level for Software Services. Stu was a developer and instructor for the VAX/VMS Systems Seminar. He joined Digital in 1982 after working as a software engineer at Pitney Bowes, Inc.

John Fu Currently earning his M.S. degree in computer science at the University of Illinois, John Fu was a principal engineer on the VAX 8800 project. He worked on the design of the C Box and configurations for the VAX 8800 family. Formerly, he worked on large-systems designs at International Computers Limited and on microprocessor control systems for Siemens Limited. John was also a project manager at Systems and Software, Inc. He received a B.Sc. (Hons) in computer science (1977) from the University of Manchester in England. John is a member of the British Computer Society and the IEE in England.

Steven S. Greenberg As a team leader in the CAD Department of the Semiconductor Engineering Group, Steve Greenberg codeveloped the CAYENNE program. An early provider of circuit and process simulators at Digital, he did research in timing verification and circuit simulators. As a Digital industrial fellow at the University of California at Berkeley, Steve performed research on iterated timing analysis. Before joining Digital in 1976, he was a member of the technical staff at RCA and a CAD engineer at Texas Instruments. Steve received a B.S.E.E. degree (1966) from M.I.T. and an M.S.E.E. degree (1979) from Northeastern University. He is a member of IEEE and Tau Beta Pi.

**Kenneth J. Haduch** In 1974, Ken Haduch joined Digital after earning his Associate in Electronic and Computer Technology degree from the Electronic Institutes, Pittsburgh. He worked as a technician in Manufacturing on the PDP-11/70 and VAX-11/780 CPUs and in Engineering on the DR750 and FP750 designs. Ken helped to develop the C Box as a hardware designer on the VAX 8800 project. He is currently a hardware engineer in the Advanced VAX Development Group, working on the hardware design for a new VAX processor. Ken is also pursuing a B.S. degree from Northeastern University.

Michael S. Harvey Mike Harvey joined Digital in 1978 after receiving his B.S. degree in computer science from the University of Vermont. He worked on developing the RSX-11M and RSX-11M-PLUS operating systems and then led the team that developed the VAX-11 RSX layered product for the VMS system. Since joining the VMS Development Group, Mike has participated in new processor support for the VAX 8300 and 8800 systems, specializing in multiprocessing. As a principal software engineer, he is currently working on future directions for VMS multiprocessing and support for high-end VAX CPUs.

James P. Janetos Jim Janetos is currently studying computer architecture as a graduate student at Purdue University. He joined Digital in 1980 after receiving his B.S.E.E. degree (Summa Cum Laude) from the University of Michigan, where he was elected to Tau Beta Pi. As a design engineer, Jim worked on memory upgrades for the PDP-11/24 and 11/44 systems, on memory system designs, and on dynamic RAM evaluations. On the VAX 8800 project, he initially worked on the diagnostic software for the I/O adapter, the NBI. Later, he designed the NBIB module, one of the two modules in the NBI.

**Tracey L. Jones** Earning her B.S. degree in computer engineering from Boston University, Tracey Jones joined Digital after graduation in 1982. As a firmware engineer in the Advanced VAX Engineering Group, she wrote a major portion of the microcode that performs floating point operations in the VAX 8800 family of processors. After promotion to senior engineer, Tracey enrolled in Digital's Graduate Engineering Education Program and is now pursuing an M.S. degree in electrical engineering at Brown University.

James B. Keller Jim Keller is the project leader for the instruction-fetch and execution units, the I and E Boxes, and the console for a new VAX processor. On the VAX 8800 project, he worked on the design of the C Box. Prior to joining Digital in 1982, Jim worked on fiber optics and the designs of several microprocessor boards at Harris Corporation. He earned a B.S. degree in electrical engineering in 1980 from Pennsylvania State University, where he was elected to Eta Kappa Nu. Jim has applied for three patents on the technology in the VAX 8800 design.

**Michael W. Kement** Mike Kement is a senior design engineer in the Power System Technology Group, currently working on EMI and EMC. He was the design engineer for the power system on the VAX 8800 project. Mike has worked on the power systems of many products since joining Digital in 1974, including the LA36 and LA180 terminals, the PDP-11/44, VAX-11/780 and 11/750 systems, and the VAX 8600 CPU.

Andrew J. Matthews As a senior software manager in the Advanced VAX Systems CAD Group, Andy Matthews is currently automating the CAD to CAM transition. He has managed the development of surface-mount CAD processes and a pilot program of advanced CAD to CAM data methods. Andy designed the prototype and first release of VLS, the VAX layout software Digital uses for module design. He worked for Adage, Inc., as the manager of applications programming before coming to Digital in 1977. Andy holds a B.S. degree in C.S. and M.E. (1968) from Boston University. He has presented two papers at the Design Automation Conference.

Sudhindra N. Mishra Sudhin Mishra is a project leader in the Advanced VAX Development Group, currently developing a design verification CAD tool. As a principal engineer on the VAX 8800 project, he designed and implemented most of the I Box and originated the system-level simulation of the CPU. Before joining Digital in 1982, he was a senior research engineer at Prime Computers, Inc. Sudhin has worked on projects ranging from radar and heat-seeking missiles to computers. He earned a B.Sc. degree in engineering from Ranchi University and an S.M. in E.E. and C.S. from M.I.T. Sudhin has applied for a patent on the technology in the VAX 8800 design.

Kathleen D. Morse As a consulting software engineer, Kathy Morse is responsible for all low-end CPUs and peripherals. She is also one of the designers for future directions in VMS multiprocessing. Kathy provided VMS support for the VAX-11/782 and MicroVAX I and II systems, and the MA780 memory. She joined Digital after receiving her B.S.C.S. degree (1976) from Worcester Polytechnic Institute, where she also earned her M.S.C.S. degree (1985). Kathy is a member of IEEE, the Professional Council, ACM, Tau Beta Pi, and Upsilon Phi Epsilon. She has published in the Computer Measurement Group's Conference Proceedings, the *Digital Technical Journal*, and *DATAMATION*.

**Paul J. Natusch** As a principal hardware engineer, Paul Natusch is currently managing the hardware development for a new VAX processor in the Advanced VAX Development Group. On the VAX 8800 project, he was a member of the memory system team and later took over as its leader. Earlier, he worked on an upgrade to the VAX-11/750 memory controller, which expanded it from 2MB to 8MB. Paul joined Digital in 1980 from Storage Technology Corporation, where he was a diagnostic engineer. He received his B.S.E.E. degree from Cornell University in 1979 and an M.B.A. degree from Northeastern University in 1985.

**Kathleen L. Pratt** Educated at Rensselaer Polytechnic Institute, Kathy Pratt came to Digital after receiving her B.S. degree in computer and systems engineering in 1980. She worked on hardware designs for networks in the Local Area Networks Group, then on the design of the floating point hardware for the VAX 8800 central processor in the Advanced VAX Development Group. Kathy is currently a senior engineer working on the floating point design for a new VAX processor.

William A. Samaras Bill Samaras is a principal engineer working to design a new VAX processor. He joined Digital in 1982 to design the clock system on the VAX 8800 project. Formerly, at Accutest Corporation, Bill designed VLSI testers and timing systems. He holds an Associates degree (1973) from Northern Essex Community College, and B.S. degrees in engineering technology (1975) and electrical engineering (1976), both from Southeastern Massachusetts University. Bill teaches digital electronics for continuing education at the University of Lowell. He has applied jointly for a patent on the technology in the 8800 clock system.

**David C. Senerchia** Dave Senerchia is currently a senior engineer in the Electronic Storage Development Group. He is a member of the design team working on the main memory for a new mid-range VAX system. On the VAX 8800 team, Dave designed the initial array module for main memory and participated in the architecture and design of the memory system, the M Box. He joined Digital in 1982 after earning a B.S. degree in electrical engineering from Washington University.

**Paul C. Wade** As a principal engineer, Paul Wade is working on advanced development for future VAX CPUs. He was responsible for the electrical design, verification, and testing for the VAXBI bus. Paul also designed parts of the VAX 8200 system. Before joining Digital in 1980, he worked as a project engineer at Microwave Semiconductor Corporation, RCA, and Lockheed Electronics. Paul earned a B.S.E.E. degree (1973) from Newark College of Engineering. He holds a patent on gallium arsenide technology and has written nine papers on that topic. One paper won the Beatrice Winner Award at the 1980 ISSCC.

Cheryl A. Wiecek Cheryl Wiecek is the engineering manager of the Systems Architecture Group and is responsible for the VAX architecture and a number of Digital's interconnect architectures. She worked on VAX instruction-set characterization and performance simulation for the VAX 8800 CPU. Cheryl also worked on PDP-11 performance simulation after coming to Digital in 1978. She was a programmer/analyst at the Connecticut Education Association and taught mathematics in Connecticut. Cheryl holds a B.A. degree in mathematics (1974) and an M.S. degree in computer science (1979) from the University of Connecticut. She has published five papers on computer performance in ACM and IEEE journals.

Eugene L. Yu Gene Yu is a senior design engineer in the Workstation Engineering Group at Palo Alto. On the VAX 8800 project, he designed the memory system interface to the memory interconnect, the NMI. Before joining Digital in 1982, Gene worked at Prime Computer as a hardware designer on their 400 and 9900 systems, and at Data General Corporation on Nova products. He carned a B.S. degree in electrical engineering from the University of Massachusetts. Gene has applied for a patent as coinventor of the NMI and memory design for the VAX 8800 CPU.

John H.P. Zurawski John Zurawski is a consulting engineer working as the project leader for computer arithmetic in the Advanced VAX Development Group. He led the team that designed the floating point strategy and hardware for the VAX 8800 family. John joined Digital in 1982 from the University of Manchester, where he was a post-doctoral research associate. He holds a B.Sc. degree in physics (1976), and M.Sc. (1977) and Ph.D. (1980) degrees in computer science, all from the University of Manchester. A member of IEEE, John has published four papers on computer technology.

**Donald J. McInnis** *Group Manager, Advanced VAX Engineering*

Since the announcement of the VAX-11/780 system in November 1977, Digital Equipment Corporation has steadily expanded the VAX family with new VAX products: the VAX-11/750, VAX-11/730, MicroVAX I, VAX-11/725, VAX-11/ 785, VAX 8600, MicroVAX II, VAX 8650, VAX 8200, and VAX 8300 systems. The market acceptance of the VAX family has been excellent across almost all computing applications. This remarkable and steady increase in the use of VAX systems creates a continuous demand by the VAX customer base for enhanced products across all segments of the computing industry. In the fall of 1982, the development team for the 8800 project (known internally as "Nautilus") was assigned the responsibility of designing new systems to enhance the mid-to-high end of the VAX family.

This issue of the *Digital Technical Journal* represents a sampling of the types of design engineering that went into the VAX 8800 family. It takes an amazingly large number of different engineering disciplines to design and manufacture a product of this complexity. As time moves on, each successive development project seems to require a bigger investment in a larger number of disciplines to produce a product attractive to the marketplace. It is unfortunate that neither time nor space permits us to give proper visibility to all the design, manufacturing, and customer-service engineering efforts that led to the shipment of the VAX 8800 family.

The VAX 8800 family consists of four new processors: the VAX 8800, VAX 8700, VAX 8550, and VAX 8500 CPUs. The VAX 8800 family and the VAX 8200 system introduced a major new I/O bus, the VAXBI. We also introduced a completely new set of I/O adapters for the VAXBI bus, which will be the new foundation I/O channel for many future mid- to high-end VAX systems. The VAXBI bus will replace the UNIBUS on this class of system. The VAXBI offers a six-fold increase in performance and substantially better reliability and maintainability features in comparison to the UNIBUS.

The 8800 represents a significant advance into new areas of high-performance computing for the VAX family. A customer can replace a VAX-11/780 CPU with a VAX 8800 CPU in the same footprint and effect an order of magnitude increase in the amount of work done. The VAX 8500 CPU is really a replacement product for the VAX-11/785 CPU kernel. However, the 8500 has the same price, twice the performance, and one-third the footprint.

To produce a product that has a good price/performance ratio in the marketplace, you have to push hard on some dimensions of technology. A number of new pieces of technology were introduced on the VAX 8800 project, such as the 22-layer backplane and a 480-pin, zero insertion force connector. In the VLSI technology area, one 8800 includes a total of 186 emitter-coupled logic (ECL) gate arrays and a total of 28 custom-designed ECL parts.

The cycle time of a VAX CPU is a large determinant in its performance. The challenge of meeting a 45-nanosecond cycle time (versus 200 nanoseconds for the 11/780) required significant advancements in technology implementation and in CAD tools for analysis.

Enhancements were made to the base operating system software for the VAX 8800 processor. These software enhancements represent a basic technological change that is available to our customers. The VMS operating system was improved significantly to provide much better throughput for customers using the VAX 8800 dual processor as a general-purpose system. The ULTRIX-32 operating system was enhanced to support tightly coupled multiprocessing. Software

library structures were also developed for customers who might want to improve the throughput of a single job by decomposing it to run in parallel on the tightly coupled dual processors of an 8800.

To meet the performance goals, the overall design of the VAX 8800 system is necessarily quite complex and was potentially difficult to implement quickly and correctly. We understood this from the beginning of the project, based on our understanding of the experiences of previous projects (e.g., the VAX-11/750, VAX 8600, and J11 VLSI CPU chip projects). To manage that complexity in a timely manner, we selected some key strategies and stuck with them through the completion of the project. They proved to be very successful since the hardware prototypes were relatively error free, and the manufacturing start-up was very smooth and rapid. Some of these strategies are as follows:

- The project followed a structured design methodology that ensured the completion of comprehensive specifications before any detailed design was done.

- We made a large investment in our CAD team and in CAD tools to automate the design process.

- The basic design was managed by a chief architect.

- The system was simulated extensively before we built any hardware. (We finished the project with 14 VAX-11/780 and 11/785 systems in our cluster. During our peak simulation effort, however, over 30 dedicated VAX systems were used for a period of several months.)

- Since many different engineering and manufacturing locations were involved, we made extensive use of Digital's worldwide network for electronic mail and data exchange.

A more important factor than any of the above examples, however, was the people who worked on the project. We attempted to build an excellent team that worked well together. The attribute of teamwork and the willingness

of people to have a broad engineering focus proved to be invaluable, especially in the simulation and prototyping phases. The core management team started with very experienced people, most of whom had VAX-11/780 or VAX-11/750 development experience: Sas Durvasula, VAX 8500 project manager; John Hittell, manufacturing manager; Steve Jenkins, engineering manager; Nancy Kronenberg, VMS engineering; Bob Kusik, CAD manager; Steve Omand, customer service engineering; and Bob Stewart, chief architect. Many contributors at the next level also had similar backgrounds, and all remained in place for the duration of the project. This continuity was a major factor in completing a very successful project and a very successful family of products.

# An Overview of the Four Systems in the VAX 8800 Family

The VAX 8800 multiprocessor and the VAX 8700, 8550, and 8500 systems all derive from the same fundamental design. Their sustained applications throughput ranges from 3.0 to 12 times that of the VAX-11/780 system. In the design process, automated tools belped to correct design bugs early. ECL technology and a two-phase clock system achieve a 45-nanosecond cycle time. Microinstructions are processed simultaneously through four logic boxes that implement a five-stage pipeline. A high-speed memory interconnect, the NMI bus, links CPUs to memory and the I/O subsystem, which connects to VAXBI buses. Many reliability features, including extensive diagnostics, are implemented.

Design work on the VAX 8800 system began in September 1982 and concentrated on developing a balanced, high-performance system based upon the use of ECL components and multiprocessing. Although performance was the primary product goal, many technology, packaging, and implementation decisions reflected the equally pressing business requirements for reliability and ease of manufacturing.

The flexibility of the design ultimately spawned four CPU systems: the VAX 8800, VAX 8700, VAX 8550, and VAX 8500 models. These systems share many common functional and design attributes yet maintain noticeable implementation differences in the areas of performance, multiprocessing, expansion capability (memory and I/O), and packaging. As a result of these implementation variations, the sustained applications throughput (SAT) rates for these systems range from approximately 3.0 to 12 times the rate for a VAX-11/780 system. Sustained applications throughput is more indicative of usable performance for a given system than the more frequently reported peak numbers that can be derived from ideal or biased conditions. Table 1 compares the physical and performance attributes of these four VAX processor systems.

# Design Environment

Traditional design environments have placed the greatest emphasis on discovering and eliminating design errors in the physical hardware. The complexity of the VAX 8800 design coupled with the new technologies involved would have created costly delays in the development schedule had traditional approaches been used. Early in the project, goals were defined to identify logic design problems and to solve all timing problems through the use of extensive design verification tools.

A hierarchical design and simulation environment allowed the engineers to move freely throughout the design at any level from gates, layouts, and behavioral models through complete system simulation and timing verification. Considerable computing resources were required to allow that freedom. This environment, with its carefully managed libraries and databases, allowed this work to be done before any hardware was actually assembled.1 As a result, the design matured within our VAXcluster systems, evolving to hardware prototypes only after it was essentially complete and stable. In addition to the expected savings in prototype costs and a reduction in overall development time, the pervasive use of software tools significantly shifted the traditional debug effort to an earlier point in the design process. Cumulative bug-detection plots were used extensively to provide insight into the stability of the design.

The effect of this shift was to provide stable, early prototypes for extensive system characterization and testing, leading to earlier design

Table 1 CPU and Memory Attributes of the VAX 8800 Family

|                                   | VAX 8500                    | VAX 8550                    | VAX 8700                    | VAX 8800                       |

|-----------------------------------|-----------------------------|-----------------------------|-----------------------------|--------------------------------|

| CPU Attributes                    |                             |                             |                             |                                |

| SAT (compared to VAX-11/780)      | 3.5                         | 6.0                         | 6.0                         | 10.0 to 12.0                   |

| Cycle Time                        | 45 ns                       | 45 ns                       | 45 ns                       | 45 ns                          |

| Number of<br>Processors           | 1                           | 1                           | 1                           | 2                              |

| Upgrade<br>Potential              | To 8550                     | None                        | То 8800                     | None                           |

| Writable Control<br>Store (Words) | 15K                         | 15K                         | 15K                         | 15K in each CPU                |

| User Control<br>Store (Words)     | 1K                          | 1K                          | 1K                          | 1K in each CPU                 |

| Microword Size                    | 143 Bits                    | 143 Bits                    | 143 Bits                    | 143 Bits                       |

| CACHE Size                        | 64KB                        | 64KB                        | 64KB                        | 64KB (in each CPU)             |

| Internal Datapath                 | 32 Bits                     | 32 Bits                     | 32 Bits                     | 32 Bits                        |

| Instruction Buffer<br>Type        | 16 Byte<br>Look Ahead       | 16 Byte<br>Look Ahead       | 16 Byte<br>Look Ahead       | 16 Byte Look Ahead in each CPU |

| Maximum Total I/O Data Rate       | 16MB/s                      | 16MB/s                      | Over 30MB/s                 | Over 30MB/s                    |

| Maximum I/O<br>Channels           | 2                           | 2                           | 4                           | 4                              |

| Memory Attributes                 |                             |                             |                             |                                |

| Maximum Physical<br>Memory Size   | 80MB                        | 80MB                        | 128MB                       | 128MB                          |

| Cycle Times:                      |                             |                             |                             |                                |

| Hexword Read (256 bits)           | 495 ns min.<br>1260 ns max.    |

| Octaword Write<br>(128 bits)      | 270 ns min.<br>540 ns max.     |

| Longword Write (32 bits)          | 135 ns min.<br>495 ns max.     |

acceptance. This strictly controlled design environment allowed us to complete physical debug along with the required system evaluation and testing in only eight months.

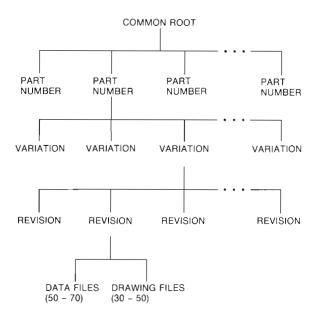

In a software-intensive design environment, the production of actual hardware is deferred somewhat in favor of design stability, resulting in a slightly longer soft-design period. The delay in hardware availability, however, is more than balanced by the stability of the hardware prototypes, which can then be accelerated through the evaluation and qualification-testing phases.

The design schedule recovers during these later phases, and substantial cost savings are realized because fewer engineering changes are made and stable manufacturing can begin quickly.

# CPU Design Overview

The VAX 8800 family of designs were structured around the functional elements, or "boxes," of the system. The CPU, memory, I/O, and bus subsystems were all matched to provide the necessary system balance. One simple model is to treat performance as a function of two variables:

the instruction execution rate, and the amount of "work" each instruction can perform. The design of the VAX 8800 family focused on what we call the "short tick" approach to achieve the necessary, sustained performance.

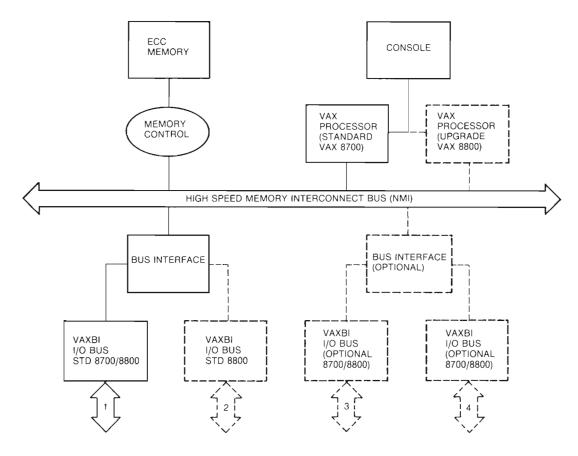

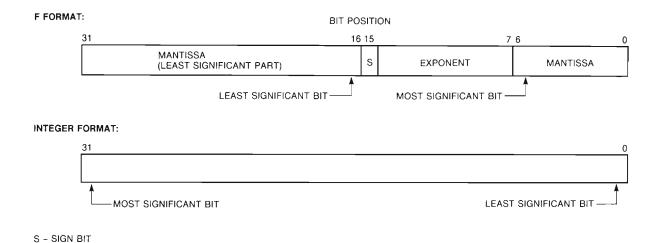

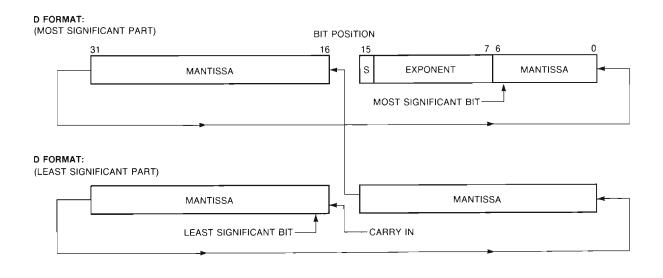

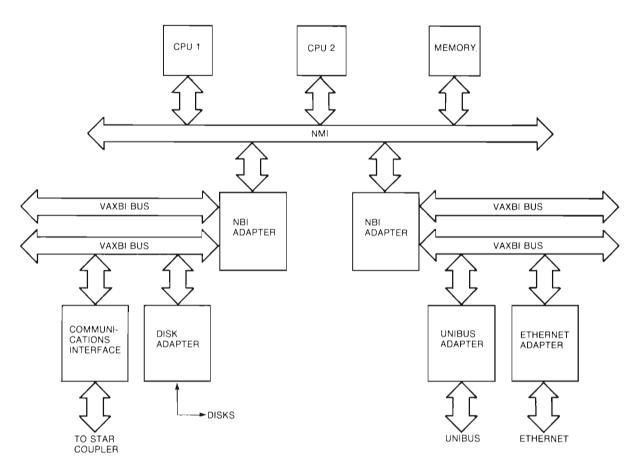

In this approach, the instruction and data streams are kept simple and are executed quickly. Any design trade-offs were resolved in favor of speed and simplicity, thus reducing design complexity. The use of high-speed custom and semicustom VLSI components combined with several new internal bus architectures resulted in a family of processors with a 45-nanosecond (ns) cycle time. All models employ a five-stage instruction execution pipeline, integral floating point acceleration (F, D, G, H formats), and the VAXBI bus as the primary I/O subsystem. The extensive use of microcode controls with minimal hardware assist augments current performance while providing flexibility for future enhancements. The block diagram in Figure 1 (using the VAX

8700 and VAX 8800 systems) illustrates the key functional elements common to the VAX 8800 family design.

# **Technology**

The raw speed, off-chip drive capabilities, and availability of bipolar emitter-coupled logic (ECL) logic components provided the most straightforward means of achieving the desired performance of the VAX 8800 family. Most logic is implemented in 1200-gate ECL arrays. Custom logic chips designed by Digital provide further performance gains for floating point operations and general-purpose registers. The cache is implemented in 10-ns and 15-ns ECL RAMs. Nine-layer, controlled-impedance CPU logic modules and a 22-layer, controlled-impedance CPU backplane were developed to meet the signal-integrity and signal-propagation requirements crucial to an ECL design. Other multilayer backplanes were designed for the private memory array bus and I/O subsystems.

Figure 1 VAX 8700/8800 Block Diagram

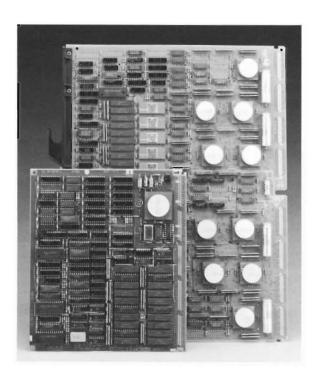

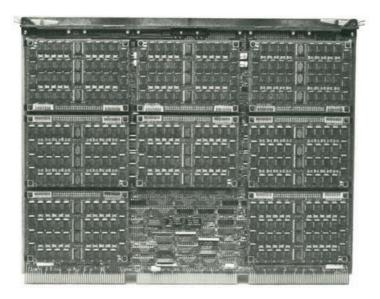

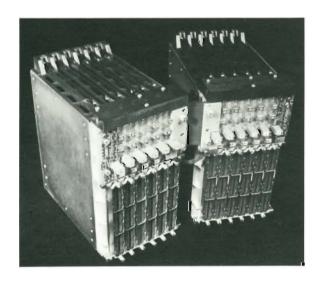

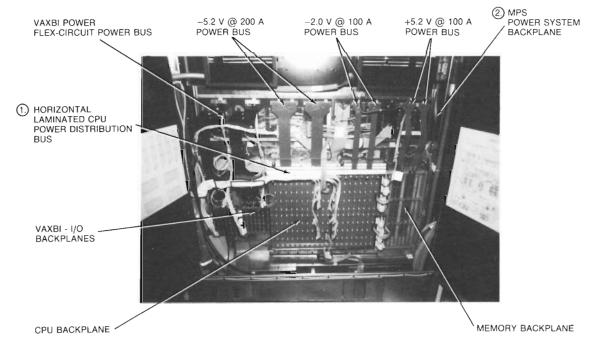

An innovative scheme of bus bars and ribbon straps routes the appropriate power to each of the backplanes, minimizing cable management problems for system power. The eight CPU logic modules, all memory arrays, and all I/O controllers attach to their respective backplanes by means of zero insertion force (ZIF) connectors, which improve our ability to manufacture and service the system. Figure 2 shows the two different module types (CPU and VAXBI) used in the VAX 8800 family.

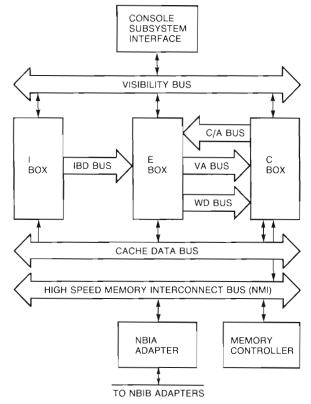

formed within each processor. There are four logical boxes: the instruction unit (I Box), the cache (C Box), the execution unit (E Box), and the memory subsystem (M Box). Each processor contains these functional units and their related buses. Five buses are implemented within each CPU: the cache/ALU bypass bus, the cache data bus, the instruction-buffer data bus, the virtual-address bus, and the write data bus. Figure 3 is a block diagram of the processor configuration.

Figure 2 Typical CPU and I/O Modules

An extensive environmental monitoring subsystem, called the EMM, has been implemented throughout the system. The EMM constantly monitors current fluctuations, air flows, and temperature variations, providing warnings at the system console. The EMM can automatically power down the system in the event that safe operating limits are violated.

## CPU Subsystems

The designs of the CPUs in the VAX 8800 family are partitioned along the logical functions per-

C/A BUS - CACHE/ALU BYPASS BUS IBD BUS - INSTRUCTION BUFFER DATA BUS VA BUS - VIRTUAL ADDRESS BUS WD BUS - WRITE DATA BUS

Figure 3 Processor Block Diagram

A short overview of each functional box follows. Other papers in this issue of the *Digital Technical Journal* and the *VAX Hardware Handbook* contain substantially more detail.<sup>2</sup>

# Pipelining the VAX 8800 Family

Pipelining, which functionally involves the E Box, the C Box, and the M Box, is primarily controlled by the I Box. Pipelining is a proven method to improve performance. The incorporation of pipelining, in conjunction with faster microcode instruction execution rates, or cycle times, increases aggregate throughput more than can be achieved by improvements of the cycle time alone. The concept of pipelining is based upon partitioning instruction execution to allow simultaneous operations upon multiple microinstructions. The VAX 8800 family employs a five-stage pipeline. In this design a new microinstruction executes every 45 ns. with five microinstructions executing simultaneously. A simplified schematic of the VAX 8800 family pipeline is represented in Figure 4.

| DNA | CS  | R   | Α   | W,C |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|     | DNA | CS  | R   | Α   | W,C |     | _   |     |

|     |     | DNA | CS  | R   | Α   | W,C |     |     |

|     |     |     | DNA | CS  | R   | Α   | W,C |     |

|     |     |     |     | DNA | CS  | R   | Α   | W,C |

DNA - DECODE/NEXT ADDRESS

CS - CONTROL STORE LOOK-UP (MICROCODE INSTRUCTION)

R - REGISTER READ

- ALU OPERATION

W,C - REGISTER WRITE, CACHE OPERATION

The Pipeline in the VAX 8800 Figure 4 Family

#### The I Box

The I Box contains the microcode store and control center and performs five primary functions.

- Buffering the prefetched VAX instructionstream data received from the cache

- Decoding and controlling the execution of microinstructions

- Monitoring and servicing microtraps, interrupts, and exceptions

- Supplying instruction-stream embedded data

- Interfacing between the console interface module and the processor

For each processor, a writable control store of 16K words by 143 bits is loaded directly from the intelligent console subsystem upon system

start. A segment of control store with 1K words by 143 bits, the user-writable control store, is provided for the system user to optimize applications. The logical function of the I Box includes the following:

- The instruction buffer

- The instruction decoder

- The microsequencer

- The condition code and microbranch logic

- The interrupt and processor-register logic

- The file-address generator

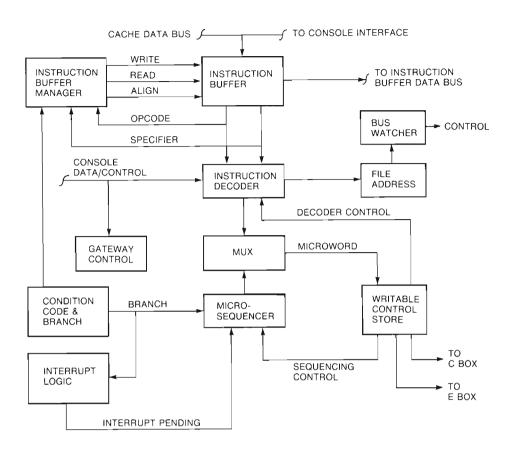

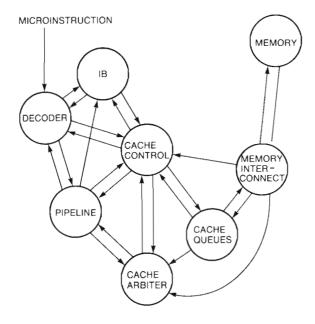

Figure 5 depicts the implementation of the I Box.

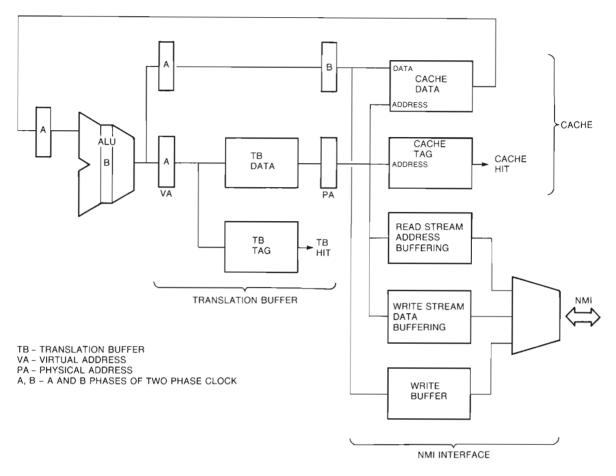

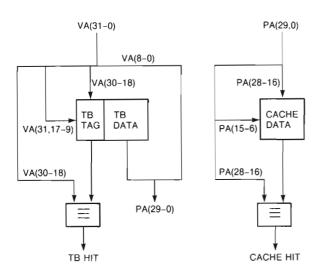

#### The C Box

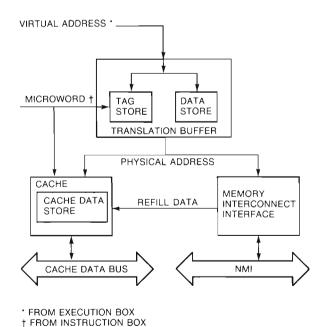

The C Box for each processor is built around a 64-kilobyte (KB) write-through data cache memory that is physically indexed and direct mapped. Functionally, the C Box provides very high-speed physical memory, high-speed address translations, and a communication path for the processor to the NMI bus. The comparatively large cache size was specifically selected to allow large applications to remain fully resident in the cache, substantially reducing memory traffic and processor wait states. The complete C Box implementation includes a 1KB translation buffer, a 64KB cache data store, and an NMI interface. The translation buffer consists of a 1K-entry cache of virtual-to-physical address translations. This translation buffer contains a tag store and a data store organized into 512 process-translation slots and 512 system region-translation slots. Using a portion of the virtual address to compare the tag-store and data-store addresses, the translation buffer concatenates the page frame number with the loworder virtual-address bits to form the physical address for the data store cache.

Data read from the cache data store (a cache "hit") requires no memory request. If the required data is not in the cache data store (a cache "miss"), logic embedded in the NMI interface uses the cache-miss address to spawn a command/address transaction that is sent to the memory subsystem. Upon return, the requested data from memory is passed to the requesting CPU and then placed in the cache data store for subsequent use. This design allows the translation

Figure 5 | I Box Block Diagram

Figure 6 C Box Block Diagram

buffer and the cache data store to be free to process other processor requests until the requested data arrives from memory.

A block diagram of the C Box is shown in Figure 6.

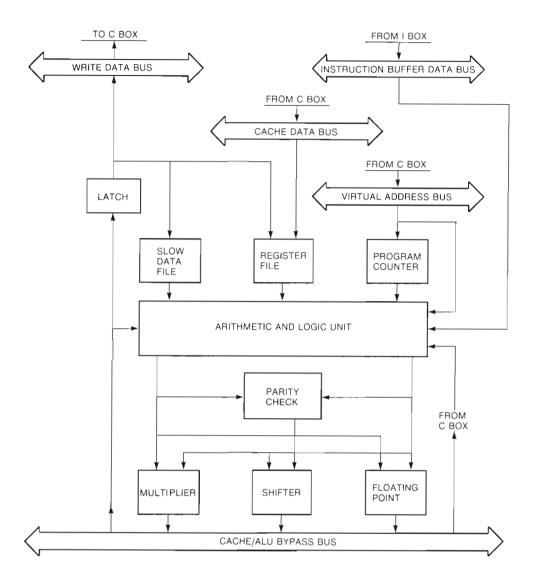

### The E Box

The E Box receives data from the I Box and the C Box, processes that data, and returns it to the C Box. The E Box performs five primary functions required by the processor.

- Handles all arithmetic, logical and bit-shift operations

- Maintains the program counter and general registers

- Maintains the processor registers

- Controls data transfers between the C Box, the I Box, and the clock-module registers

- Provides condition-code information to the I Box microsequencer

Figure 7 E Box Block Diagram

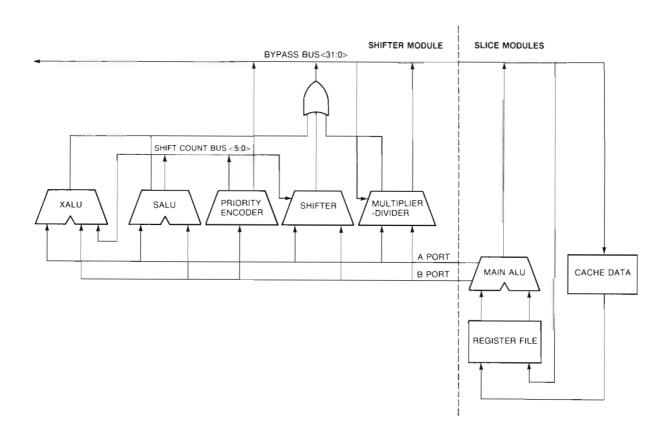

The major elements of the E Box, located physically on the data-slice modules and the shifter module, consist of a register file, a data file, the program-counter logic, the main ALU, and a shifter. The logic of the E Box includes integral floating point operations that are optimized and a 64-bit multiplier (implemented in custom-designed VLSI chips) that augments the speed of both integer and floating point multiplication. Figure 7 is a block diagram of the E Box.

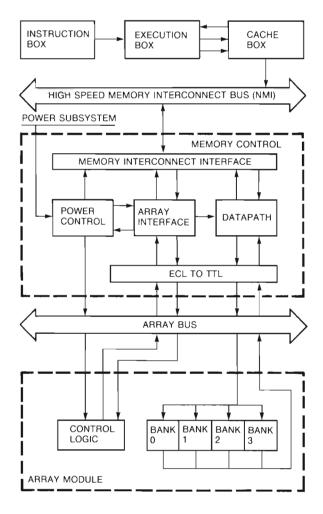

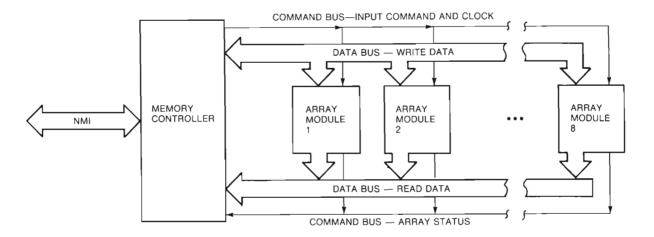

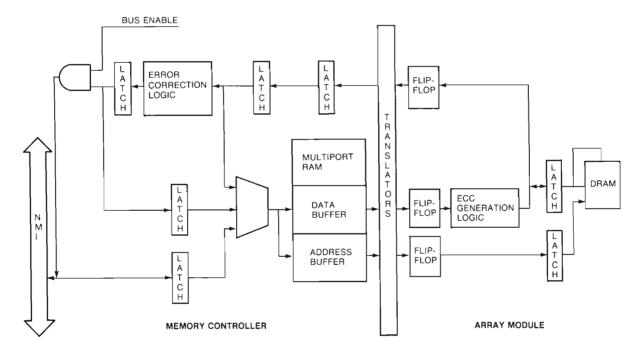

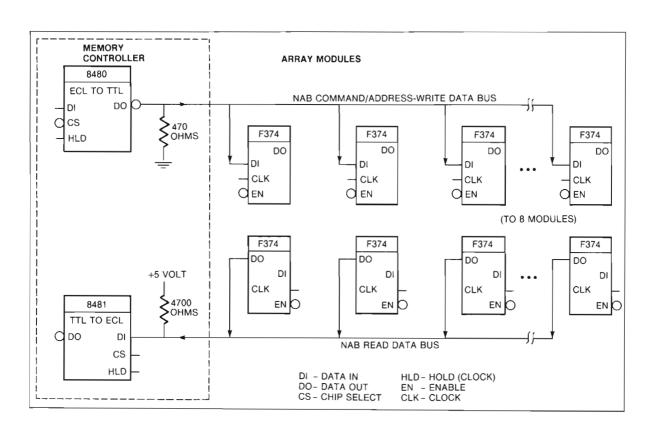

#### The M Box

The M Box, the memory subsystem, consists of memory control logic, memory arrays, and a dedicated memory array bus that provides a usable data rate of over 50MB per second to the memory subsystem. The control logic optimizes multiple memory read and write operations, implements three-way interleaving, and buffers memory transactions for optimum data movement. The dedicated memory array bus, coupled

with the memory control logic, effectively offloads the NMI bus, providing balanced bus access and loads. The interleaving algorithms are based upon array boundaries, making the memory control logic technology independent. The result is that as increasingly dense memory arrays become available, few if any controller modifications will be required.

The error checking and control (ECC) is built around 7 check bits for every 32 bits of data. This protocol provides automatic single-bit correction and double-bit detection.

In the VAX 8800 multiprocessor, all memory is fully sharable. Current systems in the VAX 8800 family are offered with 16MB per memory array, giving the VAX 8700 and VAX 8800 systems a maximum memory capacity of 128MB, and the VAX 8500 and VAX 8550 systems a maximum of 80MB. Figure 8 is a block diagram of the M Box.

Figure 8 M Box Block Diagram

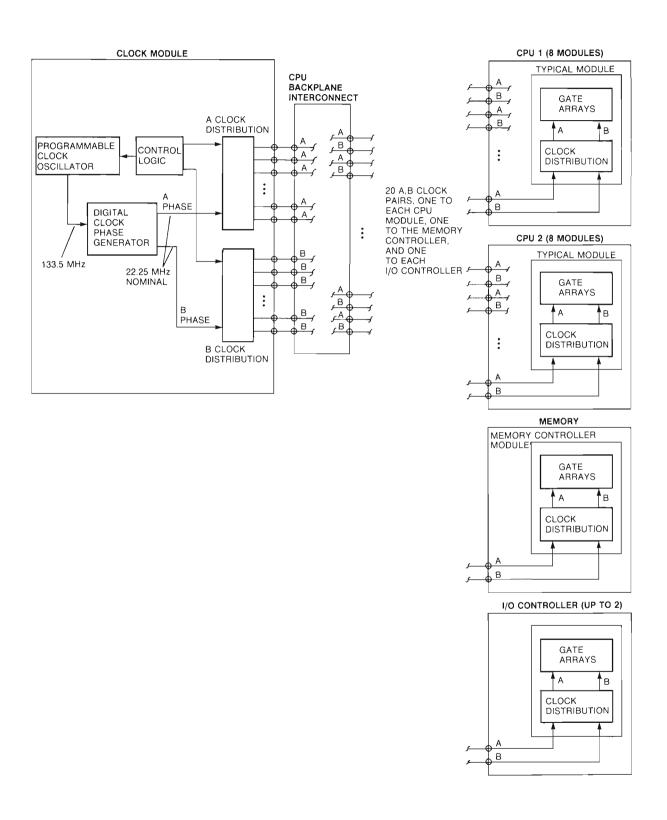

# The Clock Subsystem

The clock subsystem generates, controls, and distributes timing signals to all the components of the processor system. The clock subsystem contains the console interface, an oscillator, a phase generator, clock-control logic circuits, and the logic circuits for clock signal distribution.

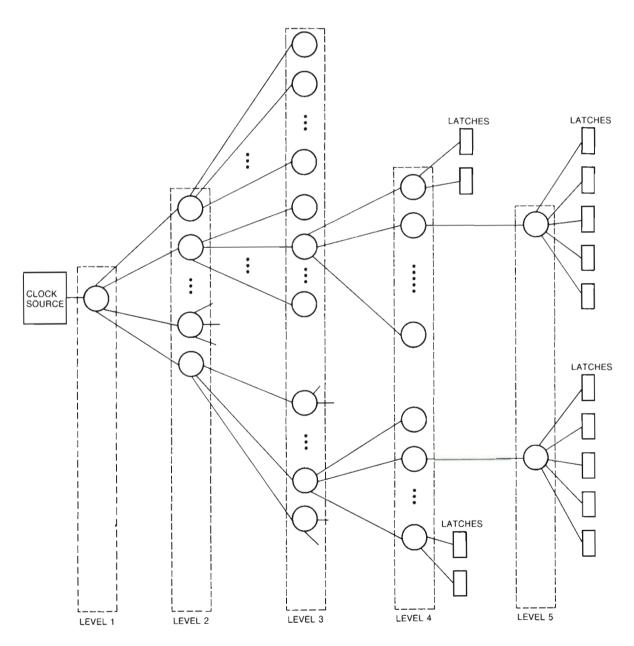

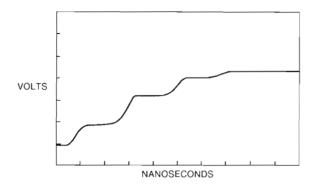

The VAX 8800 family implements a two-phase, nonoverlapped clock subsystem operating at a cycle time of 45 ns. A stable, high-frequency oscillator (120 MHz nominal with variable output), coupled with a phase generator, provides the signal. The implementation of a two-phase design with matched signal-length distribution throughout the CPU is most efficient for the pipelined, latch-based design of the VAX 8800 family. This design avoids the inefficiencies associated with the compressed signal-assertion times resulting from approaches that specify minimum delays for given logic elements.

A-clock and B-clock signals are distributed to alternate latches in a given logic stream. All data transfers occur between latches clocked by different phases to assure a race-free design. The essence of fast-processor design is managing and controlling skew. In this regard, signal propagation and distribution presented significant challenges in the areas of controlled etch lengths, controlled impedance, routing, and placement. To assure a stable, reliable design, all design activity was predicated on worst-case design rules rather than using the typical-case limits.

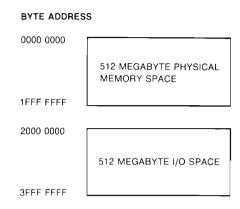

#### The NMI Bus

Integral to the design of this family of processors was the development of a high-speed memory interconnect bus called the NMI bus. This bus, analogous to the synchronous backplane interconnect (SBI bus) in the VAX-11/780 CPU, links the subsystems for CPU logic, central memory, and I/O. The NMI bus is a 32-bit synchronous bus, physically implemented within the 22-layer backplane. This bus provides the control and datapath functions as well as the distribution of clock signals for the VAX 8800 family.

One fundamental problem in the design of high-performance systems revolves around balancing the bus access needed at any given instant with the raw bandwidth available. To provide the correct balance, the NMI bus was implemented as a pended (vs. interlocked) bus, resulting in very high bus-access availability.

Since memory is the critical resource in sustained operations, the NMI bus uses a modified round-robin arbitration that gives the memory a higher priority when there is contention for the bus. This arbitration priority eliminates any lock-step conditions and also provides for recovery of states and data in the event of preemption. This high bus-access capability, coupled with usable data rates of up to 60MB per second, provides the necessary balance to support CPU, memory, and I/O transactions. The inclusion of write buffers within each CPU, coupled with the large cache size, effectively reduces the number of transactions presented to the bus. Measurements on a VAX 8800 system in our Engineering VAXcluster environment have indicated that the NMI bus is rarely busy more than 50 percent of the time; the CPUs use approximately 25 percent of the available access time and bandwidth. Other applications may see somewhat different ratios.

#### VAXBI Bus

The VAX 8800 family uses the VAX bus interconnect, called the VAXBI bus, for the I/O subsystem in order to provide adequate balance for the CPU performance. The VAXBI bus, a 32-bit clocked bus with distributed arbitration, is capable of usable data rates in the VAX 8800 family up to 8MB per second, depending upon word size and application. Custom logic on each interface module provides all bus protocols, as well as integral data-integrity features, including master transmit and command acknowledge.

The VAX 8800 and VAX 8700 systems can be configured with up to four VAXBI channels, whereas the VAX 8550 and VAX 8500 systems accept up to two. Therefore, fully configured VAX 8800 and VAX 8700 systems can support aggregate I/O bandwidths up to 30MB per second. Similarly, fully configured VAX 8550 and VAX 8500 systems can support aggregate bandwidths up to 16MB per second. Each VAXBI bus can support up to 16 nodes, or logical addresses, which connect to any combination of networks, intelligent and nonintelligent devices, DMA devices, and VAXcluster systems, as well as providing for connection to existing UNIBUS-based devices.

All of Digital's network protocols interface directly to the VAXBI on the VAX 8800 family. Thus, VAXcluster, Ethernet, DECnet and DSA

(Digital Storage Architecture) devices are all ported directly to this high-performance I/O subsystem.

#### Reliability

Reliability was one of the primary goals of the VAX 8800 design. Numerous features were implemented that more than doubled the basic computing kernel availability compared to the VAX-11/780 system. Some of the key functions include

- Environmental and power monitors that query the system and maintain safe system operating levels

- Automatic verification of hardware, firmware, and software revision compatibility

- Electrically keyed modules and module slots that prevent improper installation and damage to the modules or the system

- Automatic electrostatic discharge (ESD) protection of modules during installation and removal

- ECC on main memory

- Parity checking on internal RAMs

- Bus protocol checking for the memory interconnect

- Timing and voltage margining

- Remote diagnostics capability

- Dual-to-single processor reconfiguration (VAX 8800 system only)

#### Diagnostic Development

Similar to the hardware development, the design methodology for the diagnostics depended very heavily on simulation. Almost all the diagnostic tests were debugged on behavioral and structural models of the design before the initial prototype was powered up. There were three major benefits of this methodology.

- Microdiagnostic and macrodiagnostic tests were useful for design verification testing.

- 2. Test vectors for automatic test equipment (module test) were extracted from the simulation database.

- 3. A comprehensive diagnostic package was available shortly after the prototype was powered up.

The diagnostic for the VAX 8800 family consists of tests specific to this processor and generic to the VAX architecture. The processor is tested primarily with microdiagnostics. These tests execute from the processor's writable control store and are governed by the console.

VAX generic diagnostics are included to test the UNIBUS and VAXBI adapters and options. All the diagnostic code fits on the console's Winchester disk. When the system is powered up, a subset of the microdiagnostic tests are executed.

# **Balanced Systems**

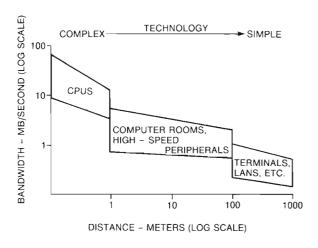

The VAX 8800 design effort delivered four different systems, the 8800, the 8700, the 8550, and the 8500, all reflecting the overriding concept of balanced system design. While the CPUs themselves demonstrate excellent internal balance between their logical and functional subsystems, they are also balanced members of the extended system that can span much larger physical distances. Monolithic or isolated computing resources are no longer capable of accessing, manipulating, and distributing the volumes of information needed for complex or extended solutions. In this light, the VAX 8800 family should be viewed in the context of a balanced network. The movement of data is governed by speed and distance. An inverse relationship exists as shown in Figure 9. The VAX 8800 family fits on the top bound of the bandwidth range throughout the distance function.

Figure 9 Bandwidth versus Distance

# Summary

The VAX 8800 family of products merges fast instruction-execution rates, large physical memories, large high-speed data caches, VAXBI I/O channels, pipelining, and balanced internal-bus architectures to provide high system-applications throughput. Spanning an applications throughput range that is from 3 to 12 times that of the VAX-11/780 system, the VAX 8500, VAX 8550, VAX 8700, and VAX 8800 systems are matched to the network and applications strategies offered by Digital Equipment Corporation.

# References

- D. Bak, "The Impact of VAX 8800 Design Methodology on CAD Development," Digital Technical Journal (February 1987, this issue): 129–135.

- 2. VAX Hardware Handbook (Maynard: Digital Equipment Corporation, Order No. EB-21710-20, 1982).

# The VAX 8800 Microarchitecture

The VAX 8800 processor has a simple but efficient microarchitecture. Its pipelined micromachine has a one-cycle next-address loop and four-cycle latencies for both microbranches and microtraps. Instruction prefetch and decode are done in parallel with microcode execution. The instruction buffer is a bit-sliced, four-longword circular queue. The decoder is primarily a RAM-based table. For special events, hardwired logic is used for decoding. A bit-sliced microsequencer provides up to 32-way conditional microbranching, using a collection of about 80 branch conditions. A hardware microstack provides up to 15 levels of nested subroutine calls and returns. Microtrap conditions are prioritized over 16 levels, and microtraps are chained, not nested.

The term "microarchitecture" means the specification or description of the interrelationships between the parts of the micromachine that implements the instruction set processor. In terms of this definition, the microarchitecture of the VAX 8800 processor will be described by elucidating the organization of its micromachine and the interaction between its components.

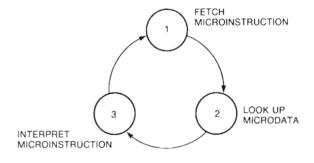

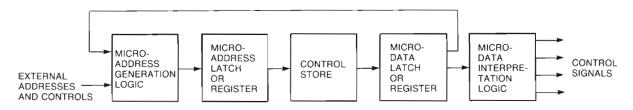

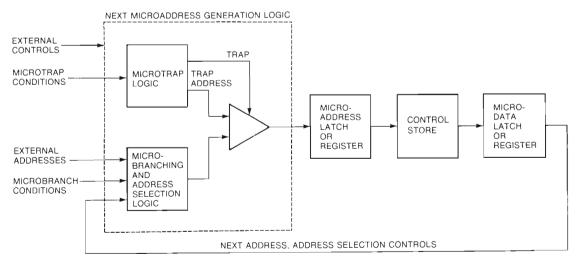

Figure 1 shows a simple three-stage statemachine model of an abstract micromachine appropriate for implementing the control unit of a typical von Neumann processor. Figure 2 shows a block diagram depicting the essential elements of such a micromachine. This statemachine is capable of executing microcode routines to implement an instruction set processor. In such a system, every macroinstruction is decoded by the hardware to produce the starting addresses of a small set of microprograms, which execute sequentially to produce the desired effect. Barring some exceptions, a microprogram or microcode routine can execute rather independently in the sense that each microinstruction produces the address of the next microinstruction. The last microinstruction causes the selection of an external address, such as one produced by the decoder, to start the execution of another routine.

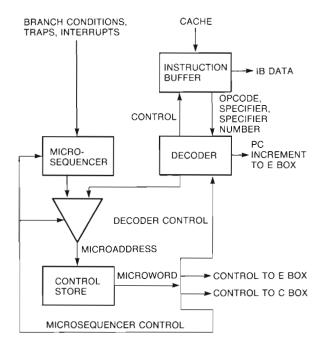

In Digital's vernacular, the I Box is the logical partition containing the instruction-processing hardware. Figure 3 shows a block diagram of the VAX 8800 I Box with the basic elements of its micromachine.

Figure 1 State-machine Model of an Abstract Micromachine

From the early IBM and CDC computers to the modern CRAY machines, computer designers have used a technique called "pipelining" to obtain higher performance. Pipelining overlaps the execution of instructions in time; that is, several instructions can be executing at the same time. This technique provides a higher throughput when the pipeline is fully loaded, but there is a cost involved. If the pipeline is broken, extra processing is required to refill it. Moreover, if any active instructions have partially executed, information about their states may have to be saved to continue processing after an abrupt interruption.

The degree of pipelining varies from one machine to another depending upon the design choices and trade-offs made by the system architects. A metaphor often used to indicate the degree of pipelining is the length of the pipeline

Figure 2 Block Diagram of an Abstract Micromachine

Figure 3 VAX 8800 I Box

stated as the number of stages, for example, a three-stage pipeline or a four-stage pipeline. The number of stages conveys the extent of time overlap for typical operations in a computer. In a machine with a pipelined microarchitecture, these operations are executions of microinstructions. A higher degree of pipelining makes short cycle times possible, thus leading to a higher throughput when the pipeline is fully loaded. But longer pipelines entail increased overhead in terms of their ability to resume operations after a break in the pipeline caused by any abnormal event. Therefore, an architect's goal is to design the system so that the pipeline remains loaded most of the time and recovery from a broken pipeline is not too inefficient. The VAX 8800 CPU is a prime example of a processor with a pipelined microarchitecture.

# **System Considerations**

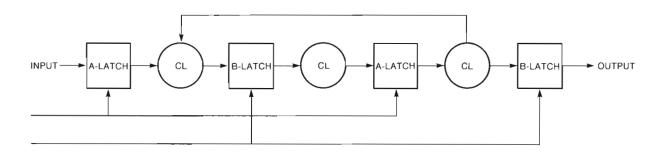

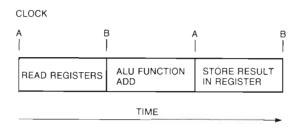

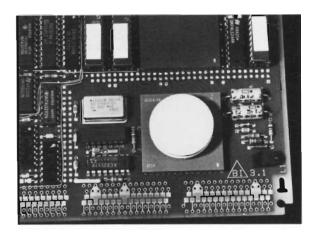

The design philosophy of the VAX 8800 processor was to optimize the hardware so that it would execute the microcode efficiently. A large control store (144 bits by 16,000 entries) holds the entire microcode. Using fairly generalized datapaths, the microcode executes the logic of the instructions. However, special hardware is used to speed up performance in critical areas. The processor logic is primarily designed with latches, which are clocked with a globally distributed, two-phase, nonoverlapping clocking scheme. The two clock phases are called the A-clock and the B-clock. A typical example of logic design, based on the above approach, is shown in Figure 4.

Figure 4 A Typical Section of the VAX 8800

CL - COMBINATORIAL LOGIC

It is apparent from Figure 4 that the data flow in such a logic system occurs through the perpetual data transfers between the latches connected to the A-clock and those connected to the B-clock. Each data transfer may be considered atomic in the sense of hardware operation. A microoperation may be envisioned as a logical operation that is atomic in terms of the execution of a microinstruction, such as a register read, a register write or an ALU function. Hence a microoperation constitutes one or more data transfers, and the microinstruction execution simply constitutes a time sequence of microoperations, as shown in Figure 5.

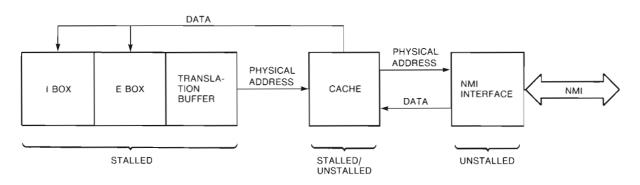

Figure 5 Example of a Microinstruction

In high-performance machines, like those in the VAX family, there is usually a mismatch between CPU cycle times and memory-access times. For example, consider an ADD instruction. If the operands are in registers, the ADD can be done rather quickly. But if one of the operands has to be read out of memory, the ADD cannot be performed until the desired data arrives from memory. Most VAX processors have a fast cache memory, tightly bound to the processor's arithmetic units, to alleviate the memory-latency problem. In the case of a cache miss on a required datum, however, the only alternative for a von Neumann processor is to wait. A processor in such a state is said to be "stalled." Under such conditions, the state of the processor must be "frozen" until the cause of the stall no longer persists and the stall is broken. The two-phase clocking scheme provides a convenient way to implement stalls, in which one of the clock phases (the A-clock in the 8800) may be blocked. Stalls are controlled by the cache through a special hardware signal distributed globally to block the A-clock. Thus, the processor logic contains two flavors of A-latches:

Stalled A-latches, which are affected by a stall

Unstalled A-latches, which are not affected by a stall

The micromachine is implemented only with stalled A-latches. Hence the effect of stalls on the execution of the micromachine is largely transparent.

A mechanism is also required to deal with hardware exceptions when the results of the execution of a microinstruction have to be undone. In a pipelined microarchitecture, several microinstructions may have partially executed when an exception condition is detected. In that case it is necessary to undo the effects of all those microinstructions. The most common technique used to deal with such situations is called a microtrap. Since microtraps relate closely to the micromachine execution, every processor has its own scheme to implement them. In every case, however, microtraps must permit the "roll back" of some number of microinstructions because the detection of a trap condition usually occurs quite late with respect to microinstruction execution.

In the VAX 8800 processor, microtraps are implemented so that the offending microinstruction is allowed to complete, but subsequent microinstructions in the pipeline are blocked. Since the offending microinstruction may have caused some undesirable results, the trap-handler microcode must fix the problem. Depending on the particular situation, either the microinstruction execution flow is resumed from the blocked state or a new flow is originated.

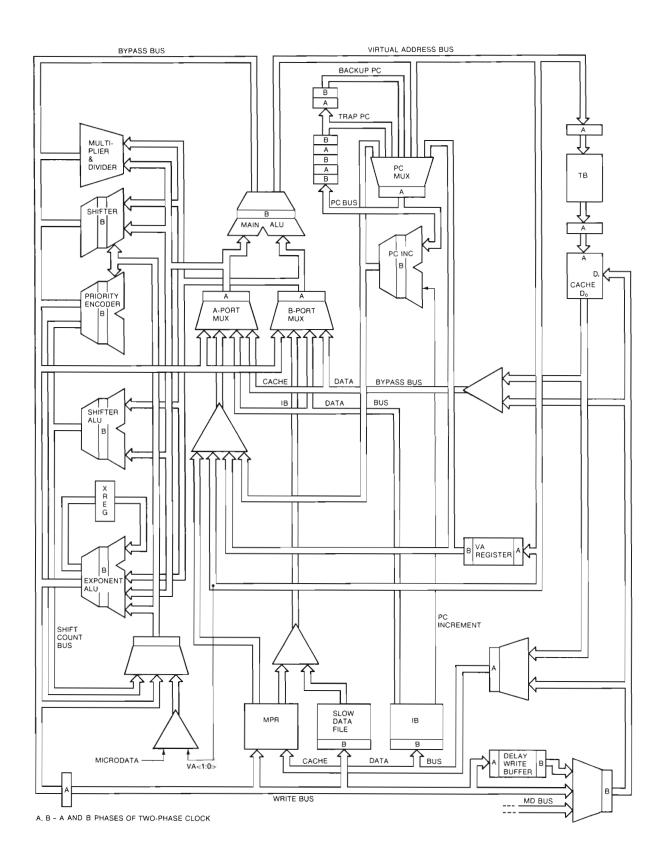

#### System Buses and Datapath

Figure 6 is a block diagram of the VAX 8800 CPU datapath, showing all the major buses. The hardware organization of the CPU provides a two-cycle operation between the cache and the ALU, as shown. The processor has several functional units in addition to the main ALU. These additional units perform high-speed multiply and divide, shifting, and floating-point arithmetic operations.

There are several possibilities for selecting inputs to these functional units. For operations involving two inputs, both can be presented simultaneously onto the two legs of the main ALU as well as most other functional units. The results from these functional units are sent on the W bus for writing to either the multiport

Figure 6 VAX 8800 Datapath

register file (MPR) or the cache. However, since the write actually occurs in the following cycle, the bypass bus provides a shortcut (saving a cycle) in case the write datum is read by the very next microinstruction.

The virtual address bus carries the virtual address of any data-stream (d-stream) references, whereas the program-counter bus has the current program counter (PC). The instruction-buffer data bus provides the instruction-stream (i-stream) data. The instructions and data from the cache are returned on the cache data bus. However, a cache data bypass bus provides a direct path to the functional units for the data returned by the cache, in case the processor is or will be stalled for that data.

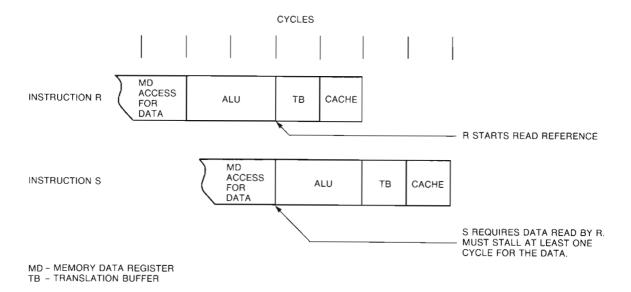

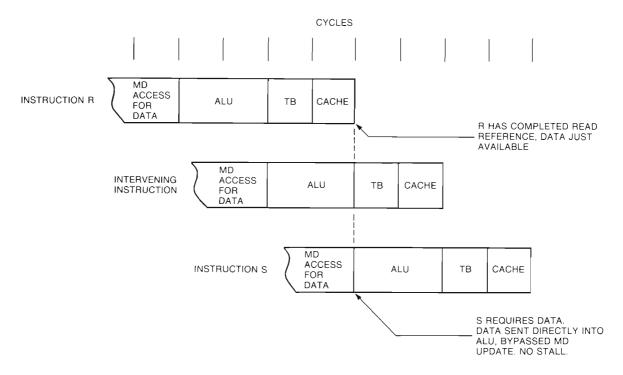

# Microinstruction Pipeline

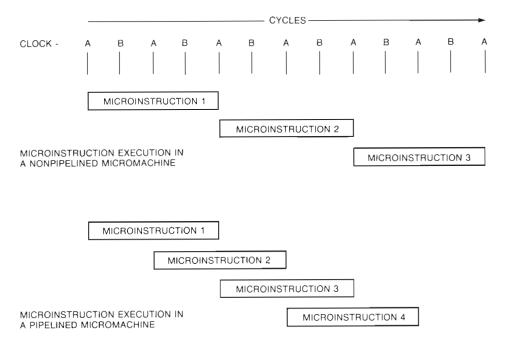

The top part of Figure 7 shows the execution of microinstructions as a function of time in a non-pipelined microarchitecture; the bottom depicts that in a pipelined microarchitecture.

The basic data flow in a processor occurs in the following sequence:

- 1. Read the register operands into a functional unit, such as the ALU.

- 2. Perform some ALU function.

- 3. Write the results into the destination register.

- 4. If there is a cache, start a cache operation at approximately the same time as a register write since memory references are buffered through special-purpose memory data registers (MDRs or MDs) in most high-performance processors.

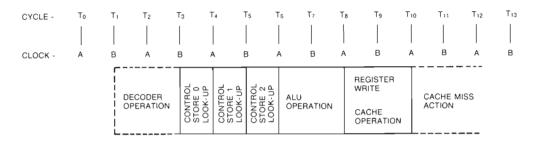

Figure 5 shows that the sequence above occurs in a natural order in time as a consequence of the microinstruction execution. With pipelined microarchitectures, a time reference is needed to correlate the microoperations performed by various microinstructions with respect to each other. The notion of canonical times is very convenient for this purpose. The clock ticks of the reference microinstruction may be labeled with a monotonically increasing set of T numbers starting at To as shown in Figure 8. These T numbers are called the canonical times of a particular microinstruction. The microoperation labeled T<sub>0</sub> marks the start of a microinstruction execution cycle. Figure 8 shows the basic microoperations of a VAX 8800 microinstruction with their canonical times.

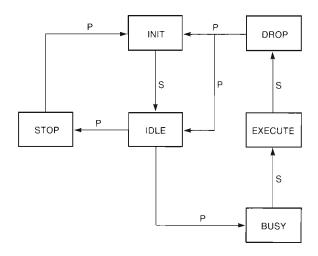

We shall use the simple model of a micromachine in Figure 1 to describe the VAX 8800 micro-

Figure 7 Microinstruction Execution

Figure 8 Canonical Times of a VAX 8800 Microinstruction

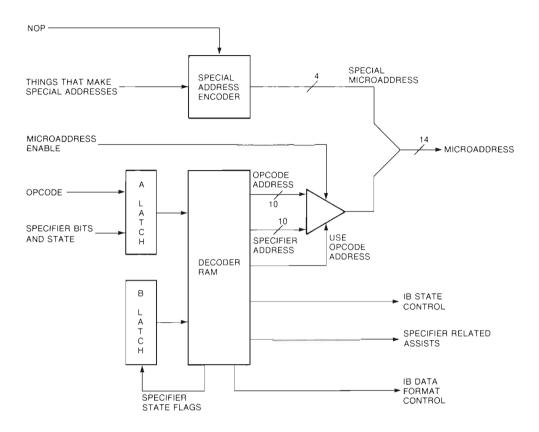

instruction format as a sequence of basic microoperations like those in Figure 8. The first stage in the microinstruction execution cycle is the microaddress fetch. The microinstruction execution cycle begins with a decoder operation. The decoder produces the starting microaddress for every new microinstruction sequence and presents it to the microsequencer. The decoder determines that address on the basis of the contents and current state of the instruction buffer (IB). Each microinstruction specifies to the microsequencer whether or not to accept the decoder's microaddress. If not, the microinstruction must either specify the address of the next microinstruction directly, as a part of the microword, or indicate an alternate source for the address within the microsequencer. Since the decoder's operation is concurrent with the microsequencer's, the decoder always has a starting microaddress for the microsequencer. It is convenient to think of this IB-decoder concurrency as a "hidden decoder cycle."

The next stage in the microinstruction execution sequence is the fetch of the microinstruction, performed by a look-up in the control store. In the VAX 8800 system, the microaddress is pipelined, not the microdata. Consequently, the microdata from a segmented control store appears at the appropriate time for the three basic operations to occur in the indicated order.

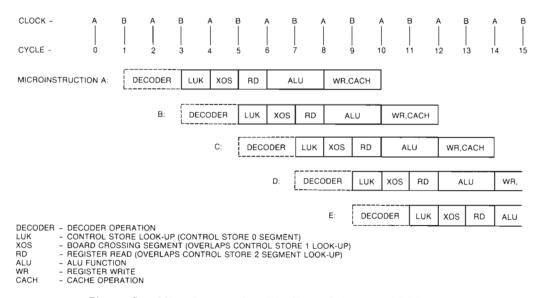

The microdata looked up causes a sequence in which the register read occurs between the times  $T_5$  and  $T_6$ , the ALU function between  $T_6$  and  $T_8$ , and the register write between  $T_8$  and  $T_{10}$ . The cache operations also occur between the times  $T_8$  and  $T_{10}$ . The section beyond  $T_{10}$  denotes cache activity with respect to the memory if there is a cache miss. (The cache/memory interface is controlled by an independent micromachine.) During every cycle, a microinstruction produces the address of the next microinstruction, which is then executed. Figure 9 depicts the generic microinstruction pipeline of the VAX 8800 processor.

Figure 9 Microinstruction Pipeline of the VAX 8800 CPU

# Microbranch Latency

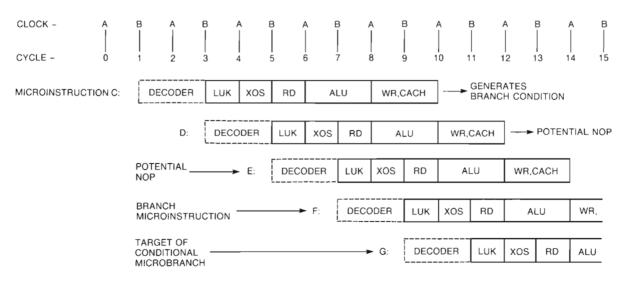

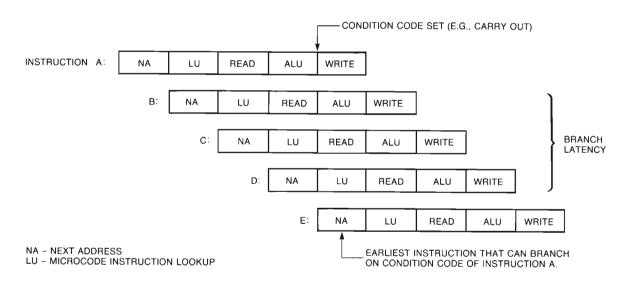

One consequence of pipelining is that any intervening microinstructions must be spaced between the instruction that produces a branch condition and the instruction that can branch on it due to latency in the development of the branch condition. Obviously, the execution of the intervening microinstructions must be independent of the branch. Usually, microcoders are able to code some useful operations during the inevitable wait. Otherwise, the intervening instructions must be NOPs (no operation). Figure 10 shows the microbranch latency in the VAX 8800 CPU.

# Microtrap Latency

A hardware exception causes a microtrap. However, the trap conditions, like the branch conditions, may develop after some execution cycles have been completed. Once again there must be some intervening microinstructions between the trap-causing microinstruction and the trap-handling routine. Moreover, the state of the micromachine must be saved so that the current execution can be resumed in such a way that the intervening execution of the trap routine appears to be transparent. This state consists primarily of microbranch conditions that result from the execution of microinstructions in the pipeline since those could influence subsequent microaddresses and hence the execution sequence. Therefore, on interruption of the current sequence by the trap routine, the branch

conditions from the earlier execution are essential to reproduce the same sequence.

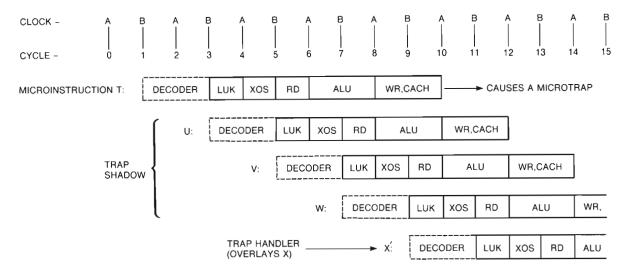

To simplify the hardware design, all early traps are delayed to a fixed canonical time  $(T_{10})$ . Some trap conditions, however, develop later than the canonical time with the consequence that those traps cannot be returned from. In such cases the microcode must roll back the state to the beginning, which causes a reexecution of the entire macroinstruction.

Figure 11 shows a sequence in which a microinstruction at address T provokes a microtrap. At the earliest, the trap-handling routine can begin at microinstruction X. Meanwhile, microinstructions U, V, and W follow T, quite unaware of the impending trap. In fact, they are in partial execution when the trap condition is detected. These microinstructions are said to be in the trap shadow, and they must be blocked from writing any registers, thus making it appear as if they had never executed. When control is returned from the trap-handling routine, these trap shadow microinstructions are reexecuted, continuing the sequence that would have arisen had the trap not occurred.

# Instruction Buffer and Decoder

The IB buffers the prefetched VAX i-stream delivered by the cache and in turn delivers the opcode and specifier to the decoder. The IB also delivers the i-stream data to the execution unit, the E Box. The decoder expects to receive the current opcode and the current specifier byte.

Figure 10 Microbranch Latency

Figure 11 Microtrap Latency

Hence the IB saves the opcode for the duration of the instruction execution and shifts the buffered i-stream along to send each specifier in turn to the decoder. The goal of the VAX 8800 decoder is to produce a starting microaddress corresponding to the opcode and the specifiers. The sequence of microcode execution caused by the decoder is first to process all the specifiers, making all the operands available, and then to execute the operation specified by the opcode. If an instruction has no specifiers, the execution microcode is initiated directly. In any case the decoder always has a microaddress ahead of time for the microsequencer. This microaddress is the starting address of either a specifier routine or the execution routine, based on the contents and the state of the IB.

If at any time the IB does not contain enough i-stream data for a successful decode, the decoder will produce a special microaddress. The microinstruction at that address is simply a NOP that again requests the selection of the decoder's address. The micromachine thus waits in a loop for sufficient i-stream data to arrive in the IB so that the decoder can again dispatch a useful microaddress. This wait-loop state of the micromachine is commonly referred to as the IB stall, which is different from the stall described earlier. Note that clocks to stalled A-latches are not blocked for an IB stall. On the contrary, the micromachine runs normally as does the rest of the processor hardware. IB stalls may occur when the instruction prefetch pipeline is broken due to macroinstruction branches. This condition requires the current contents of the IB to be discarded and new i-stream data to be prefetched into the IB.

The VAX 8800 IB is a four-longword circular queue, which is usually long enough to hold an entire instruction. The data is consumed out of the IB from the position pointed to by the read pointer. However, new data could be written concurrently by the cache at the position pointed to by the write pointer. Whenever it has room, the IB is loaded by the cache if the cache has no other higher priority job to do. Occasionally, the IB becomes full (the write pointer catches up with the read pointer), and then it does not accept the datum from the cache. If a datum is not accepted by the IB, the cache keeps repeating the transfer until the datum is accepted. Occasionally, the IB becomes empty if the cache is busy doing other things and the decoder has consumed all the data from the IB (the read pointer and the write pointer point to the same location).

The IB in the VAX 8800 family is implemented with four identical gate arrays with 8-bit slices designed to use a rather clever bit-scattering/gathering scheme. The IB also contains logic to extract and format i-stream data, making it available to the E Box. A common silo holds the opcode history for the duration of a macroinstruction's execution, as well as for recovery from microtraps. The VAX 8800 decoder is a RAM-based look-up table for generating

Figure 12 VAX 8800 Decoder

microaddresses. In the case of special events, however, hardware logic is provided for generating special microaddresses, as shown in Figure 12, thus bypassing the RAM look-up. The decoder also provides controls for the IB statemachine as well as some other hardware assists.

#### Microsequencer

The state-machine responsible for generating the next microaddress for a microinstruction sequence is commonly called the microsequencer. As shown in Figure 13, this state-machine is realized collectively by the control store, the next

Figure 13 An Abstract Microsequencer

microaddress generation logic, and the microaddress and microdata latches (or registers).

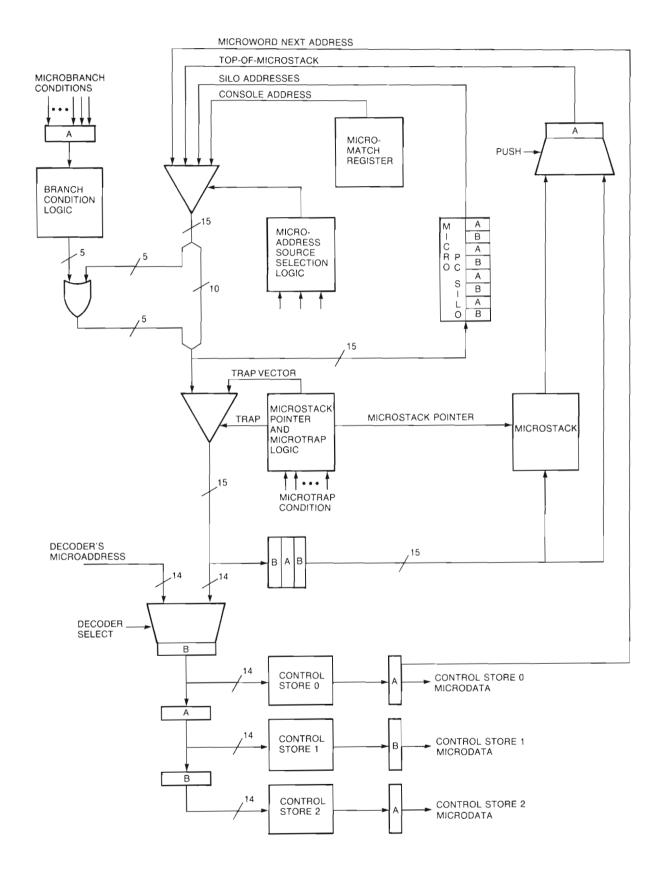

The goal of the VAX 8800 microsequencer is to produce the address of the next microinstruction during every cycle. Figure 14 depicts how the microsequencer achieves this goal.

Each microinstruction may modify its nextmicroaddress field through a microbranch command to produce the address of the target microinstruction. Microbranch conditions are delivered by other sections of the machine, such as the ALU. These conditions are grouped together in ways convenient for microprogramming so that multiway branches can be taken. Microsubroutines can be called and returned from by means of a hardware microPC stack.

Stalls cause the microsequencer state to be frozen on a cycle boundary (i.e., the clocks on microaddress and microdata latches are effectively blocked). Microtraps allow the microcode to deal with unusual events that would be too slow or inconvenient to check normally with microbranches, such as TB misses and address misalignments. The VAX 8800 processor does not permit traps to be nested. Instead, traps are "chained," meaning that trap routines and hardware trap priorities are carefully arranged so that a second trap is taken only when the first trap routine finishes. (Machine check traps cannot be controlled in this way.)

### Sources of Microaddresses

There are five sources for microaddresses:

- The decoder

- The next-address field in the microword

- The microstack upon returning from a subroutine

- The microPC silo for a saved microtrap

- The micromatch register for an address from the console

An address from the console is selected in response to an explicit console request and takes precedence over everything else. Addresses from the silo are requeued in response to a trap-return command. Addresses from the microstack are selected in response to a subroutine-return command. A decoder-generated address is selected whenever the current sequence ends and a new specifier or execution

routine should begin. Normally, this selection is caused by the assertion of a microword bit in the very last microinstruction of the current sequence. The next-address field is selected as the default for normal sequencing. This field is also used to provide an offset in case of subroutine returns.

# Microbranching

In normal cases, part of the selected microaddress can be modified according to the branch conditions, that is, whenever the next-address field is selected. A combination of two microword fields, branch type and branch mask, selects the branch conditions, which are then ORed into part of the target microaddress. In the VAX 8800 system, the microbranch logic is implemented with five identical gate arrays, each of which generates a 3-bit slice of the microaddress. One microaddress bit is branch sensitive in each slice. This organization permits up to 32-way branching. Branchings of 2, 4, 8, and 16 ways are also made possible by a separate mask bit, called the branch mask, to every slice. This bit is used to turn off the sensitivity to branch conditions in a particular slice.

There are 16 basic recipes for conditional branching in each slice. This arrangement of slicing, masking, and branch-condition selection in every slice requires that all the microbranch conditions be organized into 5 groups of 16 conditions each. The branch conditions are classified as either static or dynamic. Static conditions, once captured, are available for branching in any later cycle as long as those conditions remain unchanged. Dynamic conditions are asserted for just one cycle and must be branched on in that cycle.