- Availability in VAX cluster Systems

- Network Performance and Adapters

## Digital Technical Journal

Digital Equipment Corporation

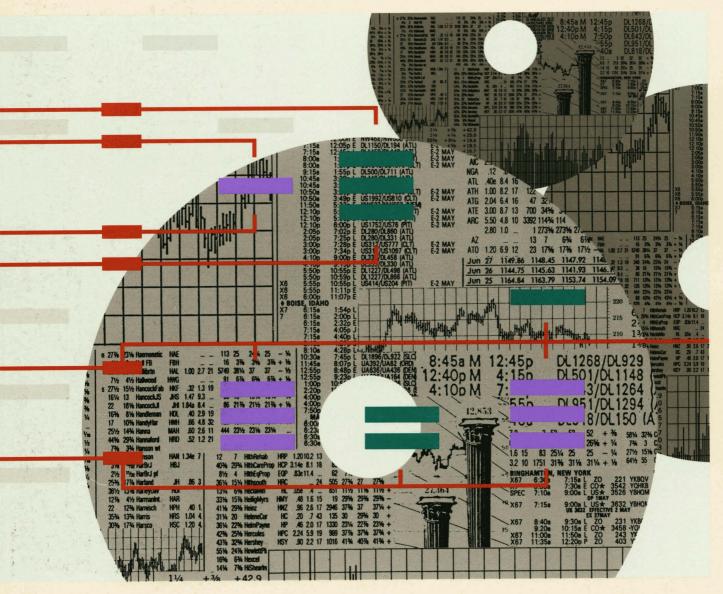

### Cover Design

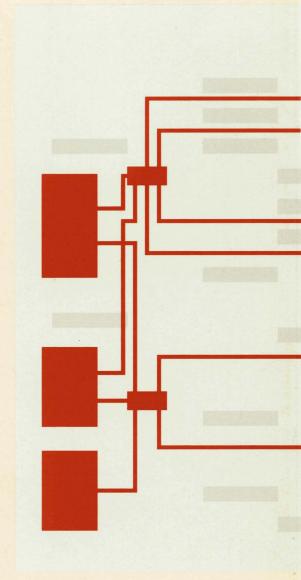

Our cover graphic represents the shadowing, or replication, of data on multiple physical disks in a VAXcluster environment. VMS host-based volume shadowing provides the high data availability required for applications such as transaction processing and is the subject of one of the papers in this issue. The cover was designed by Sandra Calef of Calef Associates.

#### **Editorial**

Jane C. Blake, Editor Kathleen M. Stetson, Associate Editor Leon Descoteaux, Associate Editor

#### Circulation

Catherine M. Phillips, Administrator Sherry L. Gonzalez

#### **Production**

Mildred R. Rosenzweig, Production Editor Margaret Burdine, Typographer Peter Woodbury, Illustrator

#### **Advisory Board**

Samuel H. Fuller, Chairman Richard W. Beane Robert M. Glorioso Richard J. Hollingsworth John W. McCredie Alan G. Nemeth Mahendra R. Patel F. Grant Saviers Victor A. Vyssotsky Gayn B. Winters

The *Digital Technical Journal* is published quarterly by Digital Equipment Corporation, 146 Main Street MLO1-3/B68, Maynard, Massachusetts 01754-2571. Subscriptions to the *Journal* are \$40.00 for four issues and must be prepaid in U.S. funds. University and college professors and Ph.D. students in the electrical engineering and computer science fields receive complimentary subscriptions upon request. Orders, inquiries, and address changes should be sent to the *Digital Technical Journal* at the published-by address. Inquiries can also be sent electronically to DTJ@CRL.DEC.COM. Single copies and back issues are available for \$16.00 each from Digital Press of Digital Equipment Corporation, 12 Crosby Drive, Bedford, MA 01730-1493.

Digital employees may send subscription orders on the ENET to RDVAX::JOURNAL or by interoffice mail to mailstop MLO1-3/B68. Orders should include badge number, site location code, and address. All employees must advise of changes of address.

Comments on the content of any paper are welcomed and may be sent to the editor at the published-by or network address.

Copyright © 1991 Digital Equipment Corporation. Copying without fee is permitted provided that such copies are made for use in educational institutions by faculty members and are not distributed for commercial advantage. Abstracting with credit of Digital Equipment Corporation's authorship is permitted. All rights reserved.

The information in the *Journal* is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in the *Journal*.

#### ISSN 0898-901X

#### Documentation Number EY-H890E-DP

The following are trademarks of Digital Equipment Corporation: BI, CI, DEC, DECconcentrator, DECdtm, DEC FDDIcontroller, DECnet, DELNI, DSA, DSSI, Digital, the Digital logo, HSC, LAT, Local Area VAXcluster, MSCP, RA, Rdb/VMS, TA, ULTRIX, UNIBUS, VAX, VAX DBMS, VAX MACRO, VAX RMS, VAX 6000, VAX 9000, VAXcluster, VMS, VMS Volume Shadowing.

Motorola and 68000 are registered trademarks of Motorola, Inc.

Book production was done by Digital's Database Publishing Group in Northboro, MA.

### **Contents**

5 *Foreword* Howard H. Hayakawa and George S. Hoff

Availability in VAXcluster Systems Network Performance and Adapters

- 7 Design of VMS Volume Shadowing Phase II—Host-based Shadowing Scott H. Davis

- 16 Application Design in a VAXcluster System William E. Snaman, Jr.

- 27 New Availability Features of Local Area VAXcluster Systems Lee Leahy

- 36 **Design of the DEC LANcontroller 400 Adapter** Richard E. Stockdale and Judy B. Weiss

- 48 The Architecture and Implementation of a High-performance FDDI Adapter Satish L. Rege

- 64 Performance Analysis of a High-speed FDDI Adapter

Ramsesh S. Kalkunte

- 78 Performance Analysis of FDDI Raj Jain

#### Editor's Introduction

Jane C. Blake Editor

This issue of the *Digital Technical Journal* contains a collection of papers on two general topics—VAXcluster systems, and network adapters and performance. The first set of three papers describes new VMS VAXcluster developments and features; the second set addresses the topics of LAN adapter design and performance measurement techniques. A common theme across these papers is the development of technologies for interconnecting systems that offer high data availability without sacrificing performance.

VMS Volume Shadowing, described by Scott Davis, is a means of ensuring data availability and integrity in VMS VAXcluster systems. By maintaining multiple copies of data on separate devices, the volume shadowing technique protects data from being lost as the result of media deterioration or device failures. Scott discusses the advantages of the new design over controller-based shadowing and explains how this fully distributed software makes a broad range of topologies suitable for shadowing.

The growth capabilities and availability of VMS VAXcluster systems are characteristics well suited to applications with high-availability requirements. Sandy Snaman first presents an overview of the VAXcluster system architecture, including explanations of the layers, their purpose and function. He then gives practical insights into how the system implementation affects application design and reviews the choices available to application designers in the areas of client-server computing and data sharing.

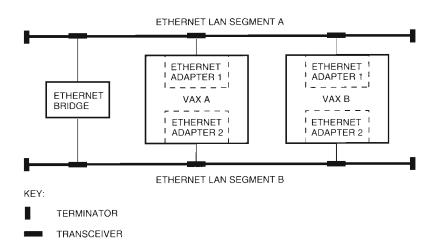

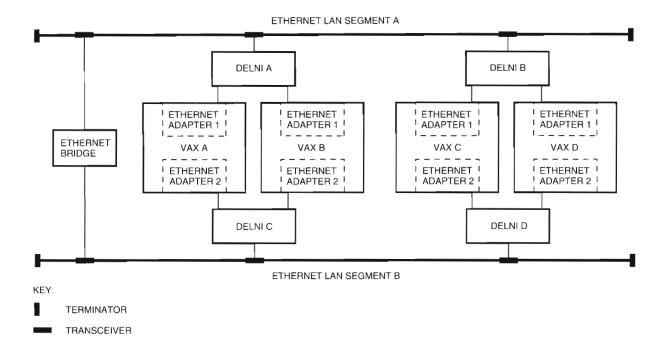

The availability of applications and cluster configurations is also enhanced by developments in a new release of the VMS operating system. Lee Leahy describes a VMS feature that enables fail-over between multiple LAN adapters and compares this approach to a single-adapter implementation. He then discusses and gives examples of VMS features

for network delay detection and reduction, and failure analysis in local area VAXcluster systems.

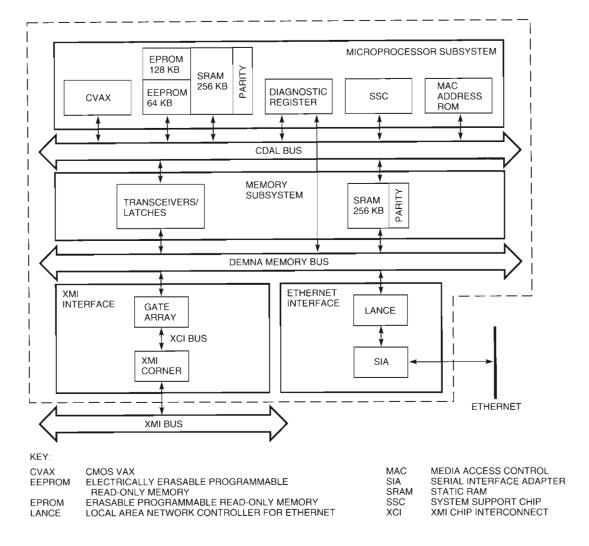

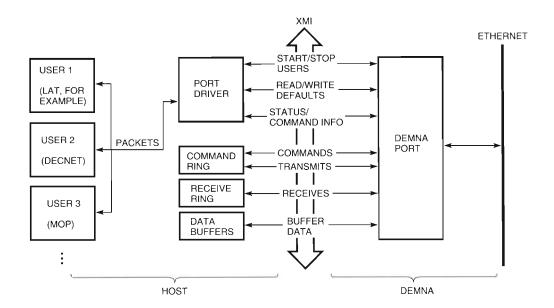

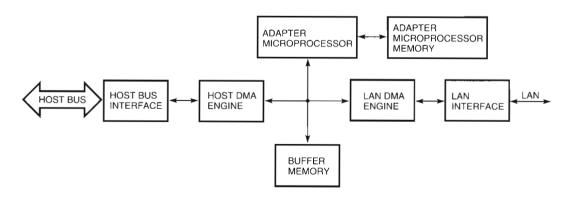

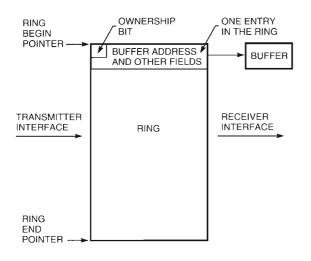

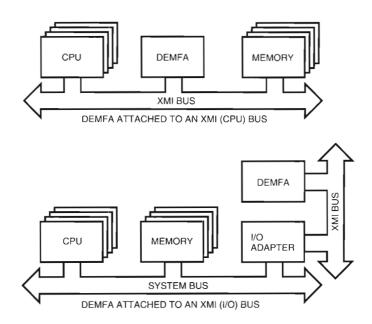

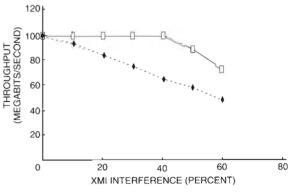

The focus then moves from VMS-level concerns to the design of network adapters and performance measurement. The adapter described by Dick Stockdale and Judy Weiss is the DEC LANcontroller 400, which connects systems based on Digital's XMI bus to an Ethernet LAN. This particular design improves on previous designs by transforming the adapter from a dumb to an intelligent adapter which can off-load the host. Consequently, the adapter supports systems that utilize the full bandwidth of Ethernet. The authors provide a system overview, performance metrics, and a critical examination of firmware-based design.

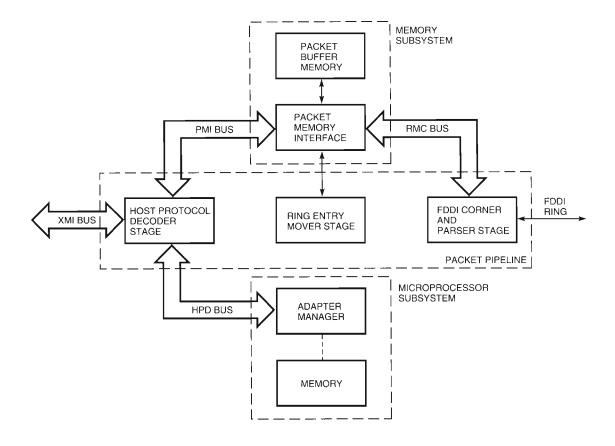

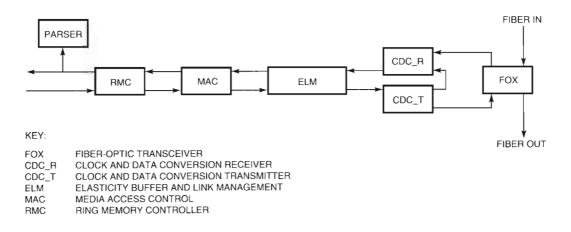

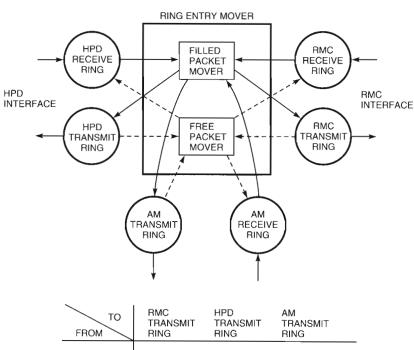

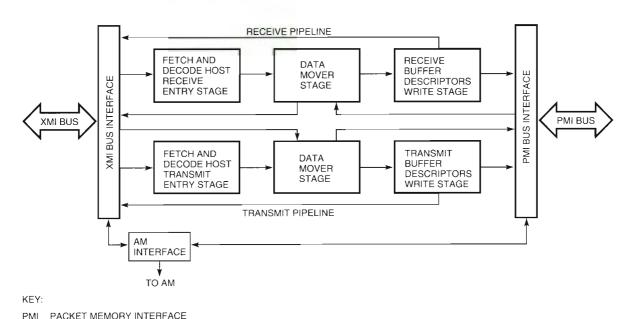

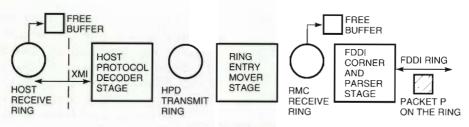

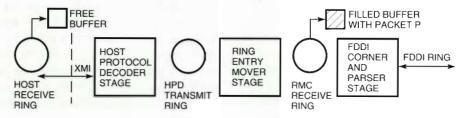

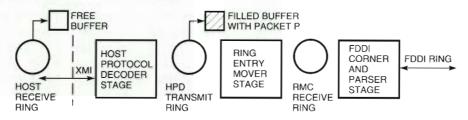

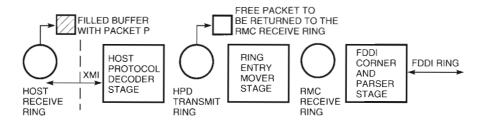

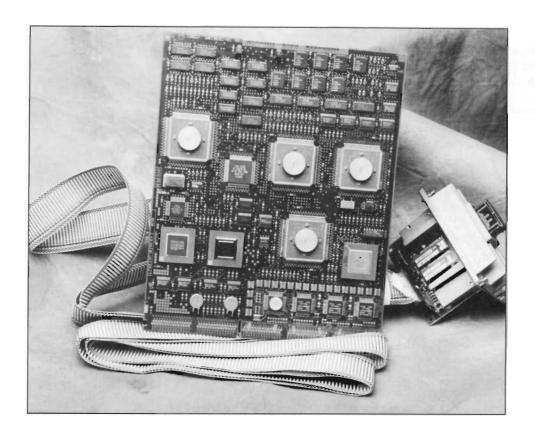

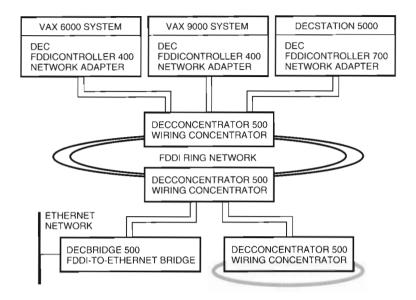

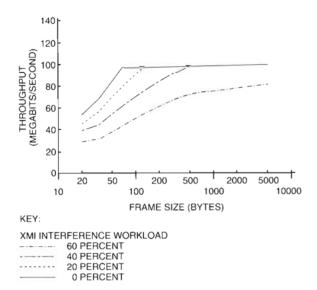

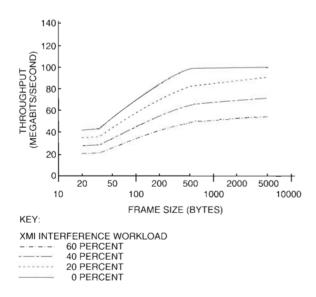

Like the LANcontroller 400, the FDDIcontroller 400 is an adapter that interfaces XMI-based systems to a LAN. However, as Satish Rege relates, this adapter was required to transmit data 30 times faster than Ethernet adapters. Satish discusses the architecture and the choices designers made to address the problem of interfacing a parallel high-bandwidth CPU bus (XMI) to a serial fiber-optic network bus (FDDI). Their design choices included a three-stage pipeline approach to buffering that enables these stages to proceed in an asynchronous fashion.

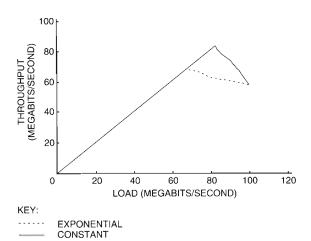

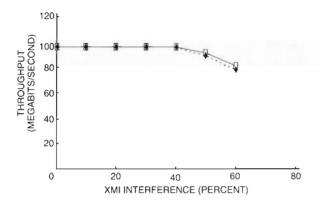

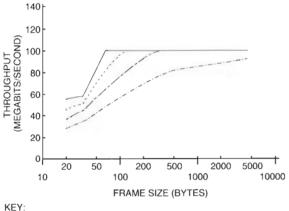

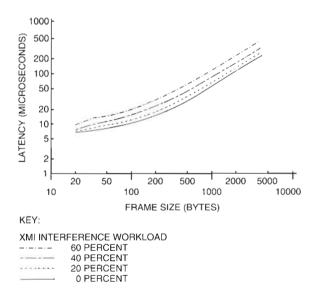

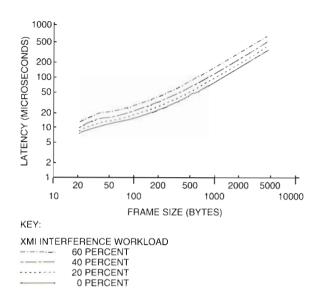

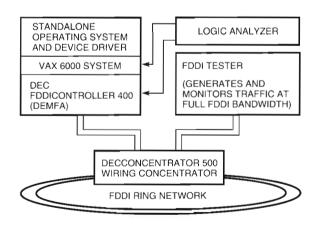

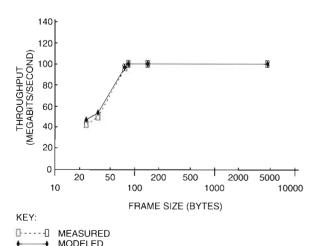

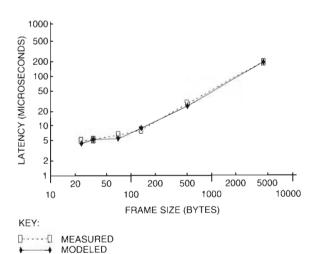

To ensure that the performance goals for the FDDIcontroller would be met, a simulation model was created. In his paper, Ram Kalkunte details the modeling methodology, reviews components, and presents simulation results. Ram describes how in addition to performance projections, the model provided designers with buffer sufficiency analysis and helped engineers analyze the functional correctness of the adapter design.

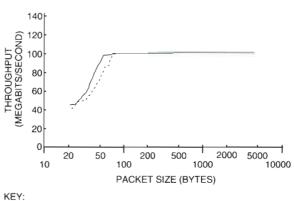

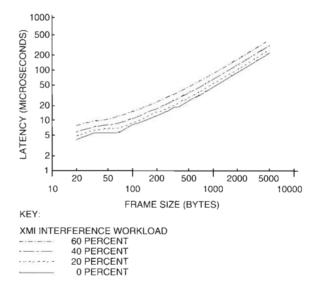

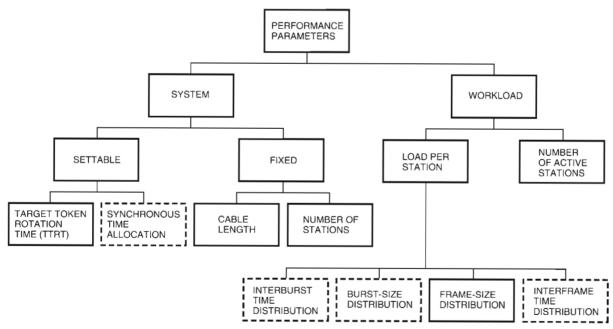

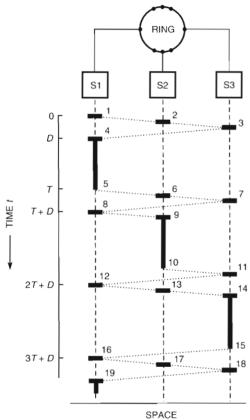

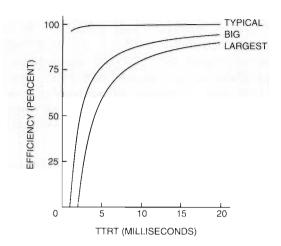

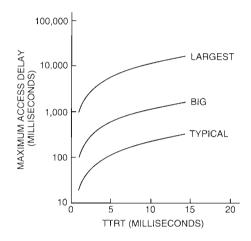

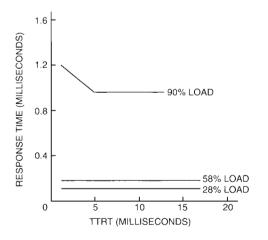

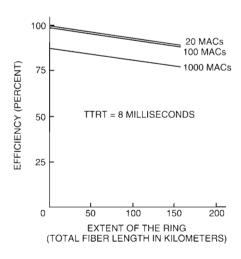

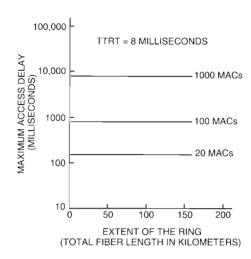

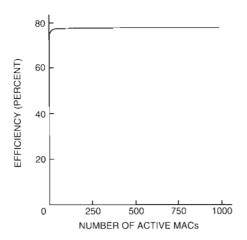

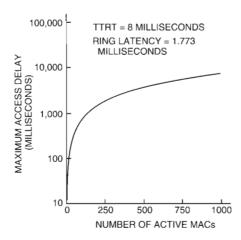

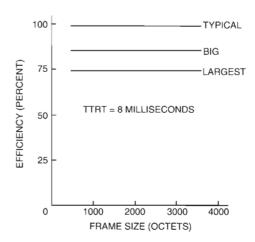

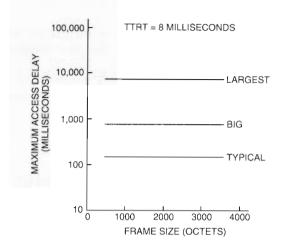

The high level of performance achieved by the FDDIcontroller was driven by the high performance of the FDDI LAN itself—100 megabits per second. Raj Jain's subject is performance measurement at the level of the FDDI LAN. Raj describes the performance analysis of Digital's implementation of FDDI and how various parameters affect system performance. As part of his presentation of the modeling and simulation methods used, he shares guidelines for setting the value of one of the key parameters, target token rotation time, to optimize performance. Raj has recently published a book on computer systems performance analysis, which is reviewed in the Further Readings section of this issue.

Jane Blake

### Biographies

Scott H. Davis Consultant software engineer Scott Davis is the VMS Cluster Technical Director. He is involved in future VMS I/O subsystem, VAXcluster, and storage strategies and led the VMS Volume Shadowing Phase II and VMS mixed-interconnect VAXcluster I/O projects. Since joining Digital in 1979, Scott worked on RT-11 development and led various real-time operating systems projects. He holds a B.S. (1978, cum laude) in computer science and applied mathematics from the State University of New York at Albany. Scott is a coinventor for four patents on the shadowing design.

**Raj Jain** Raj Jain is a senior consulting engineer involved in the performance modeling and analysis of computer systems and networks, including VAXcluster, DECnet, Ethernet, and FDDI products. He holds a Ph.D. (1978) from Harvard University and has taught courses in performance analysis at M.I.T. A member of the Authors' Guild and senior member of IEEE, Raj has written over 25 papers and is listed in *Who's Who in the Computer Industry*, 1989. He is the author of *The Art of Computer Systems Performance Analysis* published recently by Wiley.

Ram Kalkunte As a member of the VAX VMS Systems and Servers Group, senior engineer Ram Kalkunte worked on the development of the high-performance XMI-to-FDDI adapter. Since joining Digital in 1987, he has also worked on various performance analysis and modeling projects. Ram received a B.E. (1984) in instrumentation engineering from Mysore University in India and an M.S. (1987) in electrical engineering from Worcester Polytechnic Institute. He has a pending patent related to dynamically arbitrating conflicts in a multiport memory controller.

**Lee Leahy** Lee Leahy is a principal software engineer in the VAXcluster group in ALPHA/EVMS Development. He is currently the project leader of the Local Area VAXcluster development effort and was responsible for the final design and implementation of the multiple-adapter version of PEDRIVER. Lee joined Digital in 1988 from ECAD. He is coauthor of the book *VMS Advanced Device Driver Techniques* and has been writing VMS device drivers since 1980. Lee received a B.S. degree in electrical engineering from Lehigh University in 1977.

**Satish L. Rege** Satish Rege joined Digital in 1977 as a member of the Mass Storage Group. He wrote the first proposal for the MSCP protocol and evaluated disk controller design alternatives (e.g., seek algorithms and disk caching) for the HSC50 by implementing architectural and performance simulation. He was instrumental in architecting the low-end controllers used in RF-series disks. His latest project was the high-performance FDDI adapter. Satish is a consulting engineer and received his Ph.D. from Carnegie-Mellon University, Pittsburgh.

William E. Snaman Principal software engineer Sandy Snaman joined Digital in 1980. He is the technical supervisor for the VAXcluster executive services area and a project leader for VAXcluster advanced development in the VMS Development Group. His group is responsible for ongoing development of the VMS lock manager, connection manager, and clusterwide services. Sandy teaches computer science at Daniel Webster College and developed and taught VAXcluster courses in Educational Services. He holds a B.S. (1985, magna cum laude) and an M.S.C.S. from the University of Lowell.

Richard E. Stockdale As a member of the Midrange Systems Engineering Group, Dick Stockdale was firmware project leader for the DEMNA project and prior to that for the DEBNA and DEBNI Ethernet adapters. He is currently a software consulting engineer working on LAN drivers in the VMS Development Group. Dick joined Digital in 1978 and performed diagnostic testing for 36-bit systems. He graduated from Worcester Polytechnic Institute in 1973 with a B.S. (magna cum laude) in computer science and a minor in electrical engineering. He is a member of Tau Beta Pi.

**Judy B. Weiss** Judy Weiss contributed to the design, implementation, debug, and performance analysis of the DEMNA Ethernet adapter as a member of the firmware team. She is a senior engineer working in the Data Center Systems and Servers Group as a gate array designer. Concurrently with the DEMNA, she worked on the firmware for the DEBNI adapter. Judy joined Digital in 1986 after receiving her B.S. (magna cum laude) in computer engineering from Boston University. She is a member of Tau Beta Pi and the Society for Women Engineers.

#### **Foreword**

Howard H. Hayakawa Manager, VMS I/O and Cluster Development

**George S. Hoff** Group Manager, High-availability Systems

Beginning as a vision for a highly available and expandable computing environment, Digital's VAXcluster system is today recognized across the industry as the premiere foundation for creating high-availability applications. The large number of VAXcluster sites and the range of their use testifies to the wide appeal of the capabilities of VAXcluster systems. Over 11,000 VAXcluster sites based on Digital's Computer Interconnect (CI) are being used in such diverse applications as manufacturing operations, banking, and telephone information systems. Sites based on the Digital Storage System Interconnect (DSSI) and Ethernet are even more numerous. A scan of software licenses shows an amazing acceptance of VAXcluster technology-more than 200,000 VAXcluster licenses have been sold to date.

Built from standard processors and a general-purpose operating system, a VAXcluster system is a loosely coupled, highly integrated configuration of VAX VMS processors and storage systems that operates as a single system. Significantly, VAXcluster systems are so well integrated that users are often not aware they are using a distributed system. In addition to the benefits of tight integration, these configurations provide Digital's customers with the flexibility to easily expand and with the features needed for high-availability applications.

Started in 1984, VAXcluster systems were limited to specialized, proprietary interconnects and storage servers, which restricted them to the confines of a single computer room. In 1989, the cluster system was extended to support both industry-standard SCSI (small computer systems interface) storage and Digital's DSSI storage interconnect. Today, VAXcluster systems support a wide range of communication interconnects, including Cl and

DSSI, and industry-standard local area networks such as Ethernet and FDDI. Storage systems now supported cover the spectrum from standard, economical SCSI peripherals to high-performance RA-series drives for large configurations. This well-architected system has allowed for expansion across an ever wider geography: from room to building to multiple buildings. Moreover, the entire range of VAX processors—from VAXstation work-stations to VAX 9000 mainframes—are supported. The tight integration, flexibility, and power of today's VAXcluster systems is unparalleled.

The VAXcluster architecture which Digital initiated in the 1980s continues to encompass new advances and innovative technologies that ensure data availability and integrity. This issue of the Digital Technical Journal presents several new VMS VAXcluster products and features, and complementary developments in the areas of network adapters and performance. One of the products described is VMS Volume Shadowing Phase II which permits users to place redundant data on separate storage devices where most appropriate within the system, thus dramatically increasing the availability potential of VAXcluster systems. A paper on multi-rail local area VAXclusters shows how customers are now able to add parallel LAN connections to increase network capacity and to survive failure of a network connection. With shadowing and multiple communication paths, recovery from site failure need no longer incur the delays associated with restoration from archives.

Just as the VAXcluster software was able to exploit the Ethernet to extend capabilities throughout a building, it is now able to exploit the high performance and extent of an FDDI LAN.

The new industry-standard FDDI LAN allows the VAXcluster software to extend the system's range by a factor of 1,000. Papers on both an Ethernet adapter and an FDDI adapter describe the care taken to ensure that adapter performance matches that of the target processor, which is one of the keys to achieving maximum performance in the overall VAXcluster system. Performance of the FDDI LAN itself is also one of the topics included here. FDDI's performance and range permit for the first time the ability to create integrated, high-availability solutions that span multiple buildings. With combined FDDI and VMS VAXcluster technology, a bank's VAXcluster system can extend from a computer center in Manhattan to a standby center in New Jersey. Should Manhattan lose power, a disaster team can bring the bank's application into operation in New Jersey after only minutes. The days of waiting for archives or driving tapes and disks across the river are over.

Digital's VAX VMS, clusters, FDDI, and networking products continue to evolve; the process of integrating new technologies is ongoing. The papers in this issue describe the latest steps we have taken to extend the range and availability of VAXcluster systems. Future issues of the *Journal* will keep you apprised of the latest stages in this evolutionary process.

### Design of VMS Volume Shadowing Phase II— Host-based Shadowing

VMS Volume Shadowing Phase II is a fully distributed, clusterwide data availability product designed to replace the obsolete controller-based shadowing implementation. Phase II is intended to service current and future generations of storage architectures. In these architectures, there is no intelligent, multiunit controller that functions as a centralized gateway to the multiple drives in the shadow set. The new software makes many additional topologies suitable for shadowing, including DSSI drives, DSA drives, and shadowing across VMS MSCP servers. This last configuration allows shadow set members to be separated by any supported cluster interconnect, including FDDI. All essential shadowing functions are performed within the VMS operating system. New MSCP controllers and drives can optionally implement a set of shadowing performance assists, which Digital intends to support in a future release of the shadowing product.

#### Overview

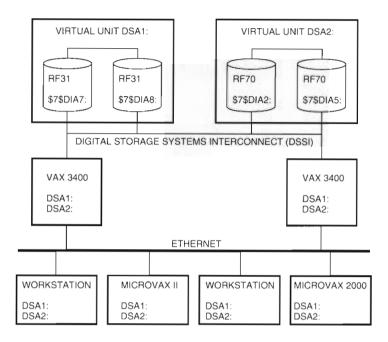

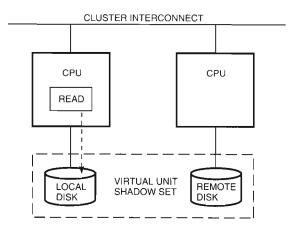

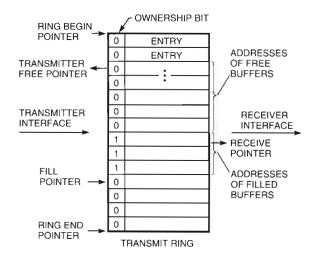

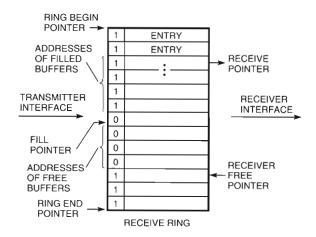

Volume shadowing is a technique that provides data availability to computer systems by protecting against data loss from media deterioration, communication path failures, and controller or device failures. The process of volume shadowing entails maintaining multiple copies of the same data on two or more physical volumes. Up to three physical devices are bound together by the volume shadowing software and present a virtual device to the system. This device is referred to as a shadow set or a virtual unit. The volume shadowing software replicates data across the physical devices. All shadowing mechanisms are hidden from the users of the system, i.e., applications access the virtual unit as if it were a standard, physical disk. Figure 1 shows a VMS Volume Shadowing Phase II set for a Digital Storage Systems Interconnect (DSSI) configuration of two VAX host computers.

#### **Product Goals**

The VMS host-based shadowing project was undertaken because the original controller shadowing product is architecturally incompatible with many prospective storage devices and their connectivity requirements. Controller shadowing requires an intelligent, common controller to access all

physical devices in a shadow set. Devices such as the RF-series integrated storage elements (ISEs) with DSSI adapters and the RZ-series small computer systems interface (SCSI) disks present configurations that conflict with this method of access.

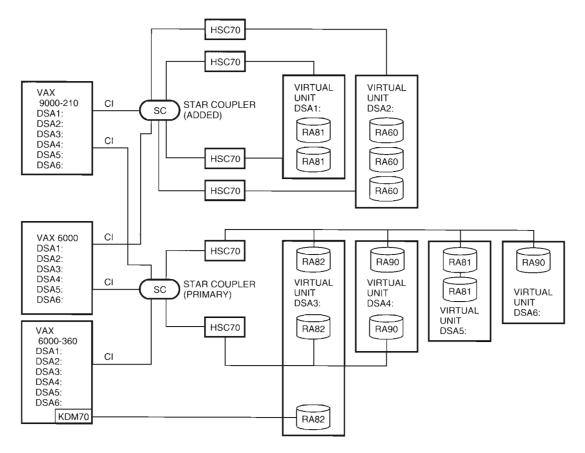

To support the range of configurations required by our customers, the new product had to be capable of shadowing physical devices located anywhere within a VAXcluster system and of doing so in a controller-independent fashion. The VAXcluster I/O system provides parallel access to storage devices from all nodes in a cluster simultaneously. In order to meet its performance goals, our shadowing product had to preserve this semantic also. Figure 2 shows clusterwide shadow sets for a hierarchical storage controller (HSC) configuration with multiple computer interconnect (CI) buses. When compared to Figure 1, this figure shows a larger cluster containing several clusterwide shadow sets. Note that multiple nodes in the cluster have direct, writable access to the disks comprising the shadow sets.

In addition to providing highly available access to shadow sets from anywhere in a cluster, the new shadowing implementation had other requirements. Phase II had to deliver performance comparable to that of controller-based shadowing,

Figure 1 Phase II Shadow Set for a Dual-host DSSI Configuration

maximize application I/O availability, and ensure data integrity for critical applications.

In designing the new product, we benefited from customer feedback about the existing implementation. This feedback had a positive impact on the design of the host-based shadowing implementation. Our goals to maximize application I/O availability during transient states, to provide customizable, event-driven design and fail-over, to enable all cluster nodes to manage the shadow sets, and to enhance system disk capabilities were all affected by customer feedback.

#### Technical Challenges

To provide volume shadowing in a VAXcluster environment running under the VMS operating system required that we solve complex, distributed systems problems.<sup>1</sup> This section describes the most significant technical challenges we encountered and the solutions we arrived at during the design and development of the product.

Membership Consistency To ensure the level of integrity required for high availability systems, the shadowing design must guarantee that a shadow set has the same membership and states on all nodes in the cluster. A simple way to guarantee this property would have been a strict client-server implementation, where one VAX computer serves the shadow

set to the remainder of the cluster. This approach, however, would have violated several design goals; the intermediate hop required by data transfers would decrease system performance, and any failure of the serving CPU would require a lengthy fail-over and rebuild operation, thus negatively impacting system availability.

To solve the problem of membership consistency, we used the VMS distributed lock manager through a new executive thread-level interface.2.3 We designed a set of event-driven protocols that shadowing uses to guarantee membership consistency. These protocols allowed us to make the shadow set virtual unit a local device on all nodes in the cluster. Membership and state information about the shadow set is stored on all physical members in an on-disk data structure called the storage control block (SCB). One way that shadowing uses this SCB information is to automatically determine the most up-to-date shadow set member(s) when the set is created. In addition to distributed synchronization primitives, the VMS lock manager provides a capability for managing a distributed state variable called a lock value block. Shadowing uses the lock value block to define a disk that is guaranteed to be a current member of the shadow set. Whenever a membership change is made, all nodes take part in a protocol of lock operations; the value block and the on-disk SCB are the final arbiters of set constituency.

Sequential Commands A sequential I/O command, i.e., a Mass Storage Control Protocol (MSCP) concept, forces all commands in progress to complete before the sequential command begins execution. While a sequential command is pending, all new I/O requests are stalled until that sequential command completes execution. Shadowing requires the capability to execute a clusterwide, sequential command during certain operations. This capability, although a simple design goal for a client-server implementation, is a complex one for a distributed access model. We chose an event-driven, request/response protocol to create the sequential command capability.

Since sequential commands have a negative impact on performance, we limited the use of these commands to performing membership changes, mount/dismount operations, and bad block and merge difference repairs. Steady state processing never requires using sequential commands.

Full Copy A full copy is the means by which a new member of the shadow set is made current

with the rest of the set. The challenge is to make copy operations unintrusive; application I/Os must proceed with minimal impact so that the level of service provided by the system is both acceptable and predictable. VMS file I/O provides record-level sharing through the application transparent locking provided by the VAX RMS software, Digital's record management services. Shadowing operates at the physical device level to handle a variety of low-level errors. Because shadowing has no knowledge of the higher-layer record locking, a copy operation must guarantee that the application I/Os and the copy operation itself generate the correct results and do so with minimal impact on application I/O performance.

Merge Operations Merge operations are triggered when a CPU with write access to a shadow set fails. (Note that with controller shadowing, merge operations are copy operations that are triggered when an HSC fails.) Devices may still be valid members of the shadow set but may no longer be identical, due to outstanding writes in progress when the host

Figure 2 Clusterwide Shadow Sets for an HSC Configuration with Multiple CI Buses

CPU failed. The merge operation must detect and correct these differences, so that successive application reads for the same data produce consistent results. As for full copy operations, the challenge with merge processing is to generate consistent results with minimal impact on application I/O performance.

Booting and Crashing System disk shadowing presents some special problems because the shadow set must be accessible to CPUs in the cluster when locking protocols and inter-CPU communication are disabled. In addition, crashing must ensure appropriate behavior for writing crash dumps through the primitive bootstrap driver, including how to propagate the dump to the shadow set. It was not practical to modify the bootstrap drivers because they are stored in read-only memory (ROM) on various CPU platforms that shadowing would support.

Error Processing One major function of volume shadowing is to perform appropriate error processing for members of the shadow set, while maximizing data availability. To carry out this function, the software must prevent deadlocks between nodes and decide when to remove devices from the shadow set. We adopted a simple recovery ethic: a node that detects an error is responsible for fixing that error. Membership changes are serialized in the cluster, and a node only makes a membership change if the change is accompanied by improved access to the shadow set. A node never makes a change in membership without having access to some source members of the set.

#### Architecture

Phase II shadowing provides a local virtual unit on each node in the cluster with distributed control of that unit. Although the virtual unit is not served to the cluster, the underlying physical units that constitute a shadow set are served to the cluster using the standard VMS mechanisms. This scheme has many data availability advantages. The Phase II design

- Allows shadowing to use all the VMS controller fail-over mechanisms for physical devices. As a result, member fail-over approaches hardware speeds. Controller shadowing does not provide this capability.

- Allows each node in the cluster to perform error recovery based on access to physical data

source members. The shadowing software treats communication failures between any cluster node and shadow set members as normal shadowing events with customer-definable recovery metrics.

#### Major Components

VMS Volume Shadowing Phase II consists of two major components: SHDRIVER and SHADOW\_SERVER. SHDRIVER is the shadowing virtual unit driver. As a client of disk class drivers, SHDRIVER is responsible for handling all I/O operations that are directed to the virtual unit. SHDRIVER issues physical I/O operations to the disk class driver to satisfy the shadow set virtual unit I/O requests. SHDRIVER is also responsible for performing all distributed locking and for driving error recovery.

SHADOW\_SERVER is a VMS ancillary control process (ACP) responsible for driving copy and merge operations performed on the local node. Only one optimal node is responsible for driving a copy or merge operation on a given shadow set, but when a failure occurs the operation will fail over and resume on another CPU. Several factors determine this optimal node including the types of access paths, and controllers for the members and user-settable, per-node copy quotas.

#### **Primitives**

This section describes the locking protocols and error recovery processing functions that are used by the shadowing software. These primitives provide basic synchronization and recovery mechanisms for shadow sets in a VAXcluster system.

Locking Protocols The shadowing software uses event-driven locking protocols to coordinate clusterwide activity. These request/response protocols provide maximum application I/O performance. A VMS executive interface to the distributed lock manager allows shadowing to make efficient use of locking directly from SHDRIVER.

One example of this use of locking protocols in VMS Volume Shadowing Phase II is the sequential command protocol. As mentioned in the Technical Challenges section, shadowing requires the sequential command capability but minimizes the use of this primitive. Phase II implements the capability by using several locks, as described in the following series of events.

A node that needs to execute a sequential command first stalls I/O locally and flushes operations

in progress. The node then performs lock operations that ensure serialization and sends sequential stall requests to other nodes that have the shadow set mounted. This initiating thread waits until all other nodes in the cluster have flushed their I/Os and responded to the node requesting the sequential operation. Once all nodes have responded or left the cluster, the operations that compose the sequential command execute. When this process is complete, the locks are released, allowing asynchronous threads on the other nodes to proceed and automatically resume I/O operations. The local node resumes I/O as well.

Error Recovery Processing Error recovery processing is triggered by either asynchronous notification of a communication failure or a failing I/O operation directed towards a physical member of the shadow set. Two major functions of error recovery are built into the virtual unit driver: active and passive volume processing.

Active volume processing is triggered directly by events that occur on a local node in the cluster. This type of volume processing uses a simple, localized ethic for error recovery from communication or controller failures. Shadow set membership decisions are made locally, based on accessibility. If no members of a shadow set are currently accessible from a node, then the membership does not change. If some but not all members of the set are accessible, the local node, after attempting failover, removes some members to allow application I/O to proceed. The system manager sets the time period during which members may attempt failover. The actual removal operation is a sequential command. The design allows for maximum flexibility and quick error recovery and implicitly avoids deadlock scenarios.

Passive volume processing responds to events that occur elsewhere in the cluster; messages from nodes other than the local one trigger the processing by means of the shadowing distributed locking protocols. This volume processing function is responsible for verifying the shadow set membership and state on the local node and for modifying this membership to reflect any changes made to the set by the cluster. To accomplish these operations, the shadowing software first reads the lock value block to find a disk guaranteed to still be in the shadow set. Then the recovery process retrieves the physical member's on-disk SCB data and uses this information to perform the relevant data structure updates on the local node.

Application I/O requests to the virtual unit are always stalled during volume processing. In the case of active volume processing, the stalling is necessary because many I/Os would fail until the error was corrected. In passive volume processing, the I/O requests are stalled because the membership of the set is in doubt, and correct processing of the request cannot be performed until the situation is corrected.

#### Steady State Processing

The shadowing virtual unit driver receives application read and write requests and must direct the I/O appropriately. This section describes these steady state operations.

#### Read Algorithms

The shadowing virtual unit driver receives application read requests and directs a physical I/O to an appropriate member of the set. SHDRIVER attempts to direct the I/O to the optimum device based on locally available data. This decision is based on (1) the access path, i.e., local or served by the VMS operating system, (2) the service queue lengths at the candidate controller, and (3) a round-robin algorithm among equal paths. Figure 3 shows a shadow set read operation. An application read to the shadow set causes a single physical read to be sent to an optimal member of the set. In Figure 3, there is one local and one remote member, so the read is sent to the local member.

Data repair operations caused by media defects are triggered by a read operation failing with an appropriate error, such as forced error or parity. The shadowing driver attempts this repair using

Figure 3 Shadow Set Read Operation

another member of the shadow set. This repair operation is performed with the synchronization of a sequential command. Sequential protection is required because a read operation is being converted into a write operation without explicit, RMS-layer synchronization.

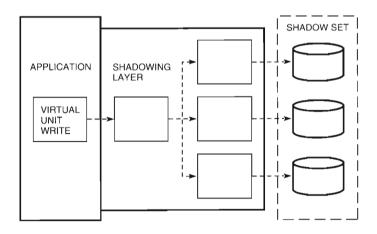

#### Write Algorithms

The shadowing virtual unit driver receives application write requests and then issues, in parallel, write requests to the physical members of the set. The virtual unit write operation does not complete until all physical writes complete. A shadow set write operation is shown in Figure 4. Physical write operations to member units can fail or be timed out; either condition triggers the shadowing error recovery logic and can cause a fail-over or the removal of the erring device from the shadow set.

#### **Transient State Processing**

Shadowing performs a variety of operations in order to maintain consistency among the members of the set. These operations include full copy, merge, and data repair and recovery. This section describes these transient state operations.

#### Full Copy

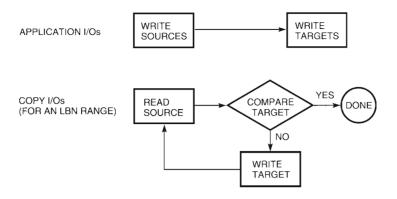

Full copy operations are performed under direct system manager control. When a disk is added to the shadow set, copy operations take place to make the contents of this new set member identical to that of the other members. Copy operations are transparent to application processing. The new member of the shadow set does not provide any data availability protection until the copy completes.

There is no explicit gatekeeping during the copy operation. Thus, application read and write operations occur in parallel with copy thread reads and writes. As shown in Figure 5, correct results are accomplished by the following algorithm. During the full copy, the shadowing driver processes application write operations in two groups: first, those directed to all source members and second, writes to all full copy targets. The copy thread performs a sequence of read source, compare target, and write target operations on each logical block number (LBN) range until the compare operation succeeds. If an LBN range has such frequent activity that the compare fails many times, SHDRIVER performs a synchronized update. A distributed fence provides a clusterwide boundary between the copied and the uncopied areas of the new member. This fence is used to avoid performing the special full copy mechanisms on application writes to that area of the disk already processed by the copy thread.

This algorithm meets the goal of operational correctness (both the application and the copy thread achieve the proper results with regard to the contents of the shadow set members) and requires no synchronization with the copy thread. Thus, the algorithm achieves maximum application I/O availability during the transient state. Crucial to achieving this goal is the fact that, by design, the copy thread does not perform I/O optimization techniques such as double buffering. The copy operations receive equal service as application I/Os.

#### Merge Operations

The VMS Volume Shadowing Phase II merge algorithm meets the product goals of operational

Figure 4 Shadow Set Write Operation

Note: No synchronization exists between the application and copy operations. I/Os can occur in parallel on different nodes in the cluster. Regardless of how the operations overlap, the correct data is copied to the target.

Figure 5 Full Copy Algorithm

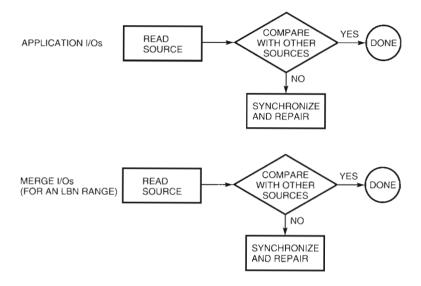

correctness, while maintaining high application I/O availability and minimal synchronization. A merge operation is required when a CPU crashes with the shadow set mounted for write operations. A merge is needed to correct for the possibility of partially completed writes that may have been outstanding to the physical set members when the failure occurred. The merge operation ensures that all members contain identical data, and thus the shadow set virtual unit behaves like a single, highly available disk. It does not matter which data is more recent, only that the members are the same. This satisfies the purpose of shadowing, which is to provide data availability. But since the failure occurred while a write operation was in progress, this consistent shadow set can contain either old or new data. To make sure that the shadow set contains the most recent data, a data integrity technique such as journaling must be employed.

In Phase II shadowing, merge processing is distinctly different from copy processing. The shadow set provides full availability protection during the merge. As a result, merge processing is intentionally designed to be a background activity and to maximize application I/O throughput while the merge is progressing. The merge thread carefully monitors I/O rates and inserts a delay between its I/Os if it detects contention for shared system resources, such as adapters and interconnects.

In addition to maximizing I/O availability, the merge algorithm is designed to minimize synchronization with application I/Os and to identify and correct data inconsistencies. Synchronization takes place only when a rare difference is found. When

an application read operation is issued to a shadow set in the merge state, the set executes the read with merge semantics. Thus, a read to a source and a parallel compare with the other members of the set are performed. Usually the compare matches and the operation is complete. If a mismatch is detected, a sequential repair operation begins. The merge thread scans the entire disk in the same manner as the read, looking for differences. A distributed fence is used to avoid performing merge mechanisms for application reads to that area of the disk already processed by the merge thread. Figure 6 illustrates the merge algorithm.

Note that controller shadowing performs an operation called a merge copy. Although this HSC merge copy operation is designed for the same purpose as the Phase II operation, the approaches differ greatly. An HSC merge copy is triggered when an HSC, not a shadow set, fails and performs a copy operation; the HSC merge copy does not detect differences.

#### Performance Assists

A future version of the shadowing product is intended to utilize controller performance assists to improve copy and merge operations. These assists will be used automatically, if supported by the controllers involved in accessing the physical members of a shadow set.

COPY\_DATA is the ability of a host to control a direct disk-to-disk transfer without the data entering or leaving the host CPU I/O adapters and memory. This capability will be used by full copy processing to decrease the system impact, the

Note: Infrequent synchronization exists between the application and merge operations. I/Os can occur in parallel on different nodes in the cluster. Regardless of how the operations overlap, data integrity is preserved.

Figure 6 Merge Algorithm

bandwidth, and the time required for a full copy. The members of the set and/or their controllers must share a common interconnect in order to use this capability. The COPY\_DATA operation performs specific shadowing around the active, copy LBN range to ensure correctness. This operation involves LBN range-based gatekeeping in the copy target device controller.

Controller write logging is a future capability in controllers, such as HSCs, that will allow more efficient merge processing. Shadowing write operation messages will include information for the controller to log I/Os in its memory. These logs will then be used by the remaining host CPUs during merge processing to determine exactly which blocks contain outstanding write operations from a failed CPU. With such a performance assist, merge operations will take less time and will have less impact on the system.

#### Data Repair and Recovery

As discussed in the Primitives section, data repair operations are triggered by failing reads and are repaired as sequential commands. Digital Storage Architecture (DSA) devices support two primitive capabilities that are key to this repair mechanism. When a DSA controller detects a media error, the block in question is sometimes repaired automati-

cally, thus requiring no shadowing intervention. When the controller cannot repair the data, a spare block is revectored to this LBN, and the contents of the block are marked with a forced error. This causes subsequent read operations to fail, since the contents of the block are lost.

The forced error returned on a read operation is the signal to the shadowing software to execute a repair operation. SHDRIVER attempts to read usable data from another source device. If such data is available, the software writes the data to the revectored block and then returns the data to the application. If no usable data source is available, the software performs write operations with a forced error to all set members and signals the application that this error condition has occurred. Note that a protected system buffer is used for this operation because the application reading the data may not have write access.

A future shadowing product is intended to support SCSI peripherals, which do not have the DSA primitives outlined above. There is no forced error indicator in the SCSI architecture, and the revector operation is nonatomic. To perform shadowing data repair on such devices, we will use the READL/WRITEL capability optionally supported by SCSI devices. These I/O functions allow blocks to be read and written with error correction code (ECC)

data. Shadowing emulates forced error by writing data with an intentionally incorrect ECC. To circumvent the lack of atomicity on the revector operation, a device being repaired is temporarily marked as a full copy target until the conclusion of the repair operation. If the CPU fails in the middle of a repair operation, the repair target is now a full copy target, which preserves correctness in the presence of these nonatomic operations.

#### System Disk

System disk shadow sets presented some unique design problems. The system disk must be accessed through a single bootstrap driver and hence, a single controller type. This access takes place when multihost synchronization is not possible. These two access modes occur during system bootstrap and during a crash dump write.

#### Shadowed Booting

The system disk must be accessed by the system initialization code executing on the booting node prior to any host-to-host communication. Since the boot drivers on many processors reside in ROM, it was impractical to make boot driver modifications to support system disk processing. To solve this problem, the system disk operations performed prior to the controller initialization routine of the system device driver are read-only. It is safe to read data from a clusterwide, shared device without synchronization when there is little or no risk of the data being modified by another node in the cluster. At controller initialization time, shadowing builds a read-only shadow set that contains only the boot member. Once locking is enabled, shadowing performs a variety of checks on the system disk shadow set to determine whether or not the boot is valid. If the boot is valid, shadowing turns the single-member, read-only set into a multimember, writable set with preserved copy states. If this node is joining an existing cluster, the system disk shadow set uses the same set as the rest of the cluster.

#### Crash Dumps

The primitive boot driver uses the system disk to write crash dumps when a system failure occurs. This driver only knows how to access a single physical disk in the shadow set. But since a failing node automatically triggers a merge operation on shadow sets mounted for write, we can use the merge thread to process the dump file. The merge

occurs either when the node leaves the cluster (if there are other nodes present) or later, when the set is reformed. As the source for merge difference repairs, the merge process attempts to use the member to which the dump file was written and propagates the dump file to the remainder of the set. The mechanism here for dump file propagation is best-effort, not guaranteed; but since writing the dump is always best-effort, this solution is considered acceptable.

#### Conclusion

VMS Volume Shadowing Phase II is a state-of-the-art implementation of distributed data availability. The project team arrived at innovative solutions to problems attributable to a set of complex, conflicting goals. Digital has applied for four patents on various aspects of this technology.

#### Acknowledgments

I would like to acknowledge the efforts and contributions of the other members of the VMS shadowing engineering team: Renee Culver, William Goleman, and Wai Yim. In addition, I would also like to acknowledge Sandy Snaman for Fork Thread Locking, Ravindran Jagannathan for performance analysis, and David Thiel for general consulting.

#### References

- 1. N. Kronenberg, H. Levy, W. Strecker, and R. Merewood, "The VAXcluster Concept: An Overview of a Distributed System," *Digital Technical Journal* (September 1987): 7-21.

- W. Snaman, Jr. and D. Thiel, "The VAX/VMS Distributed Lock Manager," *Digital Technical Journal* (September 1987): 29-44.

- 3. W. Snaman, Jr., "Application Design in a VAXcluster System," *Digital Technical Journal*, vol 3. no. 3 (Summer 1991, this issue): 16–26.

### Application Design in a VAXcluster System

VAXcluster systems provide a flexible way to configure a computing system that can survive the failure of any component. In addition, these systems can grow with an organization and can be serviced without disruption to applications. These features make VAXcluster systems an ideal base for developing high-availability applications such as transaction processing systems, servers for network client-server applications, and data sharing applications. Understanding the basic design of VAXcluster systems and the possible configuration options can help application designers take advantage of the availability and growth characteristics of these systems.

Many organizations depend on near constant access to data and computing resources; interruption of these services results in the interruption of primary business functions. In addition, growing organizations face the need to increase the amount of computing power available to them over an extended period of time. VAXcluster systems provide solutions to these data availability and growth problems that modern organizations face.<sup>1</sup>

This paper begins with an overview of VAXcluster systems and application design in such systems and proceeds with a detailed discussion of VAXcluster design and implementation. The paper then focuses on how this information affects the design of applications that take advantage of the availability and growth characteristics of a VAXcluster system.

#### Overview of VAXcluster Systems

VAXcluster systems are loosely coupled multiprocessor configurations that allow the system designer to configure redundant hardware that can survive most types of equipment failures. These systems provide a way to add new processors and storage resources as required by the organization. This feature eliminates the need either to buy nonessential equipment initially or to experience painful upgrades and application conversions as the systems are outgrown.

The VMS operating system, which runs on each processor node in a VAXcluster system, provides a high level of transparent data sharing and independent failure characteristics. The processors interact to form a cooperating distributed operating system. In this system, all disks and their stored files are accessible from any processor as if those files

were connected to a single processor. Files can be shared transparently at the record level by application software.

To provide the features of a VAXcluster system, the VMS operating system was enhanced to facilitate this data sharing and the dynamic adjustment to changes in the underlying hardware configuration. These enhancements make it possible to dynamically add multiple processors, storage controllers, disks, and tapes to a VAXcluster system configuration. Thus, an organization can purchase a small system initially and expand as needed. The addition of computing and storage resources to the existing configuration requires no software modifications or application conversions and can be accomplished without shutting down the system. The ability to use redundant devices virtually eliminates single points of failure.

### Application Design in a VAXcluster Environment

Application design in a VAXcluster environment involves making some basic choices. These choices concern the type of application to be designed and the method used to synchronize the events that occur during the execution of the application. The designer must also consider application communication within a VAXcluster system. A discussion of these issues follows.

#### General Choices for Application Design

This section briefly describes the general choices available to application designers in the areas of client-server computing and data access.

Client-server Computing The VAXcluster environment provides a fine base for client-server computing. Application designers can construct server applications that run on each node and accept requests from clients running on nodes in the VAXcluster system or elsewhere in a wider network.

If the node running a server application fails, the clients of that server can switch to another server running on a surviving node. The new server can access the same data on disk or tape that was being accessed by the server that failed. In addition, the redundancy offered by the VMS Volume Shadowing Phase II software eliminates data unavailability in the event of a disk controller or media failure.<sup>2</sup> The system is thus very available from the perspective of the client applications.

Access to Storage Devices Many application design questions involve how to best access the data stored on disk. One major advantage of the VAXcluster system design is that disk storage devices can be accessed from all nodes in an identical manner. The application designer can choose whether the access is simultaneous from multiple nodes or from one node at a time. Consequently, applications can be designed using either partitioned data access or shared data access.

Using a partitioned data model, the application designer can construct an application that limits data access to a single node or subset of the nodes. The application runs as a server on a single node and accepts requests from other nodes in the cluster and in the network. And because the application runs on a single node, there is no need to synchronize data access with other nodes. Eliminating this source of communication latencies can improve performance in many applications. Also, if synchronization is not required, the designer can make the best use of local buffer caches and can aggregate larger amounts of data for write operations, thus minimizing I/O activity.

An application that uses partitioned data access lends itself to many types of high-performance database and transaction processing environments. VAXcluster systems provide such an application with the advantage of having a storage medium that is available to all nodes even when they are not actively accessing the data files. Thus, if the server node fails, another server running on a surviving node can assume the work and be able to access the same files. For this type of application design, VAXcluster systems offer the performance

advantages of a partitioned data model without the problems associated with the failure of a single server.

Using a shared data model, the application designer can create an application that runs simultaneously on multiple VAXcluster nodes, which naturally share data in a file. This type of application can prevent the bottlenecks associated with a single server and take advantage of opportunities for parallelism on multiple processors. The VAX RMS software can transparently share files between multiple nodes in a VAXcluster system. Also, Digital's database products, such as Rdb/VMS and VAX DBMS software, provide the same data-sharing capabilities. Servers running on multiple nodes of a VAXcluster system can accept requests from clients in the network and access the same files or databases. Because there are multiple servers, the application continues to function in the event that a single server node fails.

#### Application Synchronization Methods

The application designer must also consider how to synchronize events that take place on multiple nodes of a VAXcluster system. Two main methods can be used to accomplish this: the VMS lock manager and the DECdtm services that provide VMS transaction processing support.

VMS Lock Manager The VMS lock manager provides services that are flexible enough to be used by cooperating processes for mutual exclusion, synchronization, and event notification.<sup>3</sup> An application uses these services either directly or indirectly through components of the system such as the VAX RMS software.

DECdtm Services The VMS operating system provides a set of services to facilitate transaction processing. These DECdtm services enable the application designer to implement atomic transactions either directly or indirectly. The services use a two-phase commit protocol. A transaction may span multiple nodes of a cluster or network. The support provided allows multiple resource managers, such as the VAX DBMS, Rdb/VMS, and VAX RMS software products, to be combined in a single transaction. The DECdtm transaction processing services take advantage of the guarantees against partitioning, the distributed lock manager, and the data availability features, all provided by VAXcluster systems.

#### VAXcluster and Networkwide Communication Services

Application communication between different processors in a VAXcluster system is generally accomplished using DECnet task-to-task communication services or other networking software such as the transmission control protocol (TCP) and the internet protocol (IP). Client-server applications or peer-to-peer applications are easy to develop with these services. The services allow processes to locate or start remote servers and then to exchange messages.

Since the individual nodes of a VAXcluster system exist as separate entities in a wider communication network, applications communication inside a VAXcluster system can rely on general network interfaces. Thus, no special-purpose communication services were developed. Applications are simpler to design when they can communicate within the cluster in the same manner in which they communicate with nodes located outside the VAXcluster system.

A DECnet feature known as cluster alias provides a collective name for the nodes in a VAXcluster system. Application software can connect to a node in the cluster using the cluster alias name rather than a specific node name. This feature frees the application from keeping track of individual nodes in the VAXcluster system and results in design simplification and configuration flexibility.

#### VAXcluster Design and Implementation Details

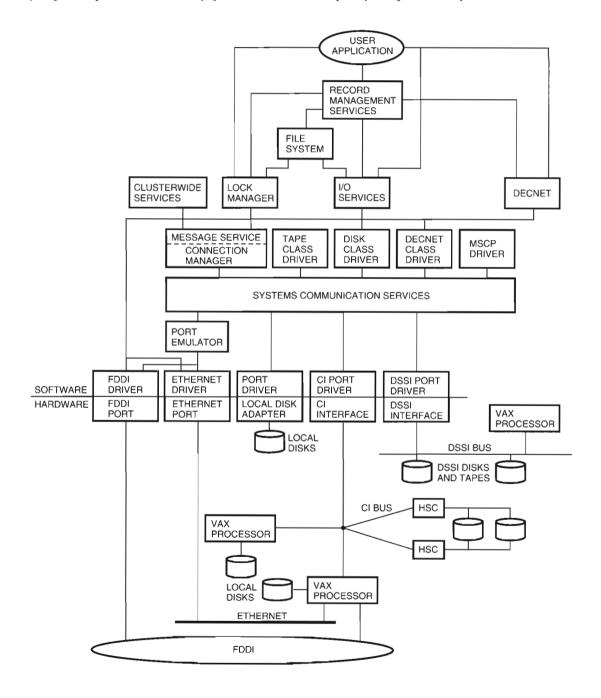

To understand how the design and implementation of a VAXcluster system affects application design, one must be familiar with the basic architecture of such a system, as shown in Figure 1. This section describes the layers, which range from the communication mechanisms to the users of the system.

#### Port Layer

The port layer consists of the lowest levels of the architecture, including a choice of communication ports and physical paths (buses). The VAXcluster software requires at least one logical communication pathway between each pair of processor nodes in the VAXcluster system. Several of the ports utilize multiple physical communication paths, which appear as a single logical path to the VAXcluster software. This redundancy provides better communication throughput and higher availability. If multiple logical paths exist between a pair of nodes, the

VAXcluster software generally selects one for active use and relies on the remaining paths for backup in the event of failure.

The port layer can contain any of the following interconnects:

- Computer Interconnect (CI) bus

- Ethernet

- Fiber distributed data interface (FDDI)

- Digital Storage Systems Interconnect (DSSI) bus

Each bus is accessed by a port (also called an adapter) that connects to the processor node. For example the CI bus is accessed by way of a CI port. The various buses provide a wide spectrum of choices in terms of wire and adapter capacity, number of nodes that can be attached, distance between nodes, and cost.<sup>5</sup>

The CI bus was designed for access to storage and for reliable host-to-host communications. Each CI port connects to two redundant, high-speed physical paths. The CI port dynamically selects one of the two paths for each transmitted message. Messages are received on either path. Thus, two nodes can communicate on one path at the same time that two other nodes communicate on the other. If one physical path fails, the port simply uses the remaining path. The existence of the two physical paths is hidden from the software that uses the CI port services. From the standpoint of the cluster software, each port represents a single logical path to a remote node. Multiple CI ports can be used to provide multiple logical paths between pairs of nodes. An automatic load-sharing feature distributes the load between pairs of ports.

The DSSI bus was primarily designed for access to disk and tape storage. However, the bus has proven an excellent way to connect small numbers of processors using the VAXcluster protocols. Each DSSI port connects to a single high-speed physical path. As in the case of the CI bus, several DSSI ports may be connected to a node to provide redundant paths. (Note that the KFQSA DSSI port is for storage access only and provides no general communication service between nodes.)

Ethernet and FDDI are open local area networks, generally shared by a wide variety of consumers. Consequently, the VAXcluster software was designed to use the Ethernet and FDDI ports and buses simultaneously with the DECnet or TCP/IP protocols. This is accomplished by allowing the Ethernet data link software to control the hardware port. This

software provides a multiplexing function such that the cluster protocols are simply another user of a shared hardware resource.

Each Ethernet and FDDI port connects to a single physical path. There may be more than one port on each processor node. This means that there may be many separate paths between any pair of nodes when multiple ports are used. The port driver software combines the multiple Ethernet and FDDI paths into a single logical path between any pair of nodes. The load is automatically distributed among the various possible physical paths by an algorithm that chooses the best path in terms of adapter capacity and path latency.<sup>6</sup>

Figure 1 VAXcluster System Architecture

#### System Communications Services Layer

The system communications services (SCS) layer of the VAXcluster architecture is implemented in a combination of hardware and software or software only, depending upon the type of port. The SCS layer manages a logical path between each pair of nodes in the VAXcluster system. This logical path consists of a virtual circuit (VC) between each pair of SCS ports and a set of SCS connections that are multiplexed on that virtual circuit. The SCS provides basic connection management and communication services in the form of datagrams, messages, and block transfers over each logical path.

The datagram is a best-effort delivery service which offers no guarantees regarding loss, duplication, or ordering of datagrams packets. This service requires no connection between the communicating nodes. In general, the VAXcluster software makes minimal use of the datagram service.

The message and block transfer services take place over an SCS connection. Consumers of SCS services communicate with their counterparts on remote nodes using these connections. Multiple connections are multiplexed on the logical path provided between each pair of nodes in the VAXcluster system.

The message service is reliable and guarantees that there will be no loss, duplication, or permutation of message sequence on a given connection. The connection will break rather than allow the consumer of the service to perceive such errors.

The block transfer service provides a way to transfer quantities of data directly from the memory of one node to that of another. For CI ports, the port hardware accomplishes the block transfer, thus freeing the host processor to perform other tasks. Some DSSI ports use hardware to copy data and others rely on software to perform this function. Depending on the exact model of an Ethernet or FDDI port, the port software, rather than the hardware, moves the data.

#### System Applications

The next higher layer in the VAXcluster architecture consists of multiple system applications (SYSAPS). These applications provide, for example, access to disks and tapes and cluster membership control. The following sections describe some SYSAPS.

Connection Manager The connection manager serves three major functions. First, the connection manager knows which processor nodes are active

members of the VAXcluster system and which are not. This is accomplished through a concept of cluster "membership." Nodes are explicitly added to and removed from the active set of nodes by a distributed software algorithm. In a VAXcluster system, every processor node must have an open SCS connection to all other processor nodes. Once a booting node establishes connections to all other nodes currently in the VAXcluster system, this node can request admission to the system. When one node is no longer able to communicate with another node, one of the two nodes must be removed from the VAXcluster system.

In a VAXcluster system, all nodes have a consistent view of the cluster membership in the presence of permanent and temporary communication failures. This consistency is accomplished by using a two-phase commit protocol to form the cluster, add new nodes, and remove failed nodes.

The second function provided by the connection manager is an extension of the SCS message service. This extension guarantees that the service will (1) deliver a message to a remote node or (2) remove either the sending node or the receiving node from the cluster. The strong notion of cluster membership provided by the connection manager makes this guarantee possible. The service attempts to deliver the queued messages to remote nodes. If a connection breaks, the service attempts to reestablish communication to the remote node and resend the message. After a period of time specified by the system manager, the service declares the connection irrevocably broken and removes either the sending or the receiving node from the VAXcluster membership. Thus, the service hides all temporary communication failures from its client.

This message service allows users to construct efficient protocols that do not require acknowledgment of messages. The service proved to be a very powerful tool in the design of the VMS lock manager. The delivery guarantees inherent in the service minimize the number of messages required to perform any given locking function, resulting in a corresponding increase in performance. The ability to hide failures by updating cluster membership further simplified the lock manager design and increased performance; this capability enabled the removal of logic used to handle changes in VAXcluster configurations and communication errors from all main lock manager code paths.

The third function of the connection manager is to prevent partitioning of the possible cluster

members. Partitioning of a system exists when separate processing elements function independently. If a system allows data sharing, completely independent processing can result in uncoordinated access to shared resources and lead to data corruption.

In a VAXcluster system, processors communicate and coordinate access to resources by means of a voting algorithm. The system manager assigns a number of votes to each processor node based on the importance of that node. The system manager also informs each node of the total number of possible votes. The algorithm requires that more than half of these votes be present in a VAXcluster system for nodes to function. When the sum of all votes contributed by the members of a VAXcluster system falls below this quorum, the VMS software blocks I/O to mounted devices and prevents the scheduling of processes. As nodes join the cluster, votes are added. Activity resumes once a quorum is reached.

In practice, the connection manager uses two measurements of the number of votes: static and dynamic. The static count of votes is the globally agreed on number of votes contributed by cluster members. This count is created ignoring the state of connections between nodes. The value of the static quorum changes only at the completion of two-phase commit operations, which accomplish a user-requested quorum adjustment in addition to performing the other activities mentioned earlier in this Connection Manager section.

Each node independently maintains the dynamic count. This count represents the sum of all votes contributed by VAXcluster members with which the tallying node has a functional connection. Changes in the dynamic quorum, and not the static quorum, initiate the blockage of process and I/O activity.

To provide configurations with a small number of nodes, e.g., two nodes, the concept of a quorum disk was invented. The system manager assigns a disk to contribute votes to the cluster. A node must be able to access a file on the disk in order to include the votes assigned to that disk in the node's own total. Consequently, a special algorithm is used to access the file. This algorithm ensures that two unrelated nodes cannot both count the quorum disk votes. Doing so could result in partitioned operation.

Mass Storage Control Protocol Server The Mass Storage Control Protocol (MSCP) server allows disks that are attached to one or more VAX processors to be accessed by other processors in the VAXcluster system. Thus, a VAXcluster processor may emulate a multihost disk controller by accepting and processing I/O requests from other nodes and accessing the disk indicated by the request. The server can process multiple commands simultaneously and also performs fragmentation of commands if there is not enough system buffer space to accommodate the entire amount of data at one time.

Hierarchical Storage Controllers, Local Controllers, and RF-series Integrated Storage Elements Hierarchical storage controller (HSC) servers are specialized devices that perform MSCP serving of RA-series disk drives and TA-series tape drives in a VAXcluster system. HSC servers connect directly to the CI bus. In addition to providing the host with access to the storage media, HSC servers accomplish performance optimizations such as seekordering and request fragmentation based on real-time head position information. The local disk controllers attached to the RA- and TA-series storage devices perform the same function for a single host processor. The RF-series integrated storage elements (ISEs) attach to a DSSI bus. Each of these disk storage devices performs its own command queuing and optimization without using a dedicated controller.

Disk Class Driver The disk class driver allows access to disks served by an MSCP server, an HSC controller, a local Digital Storage Architecture (DSA) controller, or attached to a DSSI bus. This driver provides a command queuing function that allows a disk controller to have multiple outstanding commands which can be used to provide seek, rotation, and other performance optimizations. To handle temporary communication interruptions, the driver restarts commands as needed.

VAXcluster systems can be configured so that all disks are accessed by way of redundant paths for increased availability. The way in which this is accomplished depends on the type of disk and the disk controller.

RF-series disks contain integrated controllers that connect to a single DSSI storage bus. This bus can be accessed by up to two VAX processors. Each VAX processor can then serve the disks to all other nodes in the VAXcluster system. Thus, two paths are provided to each disk.

RA-series disks connect to up to two storage controllers. These controllers can be either (1) local adapters attached directly to a single processor node or (2) HSC controllers located on the CI bus. Disks connected to local adapters can be served to other nodes of the VAXcluster system. Disks located on an HSC controller can be directly accessed by processors that are not on that bus. Thus, the use of multiple controllers when combined with disk serving provides at least two paths to a disk from every node in the VAXcluster system.

Since many paths exist to gain access to a disk, the disk class driver chooses which path to use when a disk is initially mounted by a node. If the path to the disk becomes inoperative, the disk class driver locates another path and begins to use it. Server load and type of path, i.e., local or remote, are considered when selecting the new path. This reconfiguration is totally transparent to the end user of the disk I/O service.

Tape Class Driver The tape class driver performs functions in a VAXcluster system similar to those of the disk class driver by providing access to tapes located on HSC controllers, local controllers, and DSSI buses.

### VMS Components Layered on Top of SYSAPs

The SYSAPs provide basic services that other VMS components use to provide a wide range of VAXcluster features.

Volume Shadowing The volume shadowing product allows multiple disks to be utilized as a single, highly available disk. Volume shadowing provides transparent access to the data in the event of disk media or controller failures, media degradation, and communication failures.<sup>2</sup> The shadowing layer works in conjunction with the disk class driver to accomplish this task. With the advent of VMS Volume Shadowing Phase II, disk shadowing is extended to many new configurations.

Lock Manager The VMS lock manager is a system service that provides a distributed synchronization function used by many components of the VMS operating system, including volume shadowing, the file system, VAX RMS software, and the batch/print system. Application programs can also use the lock manager directly.

The lock manager provides a name space that is truly clusterwide. Cooperating processes can request locks on a specific resource name. The lock manager either grants or denies these requests. Processes can also queue requests. The lock manager services allow processes to coordinate the means of access to physical resources or simply provide a communication pathway between processes. Processes can use the service for such tasks as mutual exclusion, event notification, and server failure detection.2.7 The lock manager uses the communication service provided by the connection manager to minimize the message count for a given operation and to simplify the design by eliminating the need to consider changes in cluster membership from all main paths of operation.

Process Control Services The VMS process control system services take advantage of VAXcluster systems. Applications can use these services to alter process states on remote nodes and to collect information about those processes. In the future, it is likely that other services will be extended to make optimal use of VAXcluster capabilities.

*File System* The VMS file system (XQP) allows disk devices to be accessed by multiple nodes in a VAXcluster system. The file system uses the lock manager to coordinate disk space allocation, buffer caches, modification of file headers, and changes to the directory structure.<sup>8</sup>

Record Management Services The VAX RMS software allows the sharing of file data by processes running on the same or multiple nodes. The software uses the lock manager to coordinate access to files, to record data within files, and to global buffers.

Batch/Print System The batch/print system allows users to submit batch or print jobs on one node and run them on another. This system provides a form of load distribution, i.e., generic batch queues can feed executor queues on each node. Jobs running on a failed node can be restarted automatically on another node in the VAXcluster system.

### An Application Constructed Using VAXcluster Mechanisms

The VMS software build process is an example of how these mechanisms can be used to benefit application design. The VMS software build is broken down into various phases such as fetch sources, compile, and link. The phases must execute in a given order but are otherwise independent. Each phase can be restarted from the beginning if there is an error. Each major component of the VMS operating system is processed separately during each of the phases. All sources reside on a shared disk to which all nodes of the VAXcluster system have access; the output disk is shared by all nodes also. A master data file describes the phases and the components. For a given phase, the actions required for each component are fed into a generic batch queue. This queue feeds the jobs into work queues on multiple nodes, resulting in the execution of many jobs in parallel. When all jobs of a phase have completed, the next phase starts. If a node fails during the execution of a job, that job is restarted automatically on another node either from the beginning or from a checkpoint in the job. This use of shared disks and batch queues provides great parallelism and reliability in the VMS build process.

### The Impact of VAXcluster Design and Implementation on Applications

This section discusses how multiple communication paths, membership changes, disk location and availability, controller selection, disk and tape path changes, and disk failure impact application design.

#### Multiple Communication Paths

VAXcluster software components are able to take advantage of multiple communication paths between nodes. For greatest availability, there should be at least two physical paths between each pair of nodes in a VAXcluster system.<sup>6</sup>

#### Membership Changes

VAXcluster membership changes involve several distinct phases with slight variations depending upon whether a node is being added or removed. Adding a node to a VAXcluster system is the simplest case because it involves reconfiguration. There is a further simplification in that nodes are only added one at a time. A booting node petitions a member of an existing cluster for membership. This member then describes the booting node to all other member nodes and vice versa. In this way, it is determined that the booting node is in communication with all members of the cluster. The connection manager then adds the new node to the cluster using a two-

phase commit protocol to ensure a consistent membership view from all nodes.

Removing a node is more complicated because both failure detection and reconfiguration must take place. In many cases, there may be multiple simultaneous failures of nodes and communication paths. The view of what nodes are members and which paths are functional may be very different from each node. Additionally, new failures may occur while the cluster is being reconfigured.