## VARIAN 620 TRAINING MANUAL

varian data machines/a varian subsidiary © 1972

98 A 9902 504 JANUARY 1973

This manual is intended for training purposes only. For detailed information, refer to the applicable document for the system you are using.

## TABLE OF CONTENTS

# CHAPTER I COMPUTER FUNDAMENTALS

| Section | n 1 Introduction                    | 1-1 |

|---------|-------------------------------------|-----|

| 1.1     | General Description                 | 1-1 |

| 1.2     | Computer Concepts                   | 1-2 |

|         | 1.2.1 Central Processing Unit (CPU) | 1-2 |

|         | 1.2.2 Memory                        | I-3 |

|         | 1.2.3 Input Unit                    | 1-3 |

|         | 1.2.4 Output Unit                   |     |

| Section | n 2 Numerical Analysis              | 1-4 |

| 2.1     | Introduction                        | 1-4 |

|         | Square Root Extraction              |     |

|         | CHAPTER II<br>PROGRAMMING           |     |

| Section |                                     |     |

| 1.1     | Communication With a Computer       |     |

| 1.2     | Mnemonics                           |     |

| 1.3     | Numerical Code                      |     |

| 1.4     | Instruction Set                     |     |

| 1.5     | Preparing the Program               | I-2 |

| Section | n 2 Flow-Chartingl                  | 1-3 |

| 2.1     | Introduction                        |     |

| 2.2     | Notationl                           |     |

| 2.3     | Symbols                             | 1-7 |

|         | 2.3.1 Functions                     |     |

|         | 2.3.2 Decisions                     |     |

|         | 2.3.3 Input/Output                  |     |

|         | 2.3.4 Start and StopII-             |     |

|         | 2.3.5 Fixed Connectors              | 10  |

| 2.4   | A Sim  | nple Flow Chart                      |       |

|-------|--------|--------------------------------------|-------|

|       | 2.4.1  | Substitution                         | II-12 |

|       | 2.4.2  | Subroutines                          | II-13 |

|       | 2.4.3  | Assertions                           | II-14 |

| 2.5   | A Mo   | re Complicated Flow Chart            | II-14 |

| Sacti | ion 3  | Machine Language Preparation         | 11.17 |

| 3.1   |        | duction                              |       |

| 3.2   |        | iction Repertoire                    |       |

| J.2   | 3.2.1  | Instruction Types                    |       |

|       | 3.2.2  | Addresses                            |       |

|       | 3.2.3  | •                                    |       |

| 3.3   |        | le Programs                          |       |

| 3.4   | •      | ine Language                         |       |

| 3.5   |        | ng                                   |       |

| 3.6   | •      | ing                                  |       |

| 0.0   | 3.6.1  | O .                                  |       |

|       | 3.6.2  |                                      |       |

|       | 3.6.3  |                                      |       |

| 3.7   |        | utines                               |       |

| 3.8   |        | g                                    |       |

|       |        | •                                    |       |

| Secti | on 4   | Programming in Assembly Language     | II-39 |

| 4.1   | DAS /  | Assembler                            | II-39 |

|       | 4.1.1  | DAS 4KA                              | II-39 |

|       | 4.1.2  | DAS 8KA                              | II-40 |

|       | 4.1.3  | DAS MR                               | II-40 |

|       | 4.1.4  | Stand-Alone MR                       | 11-40 |

| 4.2   | DAS S  | Source Language                      | 11-40 |

| 4.3   | Stater | nents                                |       |

|       | 4.3.1  | Statement Format                     | II-41 |

|       | 4.3.2  | Label Field                          |       |

|       | 4.3.3  | Operation Field                      | II-41 |

|       | 4.3.4  | Variable Field                       | II-42 |

|       | 4.3.5  | Comment Field                        | II-42 |

|       | 4.3.6  | Comment Statements                   | II-42 |

|       | 4.3.7  | Blank Statements                     | 11-42 |

| 4.4   | Progra | amming in Symbolic Assembly Language | II-43 |

# CHAPTER III COMPUTER OPERATION

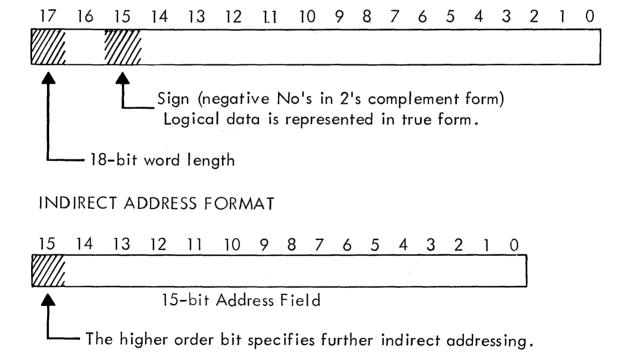

| Sectio | n 1 Word Formats                                        | 11-1 |

|--------|---------------------------------------------------------|------|

| 1.1    | Introduction1                                           | 11-1 |

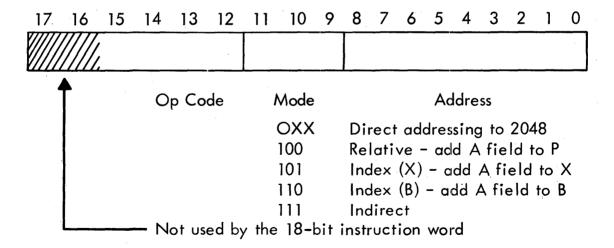

| 1.2    | Single-Word Instructions                                | 11-2 |

|        | 1.2.1 Addressable                                       | II-2 |

|        | 1.2.2 Nonaddressable                                    | II-3 |

| 1.3    | Two-Word Instructions                                   | 11-4 |

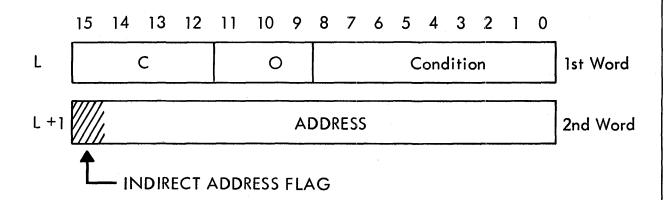

|        | 1.3.1 Jump, Jump and Mark, and Execute Instructions     | 11-4 |

|        | 1.3.2 Memory In/Out Instructions                        | 11-5 |

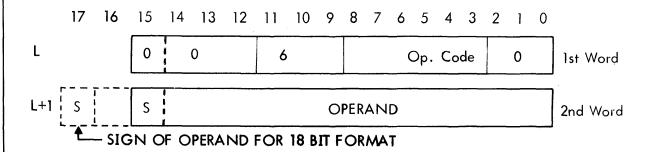

|        | 1.3.3 Immediate Instructions                            | 11-5 |

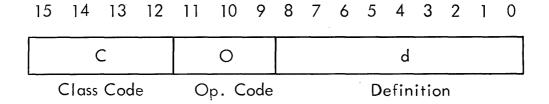

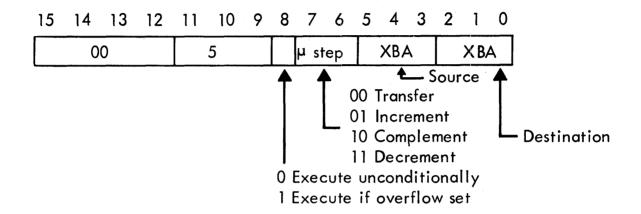

| 1.4    | MACRO-Instructions                                      | 11-6 |

| 1.5    | Instruction List                                        | 11-6 |

| Sectio | n 2 Paper Tape Formats                                  | 11-8 |

| 2.1    | Source Tape Format                                      | 11-8 |

| 2.2    | Bootstrap Format                                        | 11-8 |

| 2.3    | Binary Object (Program Object) Formatl                  | 11-8 |

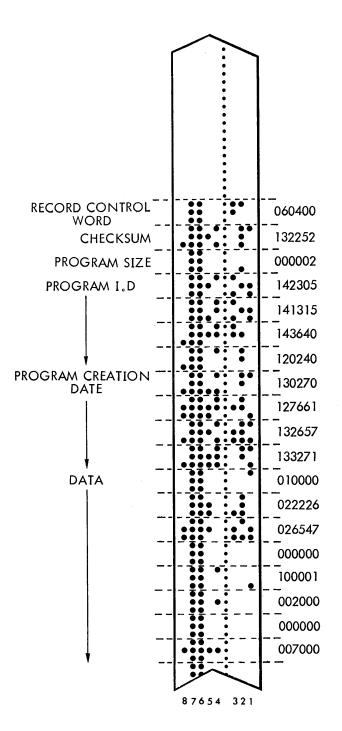

| 2.4    | MOS Relocatable Object FormatIII                        | -12  |

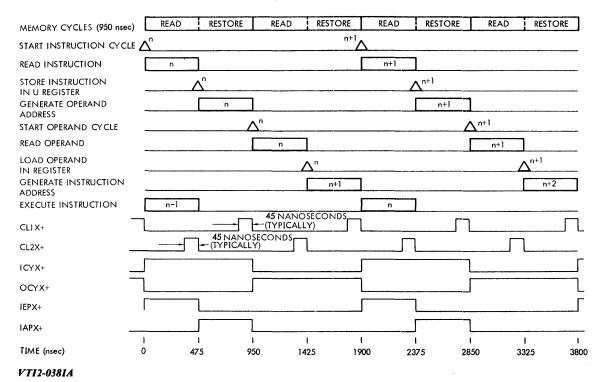

| Sectio | n 3 Operating Sequences for 620/i, 620/L                | -14  |

| 3.1    | Access Operand in MemoryIII                             |      |

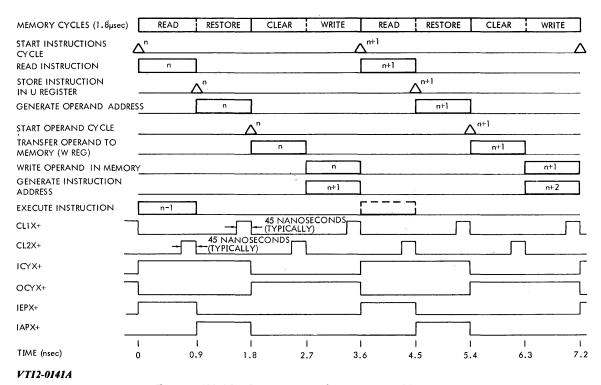

| 3.2    | Store Operand in MemoryIII                              | -17  |

| 3.3    | Indirect Operand AccessIII                              | -17  |

| Sectio |                                                         |      |

| 4.1    | ErrorsIII                                               | -19  |

| 4.2    | MistakesIII                                             |      |

| 4.3    | MalfunctionsIII                                         | -21  |

|        | 4.3.1 Diagnostic Routines for Corrective MaintenanceIII |      |

|        | 4.3.2 Diagnostic Routines for Preventive MaintenanceIII | -21  |

|        | CHAPTER IV                                              |      |

|        | 620 COMPUTER SYSTEMS                                    |      |

| Sectio |                                                         |      |

| 1.1    | Introduction                                            | ٧-1  |

| 1.2   | Switch | es and Indicators                        | IV-6  |

|-------|--------|------------------------------------------|-------|

|       | 1.2.1  | Displays                                 | IV-6  |

|       | 1.2.2  | Controls                                 | IV-8  |

| 1.3   | Manua  | al Operation                             | IV-10 |

|       | 1.3.1  | Power Control                            | IV-10 |

|       | 1.3.2  | Manual Program Entry and Execution       | IV-11 |

|       | 1.3.3  | Instruction Repeat                       |       |

|       | 1.3.4  | SENSE Switches                           | IV-12 |

| 1.4   | Organ  | ization                                  | IV-12 |

|       | 1.4.1  | Memory                                   | IV-12 |

|       | 1.4.2  | Control                                  | IV-14 |

|       | 1.4.3  | Arithmetic/Logic                         | IV-14 |

|       | 1.4.4  | Input/Output                             | IV-15 |

|       | 1.4.5  | Bus Structure                            | IV-15 |

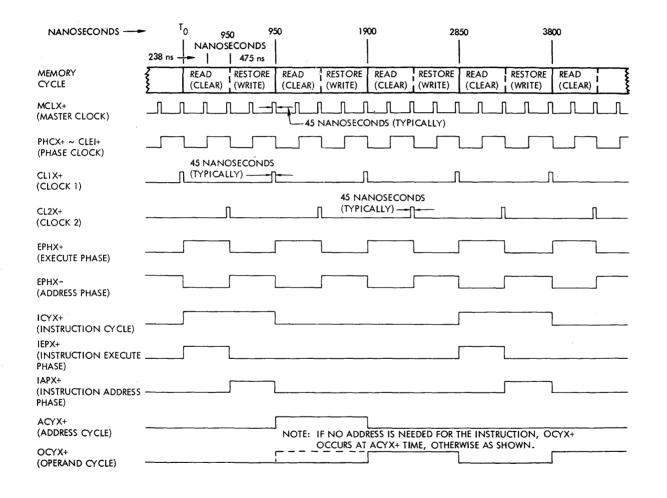

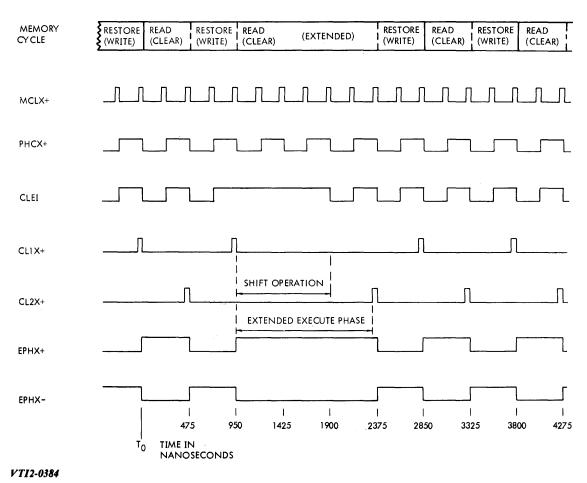

| 1.5   | Timing | <b>3</b>                                 | IV-16 |

|       | 1.5.1  | Clocks                                   | IV-16 |

|       | 1.5.2  | Clock Modifiers                          | IV-18 |

|       | 1.5.3  | Sequence Control                         | IV-19 |

| 1.6   | Inform | ation Transfer                           | IV-21 |

|       | 1.6.1  | P Register to Memory                     | IV-21 |

|       | 1.6.2  | Memory to U Register                     | IV-21 |

|       | 1.6.3  | U Register to Memory                     | IV-21 |

|       | 1.6.4  | Memory to R Register                     | IV-22 |

|       | 1.6.5  | Adder to Operation Registers             | 1V-22 |

|       | 1.6.6  | Operation Registers to Memory            | IV-22 |

|       | 1.6.7  | Memory to Operation Registers            | IV-22 |

|       | 1.6.8  | Input to Memory                          | IV-22 |

|       | 1.6.9  | Output from Memory                       | IV-23 |

|       | 1.6.10 | Input to Operation Registers             | IV-23 |

|       | 1.6.11 | Output from Operation Registers          | IV-23 |

|       | 1.6.12 | Operation Register to Operation Register | IV-23 |

| 1.7   | Decod  | ing                                      | IV-23 |

|       | 1.7.1  | Operation Code Decoding                  | IV-24 |

|       | 1.7.2  | M Field Decoding                         | IV-24 |

| Secti | on 2   | 620/f, 620/f-100 System                  | IV-30 |

| 2.1   | Introd | uction                                   | IV-30 |

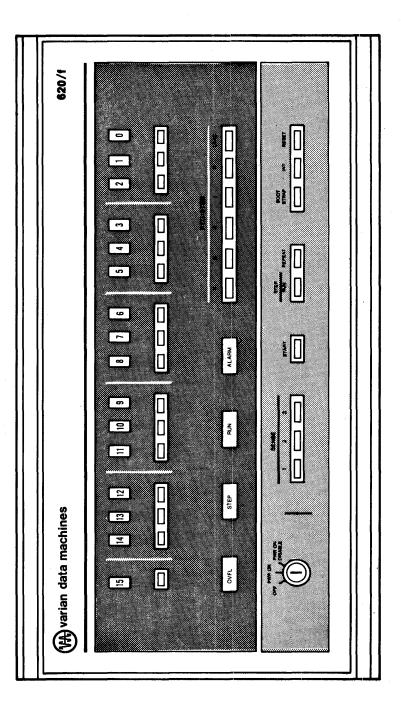

| 2.2 | Switch | ies and Indicators                             | 1V-37 |

|-----|--------|------------------------------------------------|-------|

|     | 2.2.1  | Power Switch                                   | IV-37 |

|     | 2.2.2  | STEP/RUN Switch and STEP and RUN Indicators    | IV-39 |

|     | 2.2.3  | BOOTSTRAP Switch                               | IV-39 |

|     | 2.2.4  | START Switch                                   | IV-40 |

|     | 2.2.5  | REGISTER Switches                              | IV-40 |

|     | 2.2.6  | Register Entry Switches and Display Indicators | IV-40 |

|     | 2.2.7  | LOAD Switch                                    |       |

|     | 2.2.8  | REPEAT Switch                                  | IV-42 |

|     | 2.2.9  | SENSE Switches                                 | IV-42 |

|     | 2.2.10 | INT (Interrupt) Switch                         | IV-42 |

|     | 2.2.11 | RESET Switch                                   | 1V-43 |

|     | 2.2.12 | OVFL (Overflow) Indicator                      | IV-43 |

|     | 2.2.13 | ALARM Indicator                                | IV-43 |

| 2.3 | Manua  | al Operation                                   | IV-43 |

|     | 2.3.1  | Loading Into Sequential Memory Addresses       | IV-43 |

|     | 2.3.2  | Displaying From Sequential Memory Addresses    | IV-44 |

|     | 2.3.3  | Manual Execution of Stored Programs            | IV-44 |

|     | 2.3.4  | Manual Repetition of Instructions              | IV-45 |

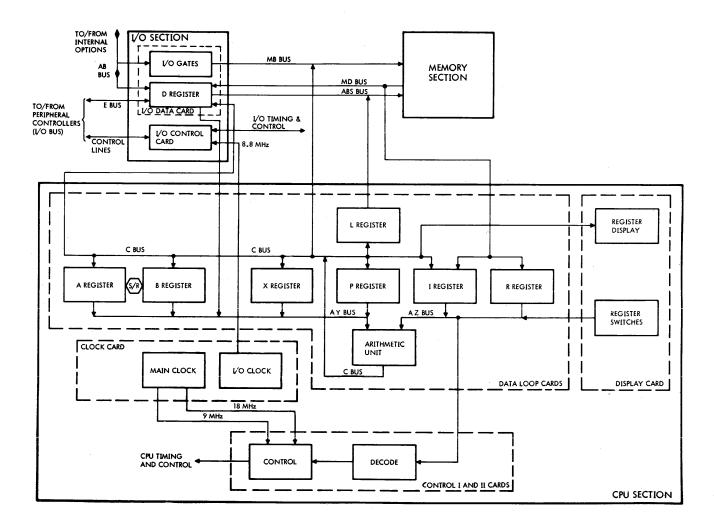

| 2.4 | Organi | ization                                        | IV-45 |

|     | 2.4.1  | Control Section                                | IV-45 |

|     | 2.4.2  | Decoding Section                               | IV-45 |

|     | 2.4.3  | Arithmetic Unit                                | IV-45 |

|     | 2.4.4  | Operation Registers                            | IV-47 |

|     | 2.4.5  | Auxiliary Registers                            | IV-47 |

|     | 2.4.6  | Data Switch Section                            | IV-48 |

|     | 2.4.7  | Register Entry Switches/Display Indicators     | IV-48 |

|     | 2.4.8  | Shift-and-Rotate Circuit                       | IV-48 |

|     | 2.4.9  | Internal Buses                                 | IV-48 |

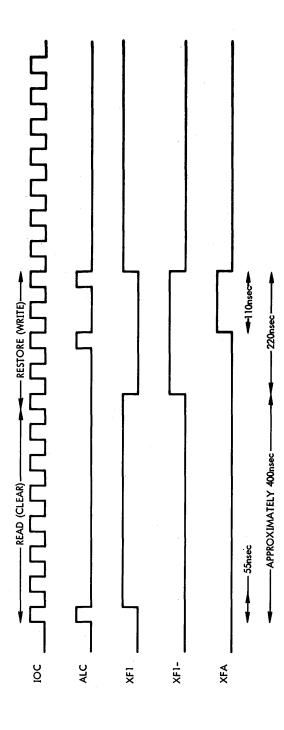

| 2.5 | Timing | g                                              | IV-49 |

|     | 2.5.1  | Clocks                                         | IV-49 |

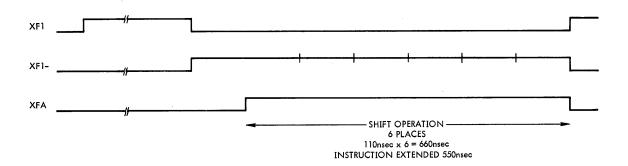

|     | 2.5.2  | Clock Modifiers                                | IV-51 |

|     | 2.5.3  | Sequence Control                               | IV-52 |

| 2.6 | Inform | nation Transfer                                |       |

|     | 2.6.1  | P Register to Memory                           | IV-53 |

|     | 2.6.2  | Memory to I Register                           | IV-53 |

|     | 2.6.3  | I Register to Memory                           | IV-53 |

|     |        |                                                |       |

| 2.6.4   | Memory to R Register                     | IV-55 |

|---------|------------------------------------------|-------|

| 2.6.5   | Arithmetic Unit to Operation Registers   |       |

| 2.6.6   | Operation Registers to Memory            |       |

| 2.6.7   | Memory to Operation Registers            | IV-56 |

| 2.6.8   | Input to Memory                          |       |

| 2.6.9   | Output from Memory                       | IV-56 |

| 2.6.10  | Input to Operation Registers             | IV-56 |

|         | Output from Operation Registers          |       |

|         | Operation Register to Operation Register |       |

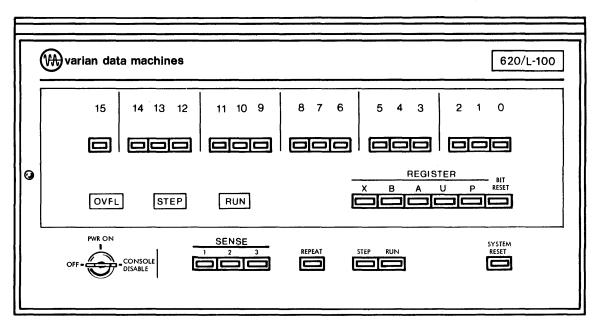

| Section | n 3 620/L-100 Systems                    | IV-57 |

| 3.1     | Introduction                             | IV-57 |

| 3.2     | System Operation                         | IV-62 |

| 3.3     | Manual Operations                        |       |

| 3.4     | Central Processing Unit                  | IV-69 |

CHAPTER V LOGIC DESCRIPTIONS

## LIST OF ILLUSTRATIONS

| 1-1    | Typical Computer System                              | l-2    |

|--------|------------------------------------------------------|--------|

| 11-1   | Typical Flow Chart                                   | 11-4   |

| 11-2   | Flow Chart Symbols                                   | 11-5   |

| 11-3   | Flow Chart for $T = AX^2 + BX \times X \sin 0 \dots$ | II-15  |

| 11-4   | Flow Chart for a Positive and Negative Number Count  | 11-25  |

| 11-5   | Count of Positive Numbers                            | II-31  |

| 11-6   | Loop Program                                         | II-32  |

| 11-7   | Add a Table of Three Numbers                         | II-34  |

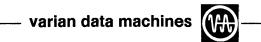

| 11-8   | Subroutines                                          | 11-38  |

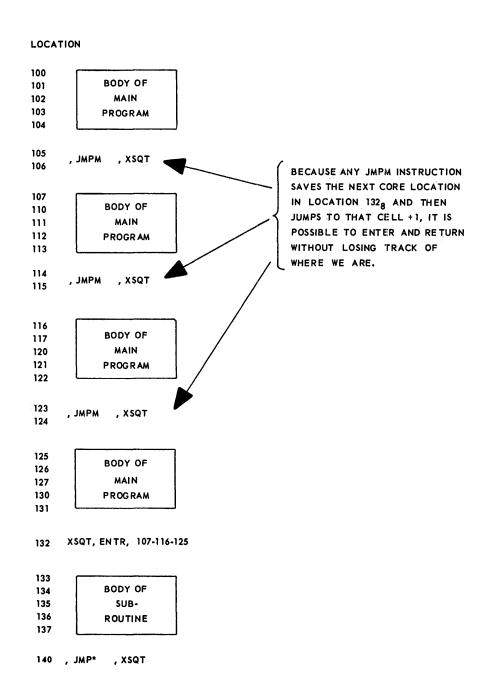

| 11-9   | Example I, Coding Form                               | 11-44  |

| II-10  | Example I, Assembly Listing                          | 11-46  |

| 11-11  | Example J, Coding Form                               |        |

| II-12  | Example J, Assembly Listing                          | II-51  |

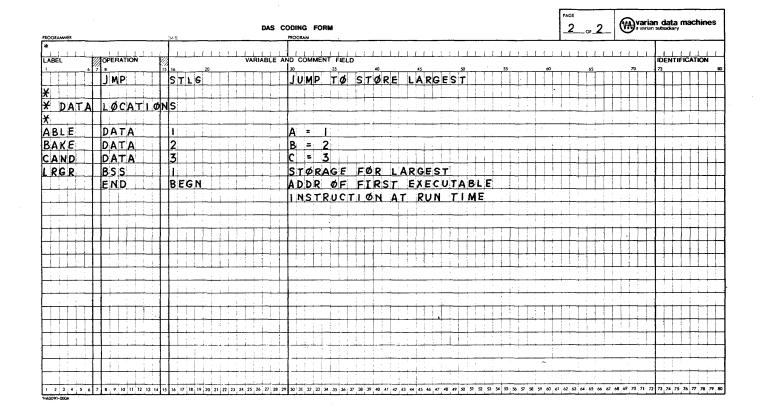

| II-13  | Example K, Coding Form                               | 11-55  |

| 11-14  | Example K, Assembly Listing                          | 11-56  |

| II-15  | Example L, Coding Form                               | 11-58  |

| II-16  | Example L, Assembly Listing                          | II-59  |

| III-1  | Formats for Data Words and Indirect Addresses        |        |

| III-2  | Single-Word Instruction Format                       | III-2  |

| III-3  | Single-Word Nonaddressable Instructions              | III-3  |

| 111-4  | Two-Word Instruction Format                          | 111-4  |

| 111-5  | Immediate Instruction Format                         |        |

| III-6  | MACRO-Command Format                                 | III-6  |

| 111-7  | 620 Series Instruction List                          | 111-7  |

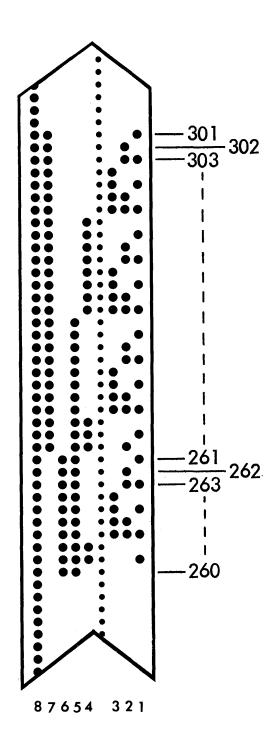

| 111-8  | Source Tape Format                                   | 111-9  |

| 111-9  | Bootstrap Format                                     | III-10 |

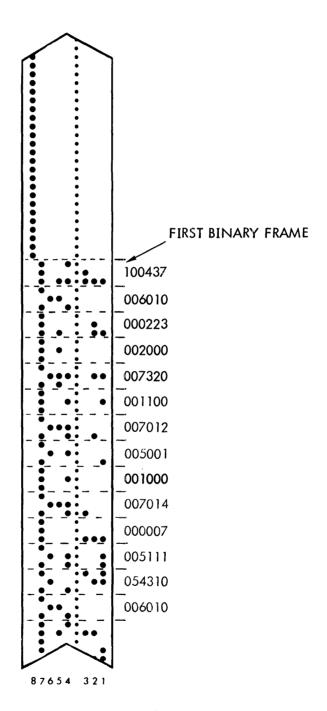

| III-10 | Binary Object Format                                 | III-11 |

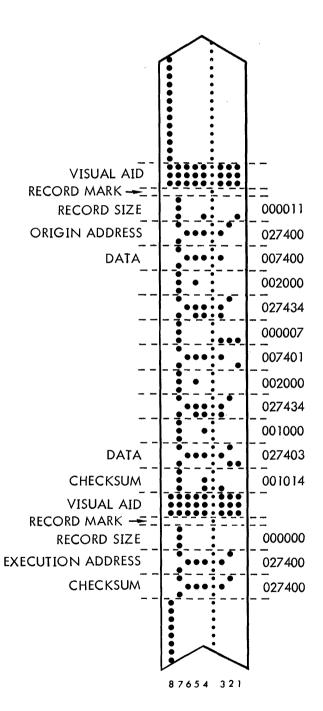

| III-11 | MOS Relocatable Object Format                        |        |

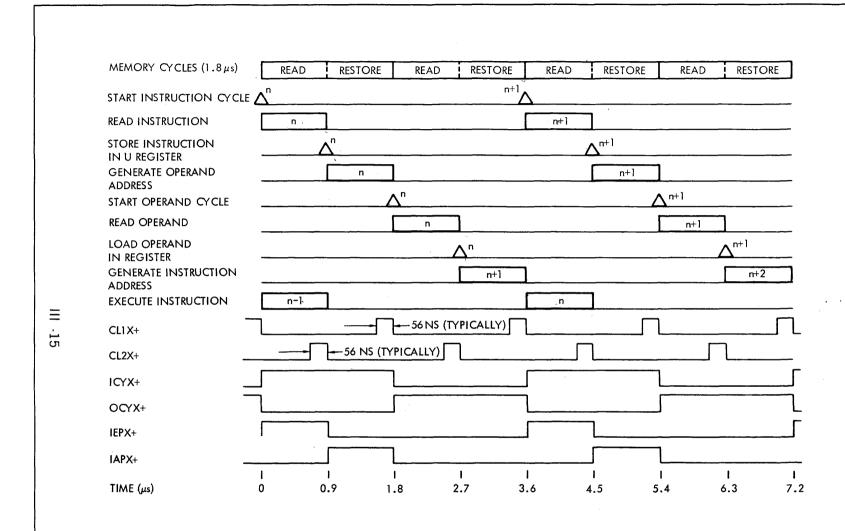

| III-12 | Operand Access from Memory Sequence                  | III-15 |

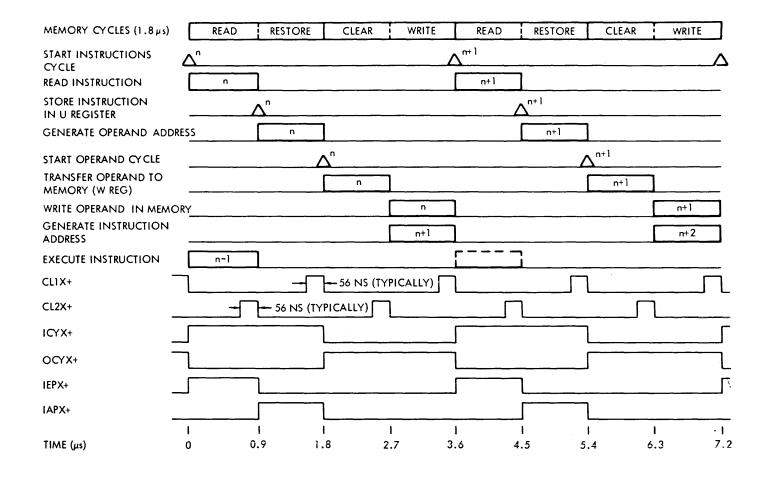

| III-13 | Operand Storage in Memory Sequence                   | III-16 |

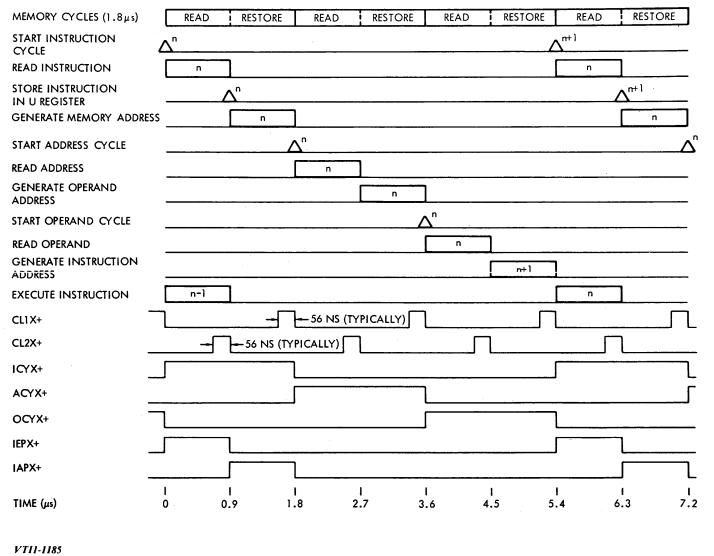

| III-14 | Indirect Operand Access Sequence                     | III-18 |

|        |                                                      |        |

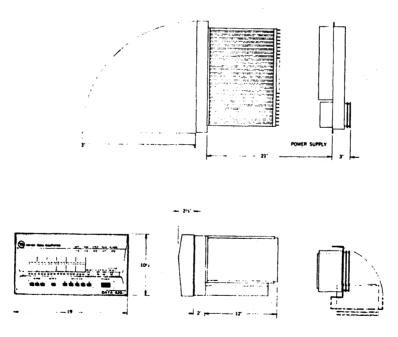

| IV-1         | 620/i Outline                                                                | IV-6               |

|--------------|------------------------------------------------------------------------------|--------------------|

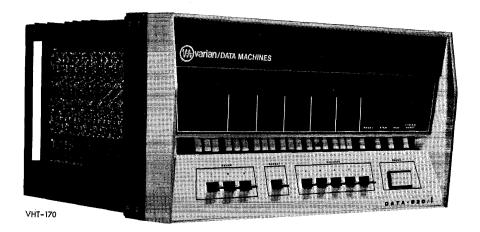

| IV-2         | 620/i Control Console                                                        | 1V-7               |

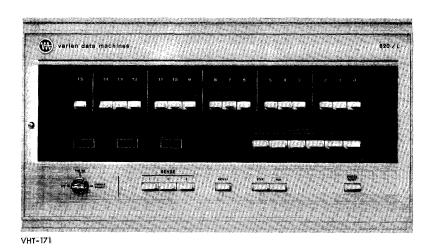

| IV-3         | 620/L Control Console                                                        | IV-7               |

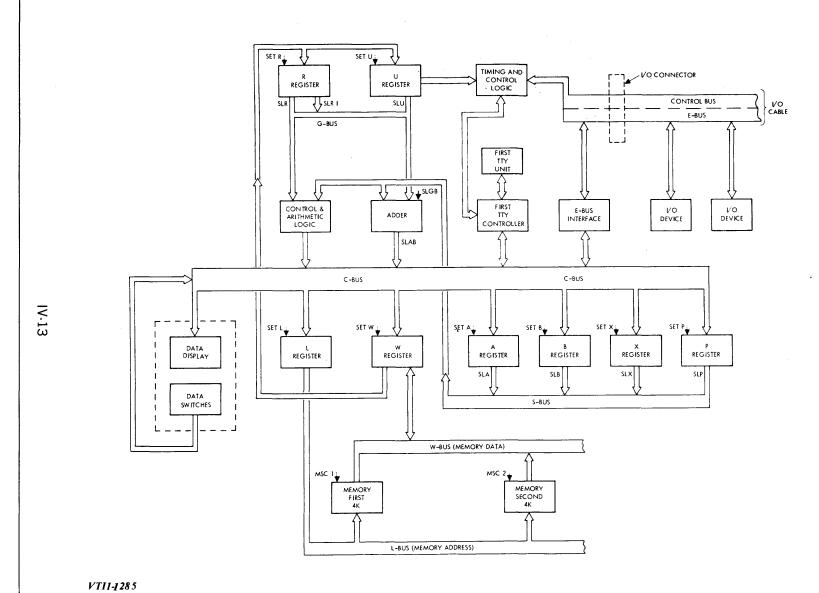

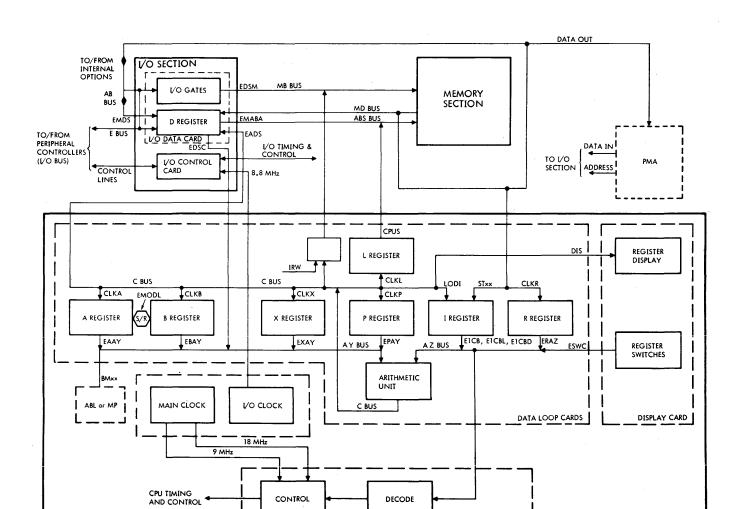

| IV-4         | 620/i Organization                                                           | .IV-13             |

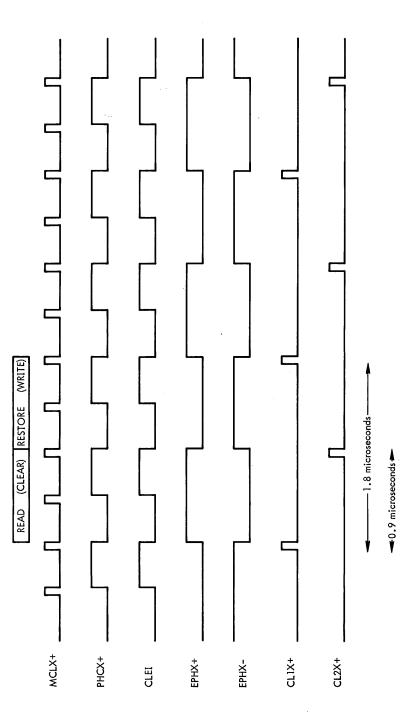

| IV-5         | Basic Timing Clocks                                                          | .IV-17             |

| IV-6         | Example of a Modified Clock Sequence                                         | .IV-10             |

| IV-7         | Data 620/L Organization                                                      | .IV-21             |

| IV-8         | 620/f Computer Control Panel                                                 | .1V-38             |

| IV-9         | 620/f Computer Functional Organization                                       | .1V-46             |

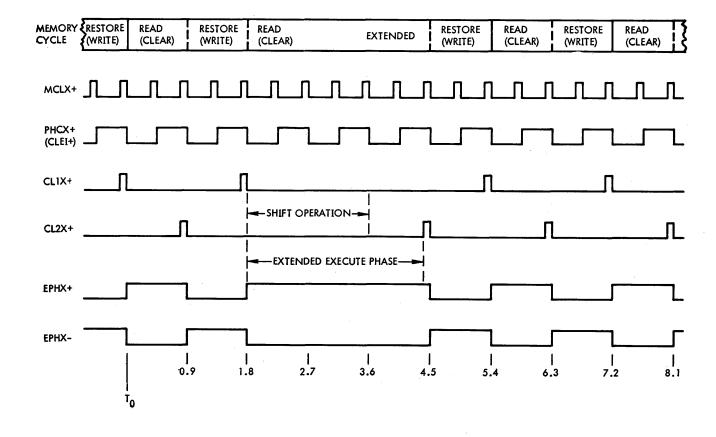

| IV-10        | Basic Timing Clocks                                                          | .1V-50             |

| IV-11        | Example of a Modified Clock Sequence                                         | .1V-53             |

| IV-12        | 620/f Organization                                                           | .1V-54             |

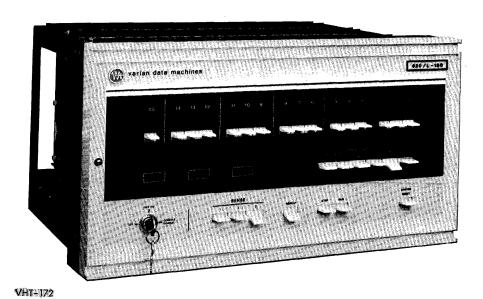

| IV-13        | Varian 620/L-100 Mainframe                                                   | . IV-61            |

| IV-14        | Varian 620/L-100 Control Panel                                               |                    |

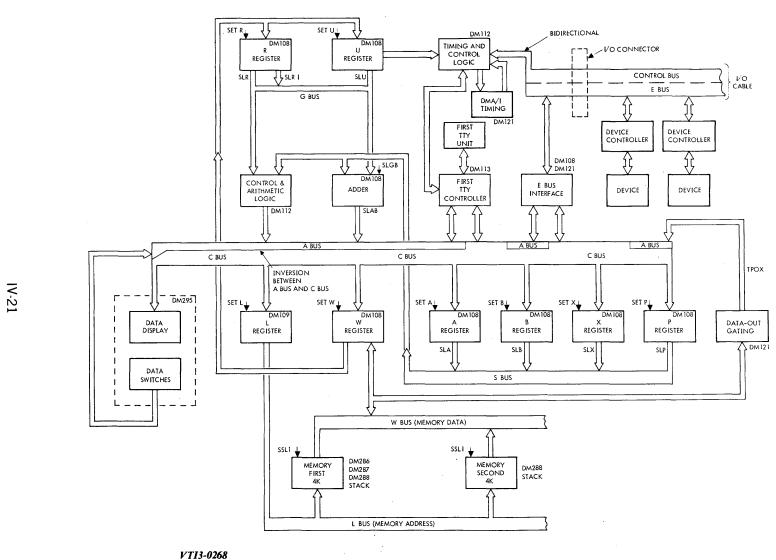

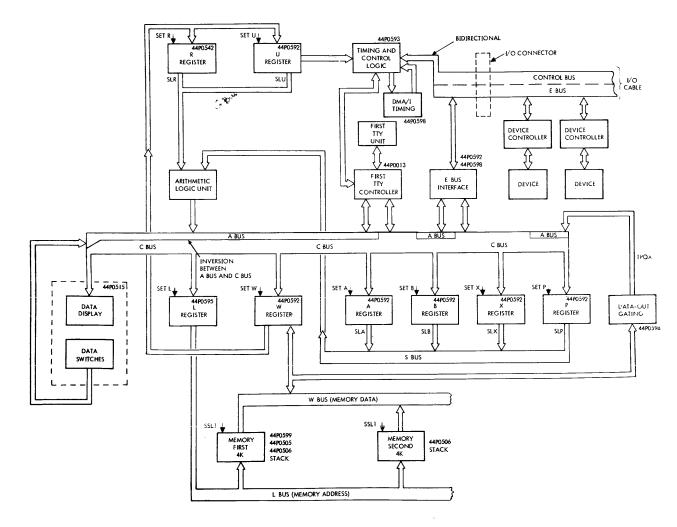

| IV-15        | Varian 620/L-100 Computer Organization                                       | . IV-70            |

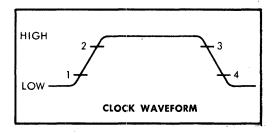

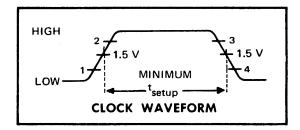

| IV-16        | Basic Clock Waveforms                                                        | . IV-79            |

| IV-17        | Example of a Modified Clock Sequence                                         | . IV-81            |

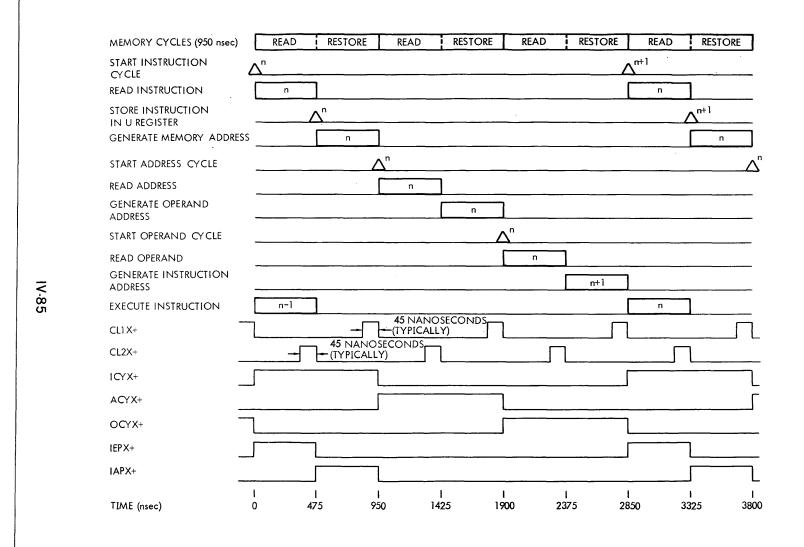

| IV-18        | Accessing on Operand in Memory                                               | . IV-82            |

| IV-19        | Storing an Operand in Memory                                                 | . IV-83            |

| IV-20        | Accessing an Operand Indirectly                                              | . IV-85            |

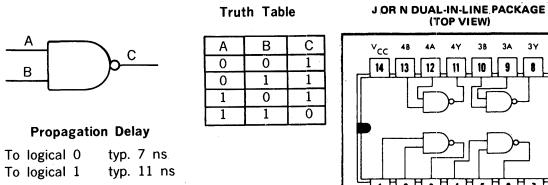

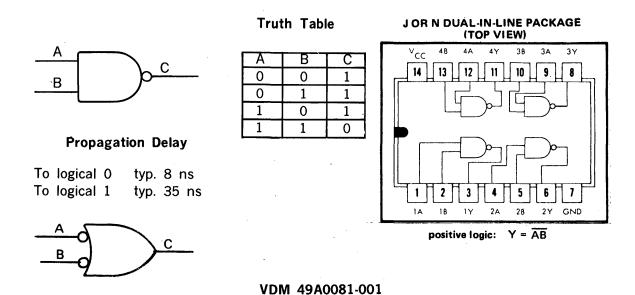

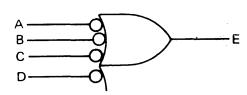

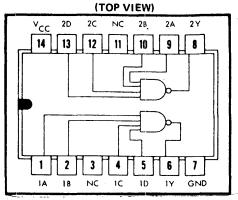

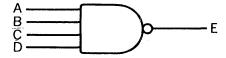

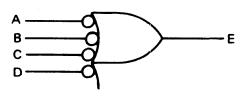

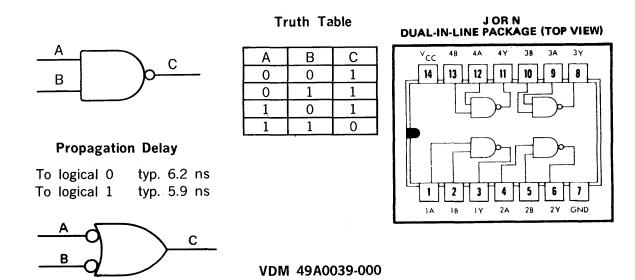

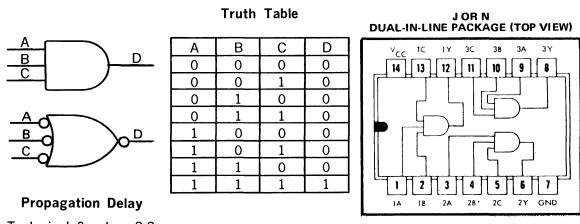

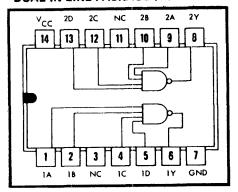

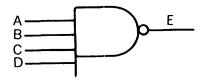

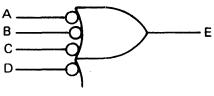

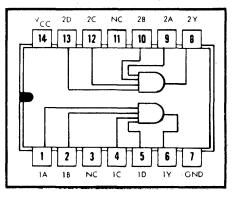

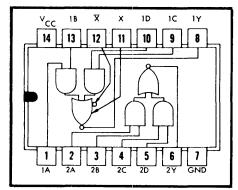

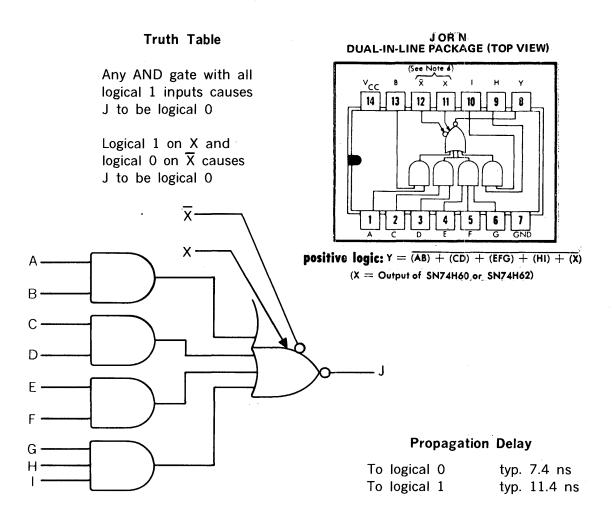

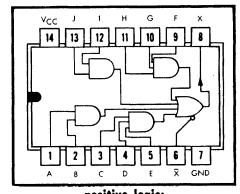

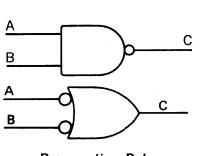

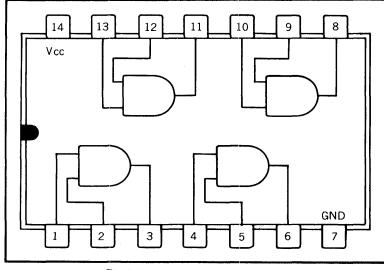

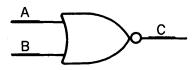

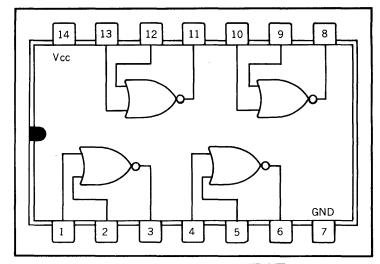

| V-1<br>V-2   | Quadruple 2-Input NAND Gate (SN7400N, 7400PC, N7400A)                        | V-2                |

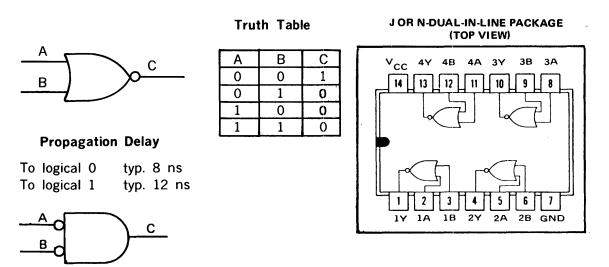

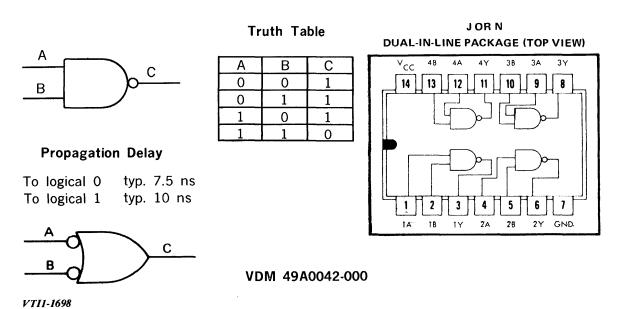

|              | 7402PC)                                                                      | V-2                |

| V-3          | Quadruple 2-Input Positive NAND Gate (Open Collector)                        |                    |

|              | (SN7403N)                                                                    | V-3                |

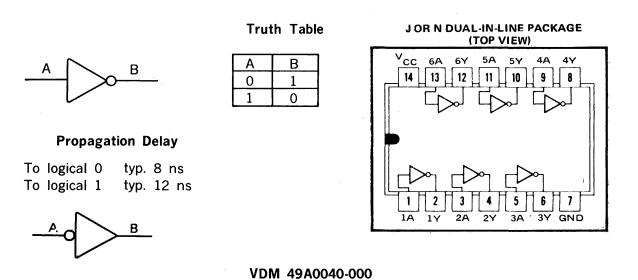

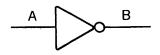

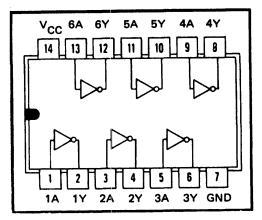

| V-4          | Hex Inverters (SN7404N, MC7404P, N7404A, 7404PC)                             | V-3                |

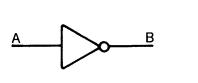

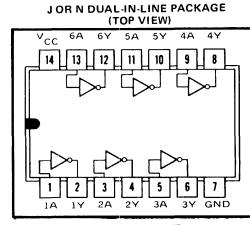

| V-5          | Hex Inverter with Open-Collector Circuit (SN7405J, MC7405L)                  | V-4                |

| V-6          | Triple 3-Input Positive NAND Gate (SN7410N, 7410PC, N7410A)                  | V-4                |

| V-7          | Dual 4-Input Positive NAND Gate (SN7420N, MC7420, 7420PC)                    | V-5                |

| V·8          | Dual 4-Input Positive NAND Buffer (SN7440N, MC7440L, 7440DC).                | V-6                |

| V-9          | Quadruple 2-Input Positive NAND Gate (SN74H00N, MC3000P)                     | V-7                |

| V-10         | Quadruple 2-Input Positive NAND Gate with Open Collector (SN74H01N, MC3004P) | V.7                |

| V-11         | Hex Inverter (SN74H04N, MC30018)                                             |                    |

| V-11<br>V-12 | Hex Inverter with Open-Collector Output (SN74H05N)                           |                    |

| V-12<br>V-13 | Triple 3-Input Positive NAND Gate (SN74H10N)                                 |                    |

| V-13<br>V-14 | Triple 3-Input Positive AND Gate (SN74H11N)                                  |                    |

| V-14<br>V-15 | Dual 4-Input Positive NAND Gate (SN74H11N)                                   |                    |

| • 10         | Dua, I mput i contro in the dute (orth-frizon, modern)                       | <del>4</del> - 1 0 |

| V-16 | Dual 4-Input Positive AND Gate (SN74H21N, MC3011)             | V-11 |

|------|---------------------------------------------------------------|------|

| V-17 | Dual 4-Input Positive NAND Gate (SN74H22N)                    | V-12 |

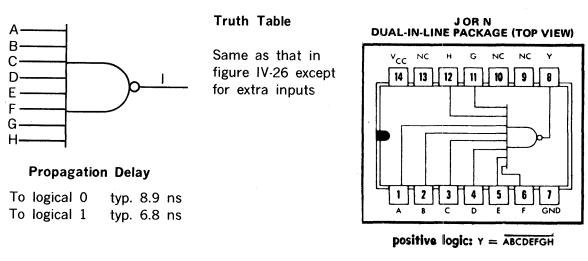

| V-18 | 8-Input Positive NAND Gate (SN74H30N)                         |      |

| V-19 | Dual 4-Input Positive NAND Buffer (SN74H40N, MC3024P)         |      |

| V-20 | Dual 2-Wide 2-Input AND-OR-Invert Gates (SN74H50 and 51N,     |      |

|      | MC3020 and 3023)                                              | V-14 |

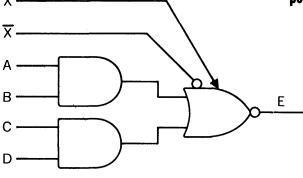

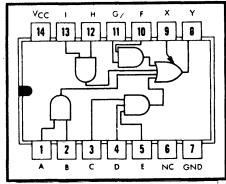

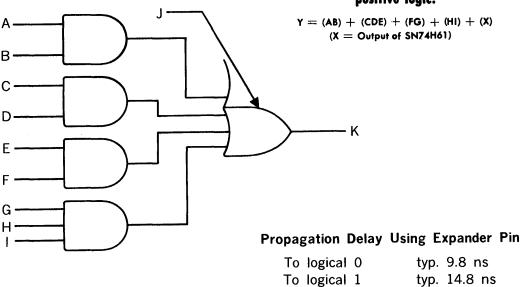

| V-21 | Expandable 2-2-2-3-Input AND-OR Gate (SN74H52N, MC3031P)      |      |

| V-22 | Expandable 2-2-2-3-Input AND-OR Invert Gate (SN74H53N,        |      |

|      | MC3032)                                                       | V-16 |

| V-23 | 3-2-2-3-Input AND-OR Expander (SN74H62N, MC3018P)             | V-17 |

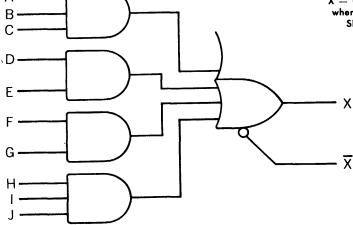

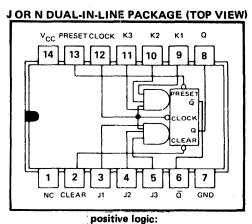

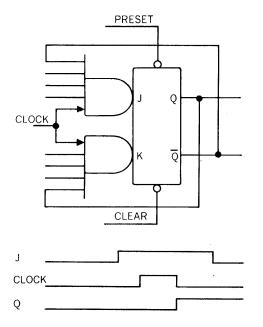

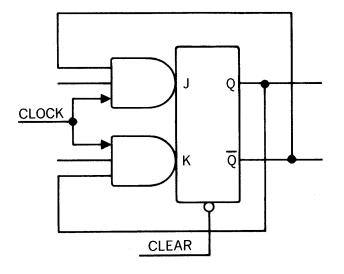

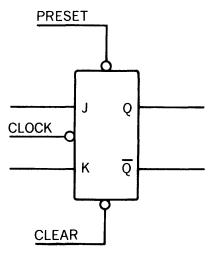

| V-24 | J-K Master-Slave Flip-Flop (SN7472N)                          |      |

| V-25 | J-K Master-Slave Flip-Flop (SN74H72N)                         |      |

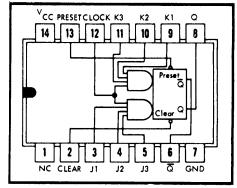

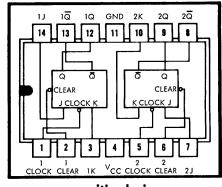

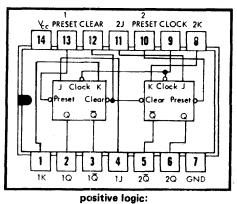

| V-26 | Dual J-K Master-Slave Flip-Flops (SN7473 and 74107N)          |      |

| V-27 | Dual J-K Master-Slave Flip-Flops (SN74H73N)                   |      |

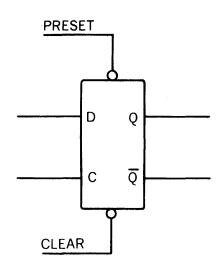

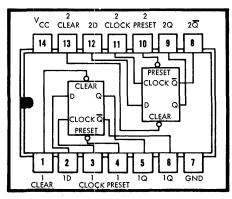

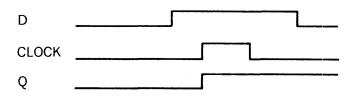

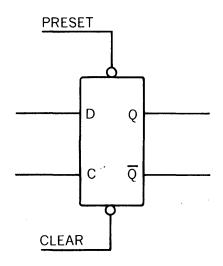

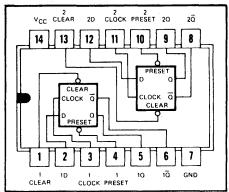

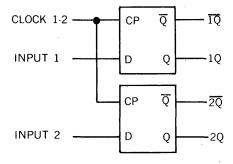

| V-28 | Dual D-Type Edge-Triggered Flip-Flop (SN7474N)                |      |

| V-29 | Dual D-Type Edge-Triggered Flip-Flop (SN74H74N)               |      |

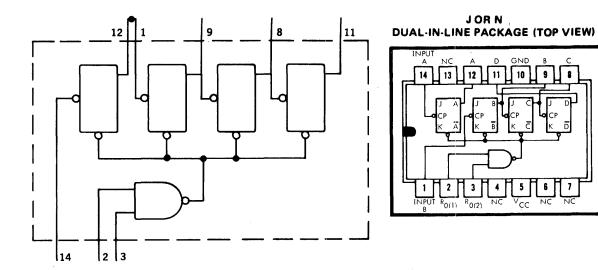

| V-30 | 4-Bit Binary Counter (SN7493N)                                |      |

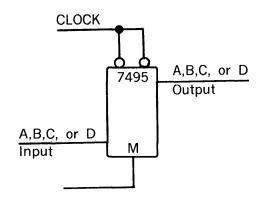

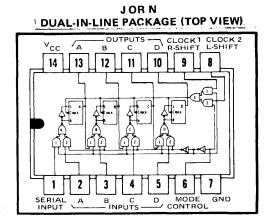

| V-31 | 4-Bit Right-Shift Left-Shift Register (SN7495N)               |      |

| V-32 | Dual J-K Edge-Triggered Flip-Flop (SN74H108N)                 |      |

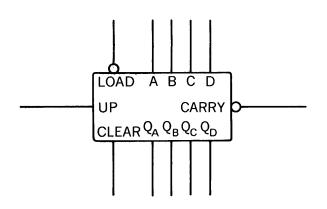

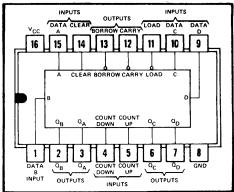

| V-33 | Synchronous 4-Bit Up/Down Counter (SN74193J)                  |      |

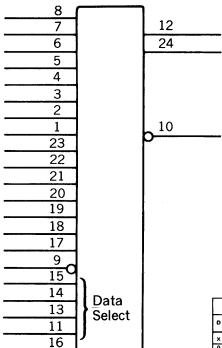

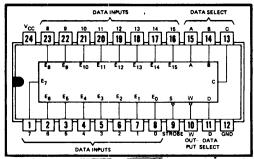

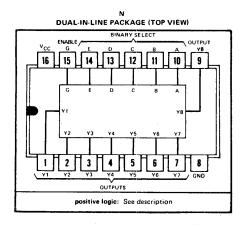

| V-34 | Data Selector/Multiplexor (SN74150N)                          | V-28 |

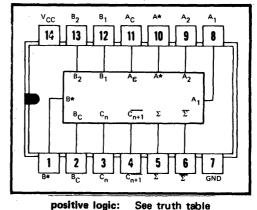

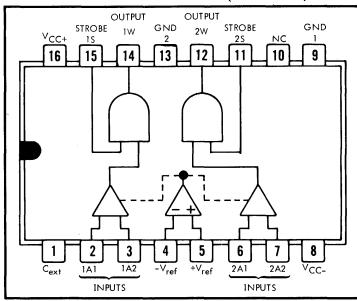

| V-35 | Arithmetic Logic Unit/Function Generator (SN74181N)           | V-29 |

| V-36 | Look-Ahead Carry Generator (SN74182N)                         | V-30 |

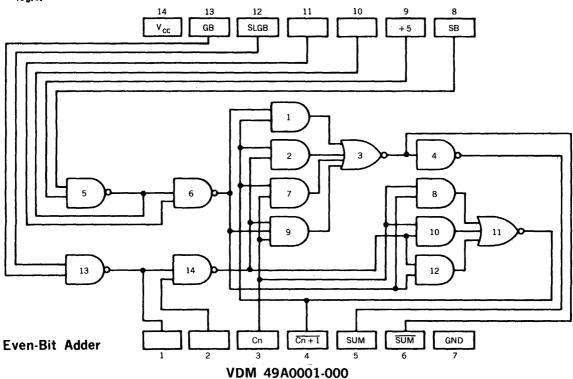

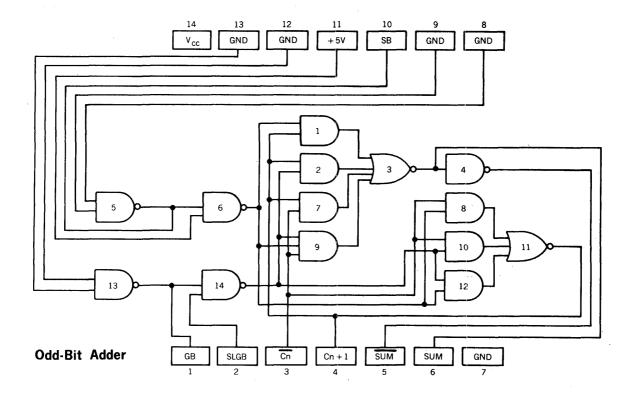

| V-37 | Gated Full Adder (SN7480N)                                    | V-31 |

| V-38 | 256-Bit Read-Only Memory (SN7488N)                            |      |

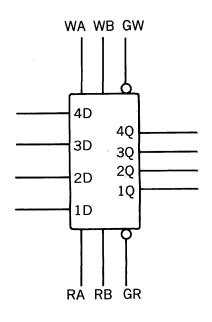

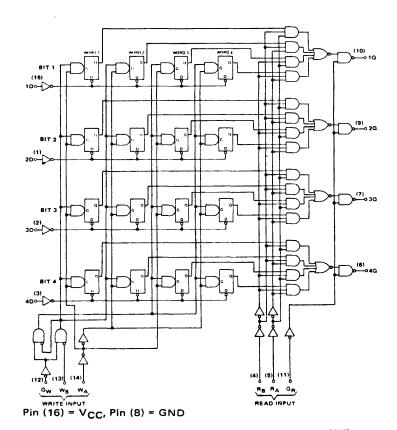

| V-39 | High-Speed Buffer Memory/Register File (SN74170N)             | V-35 |

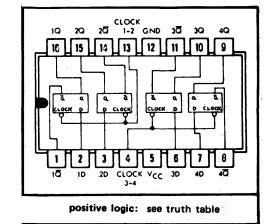

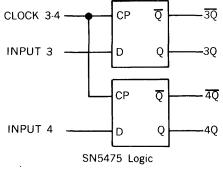

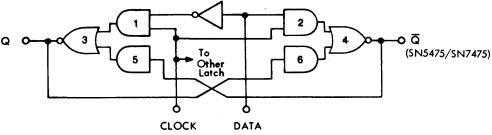

| V-40 | Quadruple Bistable Latch (SN7475N)                            | V-37 |

| V-41 | Quadruple 2-Input NAND Gate (SN15846N)                        | V-38 |

| V-42 | Triple 3-Input NAND Gate (SN15862N)                           | V-38 |

| V-43 | Dual 4-Input NAND Power Gate (SN6006N)                        | V-39 |

| V-44 | Pulse-Triggered Binary (SN15850N)                             | V-40 |

| V-45 | Monostable Multivibrator (SN15851N)                           |      |

| V-46 | Retriggerable Monostable Multivibrator (Fairchild U6A960159X) | V-42 |

| V-47 | Quadruple 2-Input AND Gate (MC3001P)                          | V-42 |

| V-48 | Quadruple 2-Input NOR Gate (MC3002P)                          |      |

| V-49 | Dual Sense Amps                                               | V-43 |

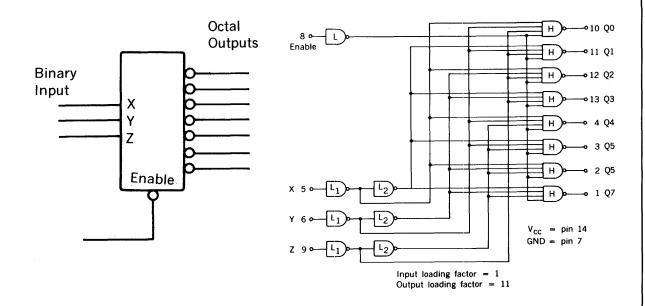

| V-50 | Binary to Octal Converter (MC4006P)                           | V-44 |

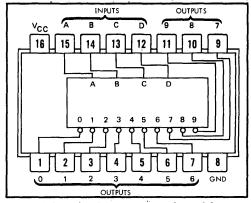

| V-51 | 3-Line to 8-Line Decoders                                     |      |

## LIST OF TABLES

| IV-1  | 620/i and 620/L Specifications    | IV-2  |

|-------|-----------------------------------|-------|

| IV-2  | Controls and Indicators           | IV-8  |

| IV-3  | Basic Timing Clock                | IV-18 |

| IV-4  | Instruction Storage in U Register | IV-26 |

| IV·5  | Operation Code Classes            |       |

| IV-6  | Operation Code Sets               | IV-27 |

| IV-7  | Operation Code Groups             | IV-28 |

| IV-8  | M Field Decoding                  | IV-28 |

| IV-9  | 620/f Specifications              | IV-31 |

| IV-10 | Basic Timing Clocks               | IV-51 |

| IV-11 | 620/L-100 Specifications          | 1V-58 |

| IV 12 | Bootstrap Loader Routines         | IV-67 |

| IV-13 | Varian 620/L-100 System Clocks    | IV-78 |

|       |                                   |       |

| CHAPTER I COMPUTER FUNDAMENTALS |                 | varian data machines | ( <del>M)</del> — |

|---------------------------------|-----------------|----------------------|-------------------|

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 | •                    |                   |

| CHAPTER I COMPUTER FUNDAMENTALS |                 |                      |                   |

| COMPUTER FUNDAMENTALS           | CHAPTED I       |                      |                   |

|                                 |                 | AFRITAL C            |                   |

|                                 | COMPUTER FUNDAM | IEN IALS             |                   |

|                                 |                 |                      |                   |

|                                 |                 |                      |                   |

|                                 |                 |                      |                   |

|                                 |                 |                      |                   |

|                                 |                 |                      |                   |

|                                 |                 |                      |                   |

|                                 |                 |                      |                   |

|                                 |                 |                      |                   |

|                                 |                 | •                    |                   |

|                                 |                 |                      |                   |

|                                 |                 |                      |                   |

|                                 |                 |                      |                   |

|                                 |                 |                      |                   |

## CHAPTER I COMPUTER FUNDAMENTALS

# SECTION I INTRODUCTION

### 1.1 GENERAL DESCRIPTION

Digital computing devices are not new. The first machine to employ some of the principles of modern computers was invented by Charles Babbage of England in 1822. His device, which he called the analytical engine, was a steam-driven assembly of gears that automatically computed and printed tables. The analytical engine incorporated three elements used in computers today:

- a. Storage (memory for holding information)

- b. A mill (arithmetic unit), including the machinery for making decisions, to work on the information

- c. A control to govern the mill automatically and call for the next piece of information in sequence when required

About the same time, George Boole, an English mathematician, was laying the foundations of logical algebra. Boolean algebra is the cornerstone of computer logic circuit design.

The era of the modern computer began in 1937 with the Mark 1, an automatic sequence-controlled calculator. Present electronic computers retain the same operational principles as earlier machines. The great advances in computer technology have been in the fields of circuit design and new components.

The digital computer is not a brain, but merely a machine that must be given precise instructions on what and how to perform. What the human lacks in lightning speed and unerring memory, the computer has in abundance. What the computer lacks in the ability to reason, analyze, deduce, organize, and plan, man can supply. The computer is insensitive to human emotion. When the button is pressed, the computer goes all the way, given correct instructions, power, and data input. But, for all its merits, the computer is useless if humans have not analyzed and prepared the problem for the machine and told the computer exactly what it must do and when, in a language understandable to the computer. The computer does not need human inspiration, but it must have the explicit direction and control that can come only from the human brain. Man's role in solving this problem is to program the computer.

CHAPTER I

COMPUTER FUNDAMENTALS

### 1.2 COMPUTER CONCEPTS

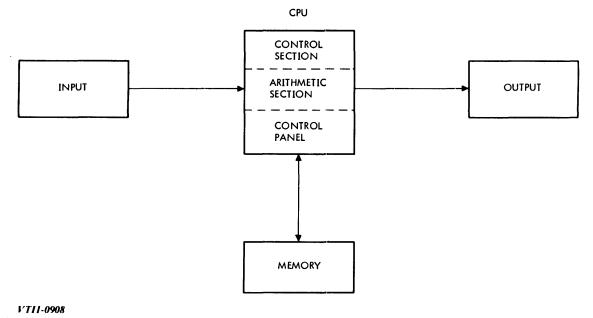

A digital computer system can be divided into four basic sections as shown in the figure below. The computer proper, called the central processing unit (CPU), has three subsections: the control section, the arithmetic section, and the control panel. The primary unit for the storage of information is called the memory. The input unit provides information and instructions to the computer. The output unit gives the user the processed data or information (answer).

### 1.2.1 Central Processing Unit (CPU)

The control section coordinates computer operations. It directs data transfers and controls the manipulation of the data. The control section also interprets and executes the instructions and information read from memory or received from the input unit.

The arithmetic section performs calculations using basic arithmetic operations. It also manipulates data under the supervision of the control section. The arithmetic section usually contains registers (accumulators) that hold the data and the results of the calculations and manipulations and logic circuitry that enables the data in the registers to be combined with information transferred from memory or input devices.

Figure I-1. Typical Computer System

# CHAPTER I COMPUTER FUNDAMENTALS

The control panel gives the user direct access to and control over CPU operations and memory. Switches and indicators on the CPU permit examination or alteration of the contents of memory or determination of the current status of the CPU and the program operating in it. The control panel and a keyboard input device (teletypewriter) are often grouped together under the term console.

### 1.2.2 Memory

The memory is a storage device for instructions and data. It is termed permanent storage because its contents remain unchanged unless alterations are specifically requested by the program or user. Since all information processed by the computer system passes through memory, memory is considered the heart of any data-processing system.

### 1.2.3 Input Unit

The input unit receives instructions and data from input devices, e.g., punched card readers, teletypewriter keyboards, magnetic tape or disc devices, etc. The input unit translates the information received from these devices into a form that memory can accept and store.

### 1.2.4 Output Unit

The ouput unit translates finished, processed data (answers) from the CPU into a form that can be accepted by output devices, e.g., card punches, line printers, magnetic tape or disc devices, etc., and transmits the translated data to these devices.

Note that some peripheral devices, e.g., magnetic tape or disc devices, can function both as input and output devices.

CHAPTER I

COMPUTER FUNDAMENTALS

## SECTION 2 NUMERICAL ANALYSIS

#### 2.1 INTRODUCTION

The numerical analysis of a problem demands mathematical skill and ingenuity from the digital computer user. Scientific and engineering problems are not expressed in terms that can be directly handled by the computer. Roots, vectors, trigonometric functions, differential equations, and similar mathematical expressions and operations must be reduced to (or expressed as) a series of arithmetical operations if the computer is to solve the problem.

Specialists in the field of numerical analysis seldom actually use a digital computer; their major concern is to provide the computer user with techniques, algorithms, routines, and other mathematical assistance to permit computer applications. Computer users, however, must have an elementary knowledge of numerical analysis.

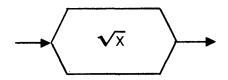

## 2.2 SQUARE ROOT EXTRACTION

Extracting the square root of a quantity is a basic mathematical operation that is often useful. The way in which this operation is executed by a digital computer is presented as an example of an algorithm provided by the science of numerical analysis. The operation is known as Newton's algorithm for square roots or the square root algorithm.

To begin, let X represent any number and let Y = X; i.e., Y is approximately equal to  $\sqrt{X}$  or an approximation of  $\sqrt{X}$ . Y can represent  $\sqrt{X}$  with sufficient precision for the required purpose. Y will be equal to 0 only if X is equal to 0. For any other value of X, Y is equal to or less than X (Y  $\leq$  X). For example, if X = 25, then Y can initially have any value between 0 and 25.

The formula for the square root algorithm is

$$Y_{i+1} = \frac{1/2 (Y_i + \frac{X}{Y_i})}{1/2}$$

where i = the order of the approximation; i.e., the number of times the equation has been solved for Y. The following example shows how the square root of 25 is obtained when 24 is selected as the first approximation.

# CHAPTER I COMPUTER FUNDAMENTALS

$$Y_1 = \frac{1}{2}(24 + \frac{25}{24})$$

$Y_3 = \frac{1}{2}(7.26 + \frac{25}{7.26})$

$= \frac{1}{2}(24 + 1.0417)$   $= \frac{1}{2}(7.26 + 3.4435)$

$Y_1 = \frac{12.5208}{12.52}$   $Y_3 = \frac{5.3517}{5.35}$

$= \frac{1}{2}(12.52 + \frac{25}{12.52})$   $Y_4 = \frac{1}{2}(5.35 + \frac{25}{5.35})$

$= \frac{1}{2}(12.52 + 1.9968)$   $Y_4 = \frac{1}{2}(5.35 + 4.6729)$

$Y_2 = \frac{7.2584}{5.01}$   $Y_4 = \frac{5.0114}{5.01}$

$= \frac{1}{2}(5.01 + \frac{25}{5.01})$

$= \frac{1}{2}(5.01 + 4.99)$

$Y_5 = 5$

The fifth approximation in this example gave the exact value of Y, but it is possible that an additional step (or one less) would be required if no roundoffs were made during computation. Frequently, an exact root cannot be found as square roots are often irrational numbers.

The value first assinged to Y does not affect the precision with which  $\sqrt{X}$  can be found. Y represents only the number of approximations to be performed.

The theory of square root extraction by this method states that:

- a. When any number is divided by its square root, the quotient is the square root. 25/5 = 5

- b. When a square root is added to a square root and the sum divided by 2, the quotient is the square root.

$$1/2(5 + 5) = 5$$

# CHAPTER I COMPUTER FUNDAMENTALS

c. Therefore

$$Y = \frac{1}{2}(5 + \frac{25}{5})$$

$$= \frac{1}{2}(10)$$

$$Y = 5$$

An equivalent and alternate form of the square root algorithm formula is

$$Y_{i+1} = Y_i + \frac{1}{2}(X \cdot Y_i)$$

The following is an example of this formula using the same values as the first example. The results of the first three approximations show the equivalency of the two formulas; the fourth and fifth approximations are omitted.

$$Y_1 = 24 + 1/2(25 - 24)$$

$Y_2 = 12.51 + 1/2(25 - 12.52)$

$= 1/2(1.0417 \cdot 24)$   $= 12.52 + 1/2(1.9968 \cdot 12.52)$

$= 24 \cdot 11.4791$   $= 12.52 \cdot 5.2616$

$Y_1 = 12.5209$   $Y_2 = 7.2584$

$Y_3 = 7.26 + 1/2(25 - 7.26)$

$= 7.26 + 1/2(3.4435 \cdot 7.26)$

$Y_3 = 5.3517$

In conventional usage of the subscript, i = 0 is the first approximate root as illustrated below. A formula for successive approximations (iterations) is also shown.

# CHAPTER I COMPUTER FUNDAMENTALS

# First Approximation Second Approximation $Y_{i+1} = \frac{1}{2}(Y_i + \frac{X}{Y_i}) \qquad Y_{i+2} = \frac{1}{2}(Y_i + \frac{X}{Y_i})$ $Y_1 = \frac{1}{2}(Y_0 + \frac{X}{Y_0}) \qquad Y_2 = \frac{1}{2}(Y_1 + \frac{X}{Y_1})$ $Y_{i+1} = \frac{Y_i + \frac{1}{2}(\frac{X}{Y_i} + \frac{Y_i}{Y_i})}{Y_i} \qquad Y_{i+2} = \frac{Y_{i+1} + \frac{1}{2}(\frac{X}{Y_i} + \frac{Y_{i+1}}{Y_i})}{Y_{i+1}}$ $Y_2 = \frac{Y_1 + \frac{1}{2}(\frac{X}{Y_i} + \frac{Y_1}{Y_i})}{Y_i}$

The square root algorithm is particularly applicable for use with digital computers due to the following advantages:

- a. The computer is required to execute only the arithmetic operations of addition, subtraction, and multiplication or division on the data supplied.

- b. The programmer need only approximate the square root, and the closeness of this first approximation will not affect the precision of the final result.

The precision of the final result is dependent upon the number of iterations performed. The first approximation determines the number of iterations required to accomplish this final precision. As illustrated below, it does not matter whether this first approximation is larger or smaller than the correct root.

Let

$$X = 36$$

, and  $Y_0 = 4$

$$Y_1 = Y_0 + \frac{1}{2}(X - Y_0) \qquad Y_2 = 6.5 + \frac{1}{2}(36 - 6.5)$$

$$= 4 + \frac{1}{2}(36 - 4) \qquad = 6.5 + \frac{1}{2}(5.5385 - 6.5)$$

$$= 4 - \frac{1}{2}(9 - 4) \qquad = 6.5 + \frac{1}{2}(-0.9615)$$

$$= 4 + 2.5 \qquad = 6.5 - 0.48$$

$$Y_1 = 6.5 \qquad Y_2 = 6.02$$

The square root algorithm is an example of many such algorithms and similar techniques developed by the science of numerical analysis for use in digital computer problem solving.

|       | ———— varian data machines | (AA) |

|-------|---------------------------|------|

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

| OUAT  | TED II                    |      |

| CHAP  | PTER II                   |      |

| PROGR | AMMING                    |      |

|       |                           |      |

|       |                           |      |

| ·     |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

|       |                           |      |

# SECTION 1 INTRODUCTION

### 1.1 COMMUNICATION WITH A COMPUTER

Any computer accepts and executes a certain number of instructions (commands). Such expressions can be plain English words or phrases, e.g., CLEAR AND ADD, MULTIPLY, STORE WORD, etc. However, because of the length of such expressions and the frequency of their use in computer programs, abbreviated mnemonic forms are often substituted.

### 1.2 MNEMONICS

A mnemonic code is usually composed of a two- or three-letter group representing a specific computer instruction. Each of the letters in the group corresponds to the first (or key) letter in the complete word or phrase. For example, the instruction CLEAR AND ADD can have the mnemonic CAD.

Mnemonics simplify the writing of computer programs. However, because the computer responds only to numerical input, neither the mnemonic nor the full written instruction is readily understandable to the computer. Each instruction, therefore, has a corresponding numerical equivalent or numerical code.

### 1.3 NUMERICAL CODES

The numerical code exists in the computer as a combination of the binary digits 0 and 1. For simple machines, such codes can be expressed in full binary form. However, for most computers the codes will be condensed to octal (base 8) or hexadecimal (base 16) numbers. The use of octal or hexadecimal numbers allows the code groups to be expressed in fewer digits than required by binary notation.

Octal notation is widely used because of the ease with which octal to binary conversions can be performed. Thus, data fed into the computer in octal form can be readily converted by the computer to binary for storage in memory. If the computer is not equipped to perform this conversion, it can be done mentally by the programmer as he loads the data.

### 1.4 INSTRUCTION SET

The list of instructions or codes that a computer accepts and executes is called the instruction set (repertoire) for that computer. The binary codes for these instructions comprise the machine language for that computer, the only language the computer understands.

### 1.5 PREPARING THE PROBLEM

The writing of a routine for the solution of a particular problem by a specific computer requires the formulation of a computer message in its machine language. The message writing procedure begins with the numerical analysis of the problem and ends with the writing of the routine in machine language. One or more people may be involved, each utilizing his individual area of interest to accomplish a specific part of the total task.

- a. The numerical analyst analyzes the problem and finds the best mathematical approach for the particular application.

- b. The programmer decides:

- (1) Operations to be performed and order of performance.

- (2) Addresses for the required number of instructions, and any address modifications necessary.

- (3) Addresses for the required number of data words.

The programmer can use mnemonics for the written routine rather than specify the actual addresses to be used.

c. The coder prepares the final routine in numerical code with all addresses designated.

When the entire program is coded in machine language, it is ready to be loaded into the machine.

## SECTION 2 FLOW-CHARTING

### 2.1 INTRODUCTION

In preparing a problem for the computer, the user must first clearly define the problem and a method of solving it. The computer can only follow instructions and cannot devise its own methods of problem-solving. The definition of a simple problem and the method of solving it may be obvious enough that the program can be coded directly as a list of instructions in mnemonic form. However, if a problem is this simple, use of a computer is probably unnecessary.

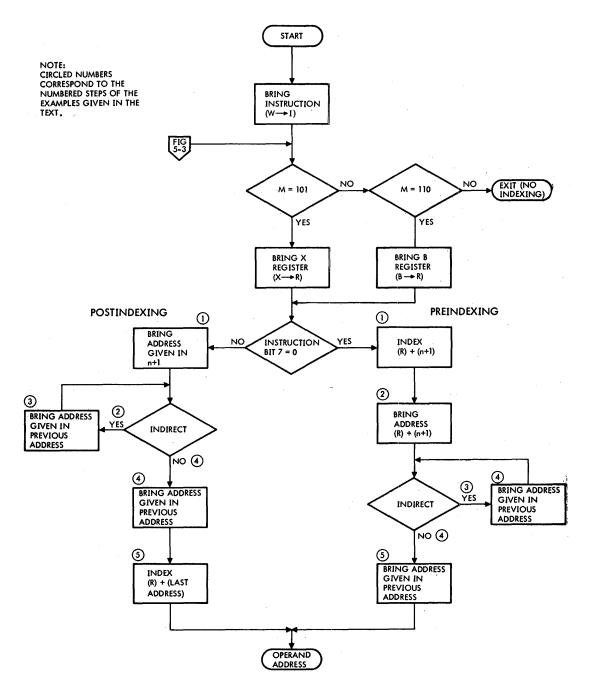

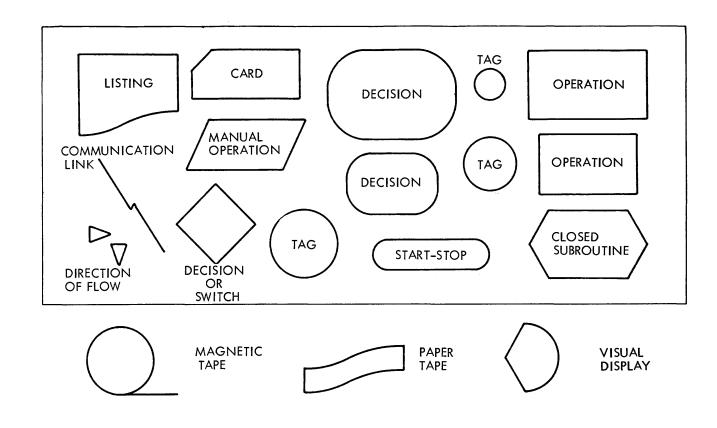

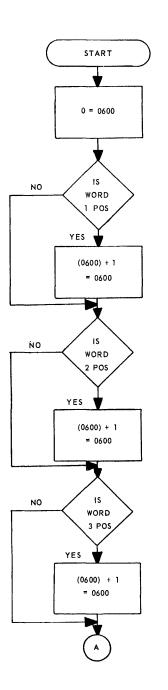

In typical computer problems from the business and scientific worlds, solutions require many steps and decisions. As an aid to programming the solutions to such problems, the flow chart is invaluable. The flow chart illustrated in figure II-1 is a schematic diagram of the logical steps required to solve the problem. The chart consists of a series of connected geometric figures, each denoting a step in the solving of the problem. Each geometric shape has a particular logical significance, e.g., rectangles indicate computer processing steps, diamonds indicate decisions (refer to figure II-2). The geometric forms are annotated with explanations and connected with lines and arrows showing the sequence and direction of process flow.

Since the flow chart is a tool for analysis and clarification, it generally shows only enough information to ensure:

- a. Correct compilation of the instructions in the program

- b. Proper planning for and allocation of memory space

Flow-charting is sometimes considered an art rather than a science because it is unlikely that two programmers will produce identical flow charts for the solution of the same problem. Given the various ways of approaching any problem, it is not necessary that such charts be identical. Even the number of functions considered to be a single step for inclusion in one geometric figure in the chart will vary. Since flow charts are tools, the way in which this tool is used depends on the programmer's training, experience, ability, preferences, and even personality. These differences do not reduce the importance of the flow chart or the necessity of mastering flow-charting techniques. A good flow chart gives maximum assistance in compiling a program and allocating memory space. Flow-charting is thus an art with a sound basis in scientific methods.

VT13-0243

Figure II-1. Typical Flow Chart

VTI1-0240

Figure II-2. Flow Chart Symbols

The completed flow chart should be examined to see that a program based on it will actually allow the computer to solve the problem. Alternate methods that might require less computer running time and/or memory space should be considered. When these considerations have been taken into account and the final flow chart approved, the programmer is ready to start writing the program based on the chart.

### 2.2 NOTATION

The following is a list of common notations used to signify the writing of computer programs.

| Notation | Meaning                                                                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| ( )      | The content of; (A) indicates the contents of the A register.                                                                                 |

| A1       | A register bit 1                                                                                                                              |

| A1-5     | A register bits 1 through 5                                                                                                                   |

| Asn      | A register sign bit                                                                                                                           |

| <b>→</b> | Indicates the transfer of data; (A) $\rightarrow$ (B) means the contents of the A register are transferred to the contents of the B register. |

| 1 1      | The magnitude of; $\mid X \mid$ indicates the magnitude of X                                                                                  |

| <        | Smaller than; (A) $<$ (B) indicates that the contents of the A register are smaller than the contents of the B register.                      |

| >        | Greater than; $(A) > (B)$ indicates that the contents of the A register are greater than the contents of the B register                       |

### 2.3 SYMBOLS

### 2.3.1 Functions

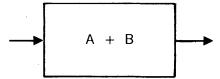

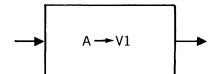

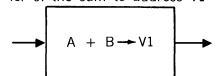

The solution of a problem requires the execution of several functional steps. In the context of flow-charting, a functional step is one that requires the exectuion of an arithmetical or logical operation on the data being processed or the transfer of data within the computer. A function box in the flow chart indicates a functional step or operation as illustrated below.

The number of functions in any function box is at the discretion of the programmer. In the preliminary part of the analysis, two or more functional operations may appear in a single box if the operations are related or sequential, such as those shown in figure II-3. As the analysis progresses and the flow chart becomes more complete and detailed, complexity permits only one functional operation per box.

Not annotated

Annotated to show the addition of word A to word B

Annotated to show the transfer of word A to address V1

Annotated to show the addition of words A and B and the transfer of the sum to address V1

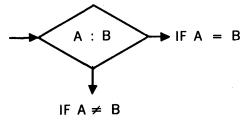

### 2.3.2 Decisions

A decision box is used to show a step which requires the computer to make a decision. Computer decisions are two-valued (yes or no or true or false); therefore, the decision box has one input path and two output paths (see below). For a particular operation, only one of the output paths is taken dependent upon the decision.

Annotated to show a decision based on an equality comparison of values of words A and B

Annotated to show a decision based on the comparative values of words A and B

## 2.3.3 Input/Output

Whenever problem solution requires that information be received via the input equipment, or transmitted via the output equipment, an input/output box is used in the flow chart as illustrated.

The input/output box is annotated to indicate:

- a. The operation to be performed by the use of words such as LOAD, STORE, PRINT, DISPLAY, etc.

- b. Data involved as stated in the literal term appearing in the equation  $(a, x, b^2)$ , a memory address, or an auxiliary store address.

- c. The input/output equipment involved. The equipment may be implied by the operation (PRINT implies a teletypewriter), or explicitly stated.

Annotated for the loading of word A into memory via the card reader

LOAD A FROM CARD READER

Annotated for the printing of the word at address V2

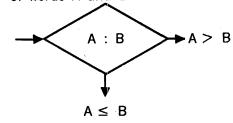

### 2.3.4 Start and Stop

Start and stop boxes designate the beginning and the end of a flow chart as illustrated below.

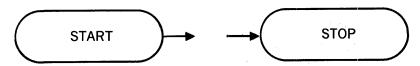

### 2.3.5 Fixed Connectors

A flow chart appears as a sequence of interconnected boxes arranged in either columns or rows. It is normally not possible to present an entire flow chart on one page. Therefore, a system of fixed connector circles is used to relate the separate sheets of the flow chart. These circles are numbered; all fixed connectors with the same number refer to the same location on the chart. A fixed connector may have one or more input/output paths as illustrated.

### 2.4 A SIMPLE FLOW CHART

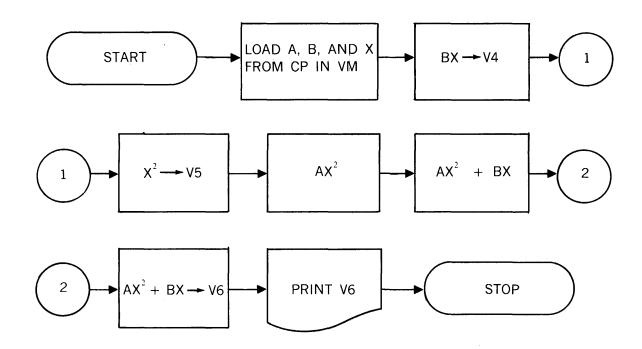

Using only the symbols presented so far, it is possible to formulate a simple flow chart to solve the equation:

$$T = AX^2 + BX$$

In the preceding flow chart:

- a. FROM CP IN VM indicates that data is input from the control panel and stored in variable memory. Variable memory is the area of memory reserved for the storage of data with variable values, as opposed to data representing mathematical constants with fixed values.

This flow chart is only one of many that could be constructed for this particular problem. The number of boxes used and the amount of information given in each box is at the discretion of the programmer. For instance, the loading of each of the three terms (A, B, and X) could be shown by a separate input box, and each of these boxes could be annotated to show the storage address in variable memory.

The general rule is to show only the information necessary to compile the list of instructions and to ensure proper allocation of memory addresses.

### 2.4.1 Substitution

The preceding flow chart does not explicitly show when the value of T is computed but implicates it in the function box  $AX^2 + BX$  before fixed connector box 2. At this point, a substitution box can be used to indicate that a computation has been performed and the result can be substituted to simplify the notations that follow.

Annotated for point of computation and substitution

$$AX^2 + BX \longrightarrow T$$

Annotated to change the value of a subscript

The substitution box can also be used to:

- a. Advance or change the value of a subscript (see above).

- b. Provide a term or quantity that is equivalent to one that is not available (i.e., the cosine of 60° that is available in memory for the sine 60° that is not).

- c. Modify an address to effectively substitute one address for another.

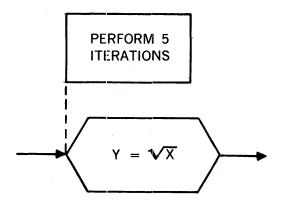

### 2.4.2 Subroutines

Often the solution of a problem requires the solution of one or more subordinate or auxiliary problems. If these secondary problems appear repeatedly, either within the same problem or in different problems, a separate routine is written for each problem and used whenever that problem appears. These previously prepared routines for secondary problems are called subroutines.

A flow chart is prepared for a subroutine in the same manner as larger routines except that the START and STOP boxes are annotated identically to identify the subroutine. A subroutine computation box is used to indicate where the subroutine is to appear on the larger flow chart; the subroutine flow chart itself does not appear.

#### 2.4.3 Assertions

An assertion box is used to present additional information or explanatory notes. It is appended outside the path of the flow chart to indicate where the information is applicable.

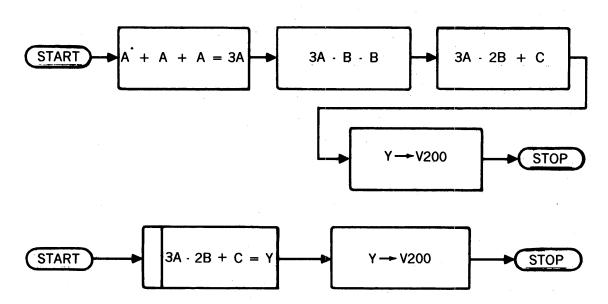

### 2.5 A MORE COMPLICATED FLOW CHART

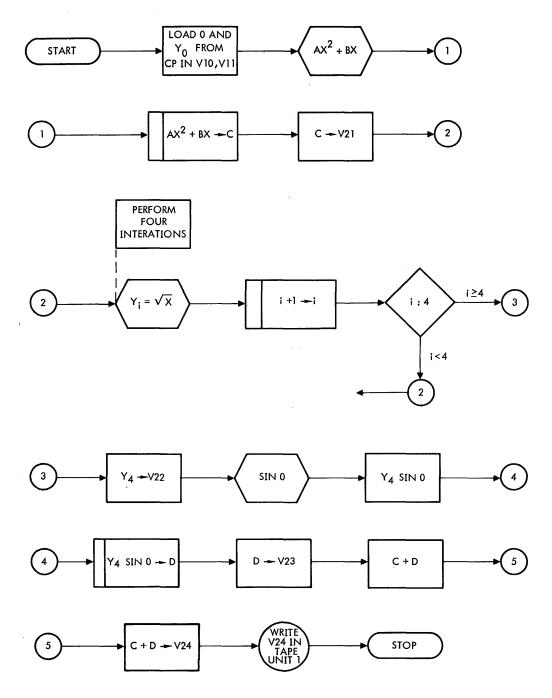

Figure II-3 is a flow chart to solve the problem:

$$T = AX^2 + BX + \sqrt{X} + \sin \theta$$

Subroutines are available for  $AX^2 + BX$ ,  $\sqrt{X}$ , and sin 0. It is assumed that the correct values of all terms are stored at a known memory address (any address except 0). A value for Y in the square root algorithm must be assigned and stored in memory.

Between fixed connectors 2 and 3, the value of 1 is added to the subscript value of Y each time a square root iteration is performed. This value is then compared with a value in the decision box to determine when the required number of iterations (in this case, four) have been performed so that the computation can proceed to the next step. During the square root computations a closed loop exists in the flow chart between the bottom of the decision box and the left end of the square root subroutine computation box (fixed connector 2). Such a loop is known as a program loop.

Since a decision box always has two output paths, the appearance of a decision box in a flow chart will always produce a program loop or a program branch; i.e., if one of the

VT11-1163

Figure II-3. Flow Chart for  $T = AX^2 + BX \sqrt{X} \sin \theta$

output paths does not loop back to a previous point in the flow chart, then the decision must be to branch out on one or the other of the two possible output paths. Thus, a branch determines which of two possible methods (or program paths), are to be used for the remainder of the problem solution.

# SECTION 3 MACHINE LANGUAGE PREPARATION

#### 3.1 INTRODUCTION

After a problem has been analyzed and a method of solution determined by the construction of a flow chart, the routine (or program) is prepared. The programmer first verifies that:

- a. The flow chart utilizes a method that will actually solve the problem.

- b. This method is presented in its simplest form.

- c. There is not a more efficient method.

### 3.2 INSTRUCTION REPERTOIRE

A program is written for a specific computer in response to the language used and the repertoire provided. The number of instructions in a repertorie varies. A large repertoire does not necessarily mean that the program will be more complex, only that more instructions are available for the programmer's use. A thorough knowledge of the specific computer's repertoire is necessary to fully utilize the instructions provided.

To write a program, the programmer must know:

- a. The name and mnemonic of each instruction in the repertoire.

- b. The result obtained through the use of each instruction.

- c. The conditions governing the use of a particular instruction.

- d. The type and format of the computer's instruction and data words.

- e. The types of addressing available, and the use of addresses with the various instructions.

### 3.2.1 Instruction Types

All computer instructions are classified as arithmetic or processing instructions, transfer of information instructions, or transfer of control instructions.

Certain instructions are included in two classifications; i.e., instructions that transfer data to the arithmetic unit and perform an operation there. Examples are the ADD, SUBTRACT, MULTIPLY, and DIVIDE instructions. This type of instruction always requires the use of an address in the address part of the instruction word to specify the location of the data word.

SHIFT LEFT and SHIFT RIGHT are examples of instructions that are only arithmetic or processing instructions. This type of instruction does not require an address as no data are transferred.

Transfer of information instructions such as LOAD and STORE generally require the use of an address in the instruction word to indicate the point of origin or destination of the word being transferred. An exception is an instruction such as TRANSFER where the origin and destination are given.

There are many transfer of control instructions, including all the JUMP instructions. These instructions contain an address in the address part of the instruction word to indicate the location of the instruction to which the program jumps. This is the address of another instruction not a data word.

### 3.2.2 Addresses

A program can use either the actual address or a relative address. If the problem is fairly simple, the actual address is used throughout. In more complex problems, relative addresses are used until memory requirements are established and actual addresses can replace the relative addresses. Actual addresses are expressed in octal or hexadecimal notation; relative addresses can use any convenient format.

#### 3.2.3 Codes

In the program, instructions are written as mnemonic code references. Each mnemonic in turn references a numeric code which is the final input to the computer and constitutes the machine language. Mnemonic codes and the associated numeric codes for each instruction are provided by the manufacturer of the specific computer. After the program is completed, the mnemonics are coded into the numeric equivalents.

### 3.3 SAMPLE PROGRAMS

The following programs are presented to illustrate a computer repertoire. A specific computer repertoire can comprise more or fewer instructions than used in these programs.

A digital computer is normally used only for complex or lengthy problems as operating expense does not make it practical for use in simple problems. The examples that follow are presented as illustrations of flow charts and repertoires; they are too simple to be typical computer problems. For additional information about these problems, refer to the applicable system reference manual and to the instruction repertoire (figure III-7).

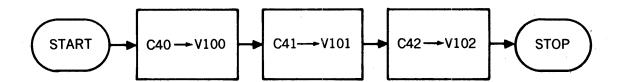

#### PROBLEM 1

Given:

Three constants stored in constant memory locations:

C40, C41, and C42.

Problem:

To store these constants in variable memory locations:

V100, V101, and V102, respectively.

### Flow chart

|          |           | Repertoire |                                                                                                  |

|----------|-----------|------------|--------------------------------------------------------------------------------------------------|

| Step No. | Operation | Address    | Remarks                                                                                          |

| 000      | LDA       | C40        | This instruction clears the accumulator to 0 and loads the contents of C40 into the accumulator. |

| 001      | STA       | V100       | This instruction stores the contents of the accumulator in V100.                                 |

| 002      | LDA       | C41        | Same operations as step 000, for the contents of C41.                                            |

| 003      | STA       | V101       | Same as step 001, stored in V101.                                                                |

| 004      | LDA       | C42        | Same as step 000, for C42.                                                                       |

| 005      | STA       | V102       | Same as step 001, stored in V102.                                                                |

| 006      | HLT       |            | Computer stops. End of program.                                                                  |

NOTE: The step number column is used at the programmers's option to keep track of the program and provide a means of reference to a particular operation in the program sequence.

#### **PROBLEM 2**

Given:

A located in C40, B in C41, and C in C42.

Problem:

Write a program to solve for Y and store Y in V200:

$Y = 3A \cdot 2B + C$ .

#### Flow charts

Two flow charts are shown; both present the same solution to the problem. The first flow chart is more detailed and breaks the operations down into three computation boxes, plus a transfer box. The second flow chart places all the computations into one substitution box.

### Repertoire

| Step No. | Operation | Address | Remarks                                                                  |

|----------|-----------|---------|--------------------------------------------------------------------------|

| 000      | LDA       | C40     | Accumulator register (AR) is cleared.<br>Contents of C40 loaded into AR. |

| 001      | ADD       | C40     | A + A = 2A in AR.                                                        |

| 002      | ADD       | C40     | A + 2A = 3A  in  AR.                                                     |

| 003      | SUB       | C41     | 3A - B in AR.                                                            |

| 004      | SUB       | C41     | 3A - 2B in AR.                                                           |

| 005      | ADD       | C42     | 3A - 2B + C in AR.                                                       |

| 006      | STA       | V200    | $Y = 3A \cdot 2B + C \text{ to } V200.$                                  |

| 007      | HLT       |         | Computer stops. End of program.                                          |

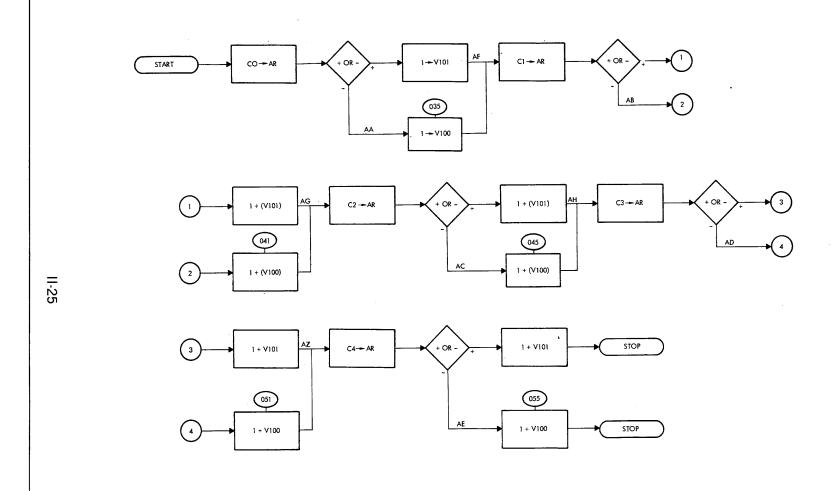

#### PROBLEM 3

Problem 3 illustrates the use of program tags. Program tags aid the programmer in jumping to an unknown program address. They are annotated with one to four alphanumeric characters, one of which must be a letter. X, X3, X123, XYZ, ABCD, XXX, and PB12 are examples of program tag notation.

Given:

Five numbers are stored in C0 through C4; C10

contains 0; C11 contains 1.

Problem:

Write a program to place the count of negative numbers

in V100, the count of positive numbers in V101.

To solve the problem, write a program that:

a. Clears addresses V100 and V101 to 0.

- b. Transfers each number to the accumulator to determine if it is positive or negative.

- c. Stores a one in V101 if the number is positive, and a one in V100 if it is negative.

Figure II-4 illustrates a flow chart that causes the computer to step sequentially through the program if all the numbers are positive. If C0 is a positive number, the program proceeds normally to store a one in V101. If C0 is negative, however, the computer must jump out of the normal sequence to store a one in V100. Therefore, provision in made in the program to jump to some other step in the case of a negative number. Since it is not known when the program is written where a negative number will occur, program tags are used. This will allow the programmer to go back and assign a program step number to the program tag.

The reference boxes in the flow chart are annotated to correspond to the step number in the repertoire that is associated with the program tag closest to that box.

VTI1-1164

Figure II-4. Flow Chart for a Positive and Negative Number Count

### Repertoire for Problem 3

| Tag | Step No. | Operation | Address  | Remarks                                                                                                                 |

|-----|----------|-----------|----------|-------------------------------------------------------------------------------------------------------------------------|

| *   | 000      | LDA       | C10      | 0 in AR.                                                                                                                |

|     | 001      | STA       | V100     | 0 in V100.                                                                                                              |

|     | 002      | STA       | V101     | 0 in V101.                                                                                                              |

|     | 003      | LDA       | CO       | Contents of CO in AR.                                                                                                   |

|     | 004      | JAN       | AA (035) | If CO is negative, jump to AA (we learn later in the program that AA is step 035 and add the step number at that time). |

|     | 005      | LDA       | C11      | 1 in AR if C0 is positive.                                                                                              |

|     | 006      | ADD       | V101     | Contents of V101 (0) to contents of AR (1).                                                                             |

|     | 007      | STA       | V101     | Contents of AR to V101.                                                                                                 |

| AF  | 010      | LDA       | C1       | Contents of C1 to AR.                                                                                                   |

|     | 011      | JAN       | AB (041) | Jumps if C1 is negative.                                                                                                |

|     | 012      | LDA       | C11      | 1 in AR if C1 is positive.                                                                                              |

|     | 013      | ADD       | V101     | Add contents of V101 to AR (1).                                                                                         |

| •   | 014      | STA       | V101     | Contents of AR to V101.                                                                                                 |

| AG  | 015      | LDA       | C2       | Contents of C2 to AR.                                                                                                   |

|     | 016      | JAN       | AC (045) | Jumps if C2 is negative.                                                                                                |

|     | 017      | LDA       | C11      | 1 in AR if C2 is positive.                                                                                              |

### Repertoire for Problem 3 (continued)

| Tag | Step No. | Operation | Address  | Remarks                                     |

|-----|----------|-----------|----------|---------------------------------------------|

|     | 020      | ADD       | V101     | Add contents of V101 to AR (1).             |

|     | 021      | STA       | V101     | Contents of AR to V101.                     |

| АН  | 022      | LDA       | C3       | Contents of C3 to AR.                       |

|     | 023      | JAN       | AD (051) | Jumps if C3 is negative.                    |

|     | 024      | LDA       | C11      | 1 in AR if C3 is positive.                  |

|     | 025      | ADD       | V101     | Add contents of V101 to AR (1).             |

|     | 026      | STA       | V101     | Contents of AR to V101.                     |

| ΑI  | 027      | LDA       | C4       | Contents of C4 to AR.                       |

|     | 030      | JAN       | AE (055) | Jumps if C4 is negative.                    |

|     | 031      | LDA       | C11      | 1 in AR if C4 is positive.                  |

|     | 032      | ADD       | V101     | Add contents of V101 to AR (1).             |

|     | 033      | STA       | V101     | Contents of AR to V101.                     |

|     | 034      | HLT       |          | Stops here if C4 is positive.               |

| AA  | 035      | LDA       | C11      | 1 in AR if C0 is negative.                  |

|     | 036      | ADD       | V100     | Contents of V100 (0) to contents of AR (1). |

|     | 037      | STA       | V100     | Contents of AR to V100.                     |

|     | 040      | JMP       | AF (010) | Jumps back to bring in C1.                  |

| AB  | 041      | LDA       | C11      | 1 in AR if C1 is negative.                  |

|     | 042      | ADD       | V100     | Contents of V100 added to                   |

|     |          |           |          |                                             |

### Repertoire for Problem 3 (continued)

| Tag | Step No. | Operation | Address  | Remarks                         |

|-----|----------|-----------|----------|---------------------------------|

|     |          |           |          | contents of AR (1).             |

|     | 043      | STA       | V100     | Contents of AR to V100.         |

|     | 044      | JMP       | AG (015) | Jumps back to bring in C2.      |

| AC  | 045      | LDA       | C11      | 1 in AR if C2 is negative.      |

|     | 046      | ADD       | V100     | Add contents of V100 to AR (1). |

|     | 047      | STA       | V100     | Contents of AR to V100.         |

|     | 050      | JMP       | AH (022) | Jumps back to bring in C3.      |

| AD  | 051      | LDA       | C11      | 1 in AR if C2 is negative.      |

|     | 052      | ADD       | V100     | Add contents of V100 to AR (1). |

|     | 053      | STA       | V100     | Contents of AR to V100.         |

|     | 054      | JMP       | AI (027) | Jumps back to bring in C4.      |

| ΑE  | 055      | LDA       | C11      | 1 in AR if C4 is negative.      |

|     | 056      | ADD       | V100     | Add contents of V100 to AR (1). |

|     | 057      | STA       | V100     | Contents of AR to V100.         |

|     | 060      | HLT       |          | Stops here if C4 is negative.   |

### To review this program:

a. In Step 003, the first number (C0) is transferred to the accumulator. A count will be stored in either of two locations, depending upon whether this number is positive or negative.

- b. In Step 004, the program states that if the number is negative, it will be dealt with during a later portion of the program. The step number is not available yet, so the programmer tags the point as AA and puts a reference box above the function box on the flow chart.

- c. Continue the program as though C0 and all the other words are positive, but a decision box and alternate branch are charted following each function box annotated to show the transfer of a word in the AR.

- d. At Step 034, a stop operation is programmed. To be complete, the program must now store a count of the negative numbers.

- e. At the first negative number, the computer was directed to jump to AA.

- (1) The programmer can now assign a program step number to AA; this is Step 035.

- (2) He goes back to Step 004 and indicates that the address of tag AA is Step 035.

- (3) He must also complete a cross reference to indicate that Step 035 is AA by placing AA in the column to the left of the step number.

- f. Assuming that C0 was negative, a one must be stored in V100; this is Step 037.

- (1) The computer must return to examine the second number at Step 010.

- (2) The programmer programs an Unconditional Jump (JMP) to tag AF.

- g. Looking back to where the second number (C1) was brought into the accumulator, he finds that this is Step 010. He tags Step 010 with an AF.

- h. He continues with this procedure until he has stored a count of all negative numbers in V100 and then programs a HLT operation at Step 060.

#### 3.4 MACHINE LANGUAGE

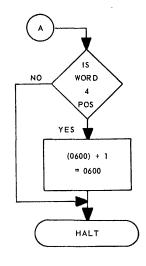

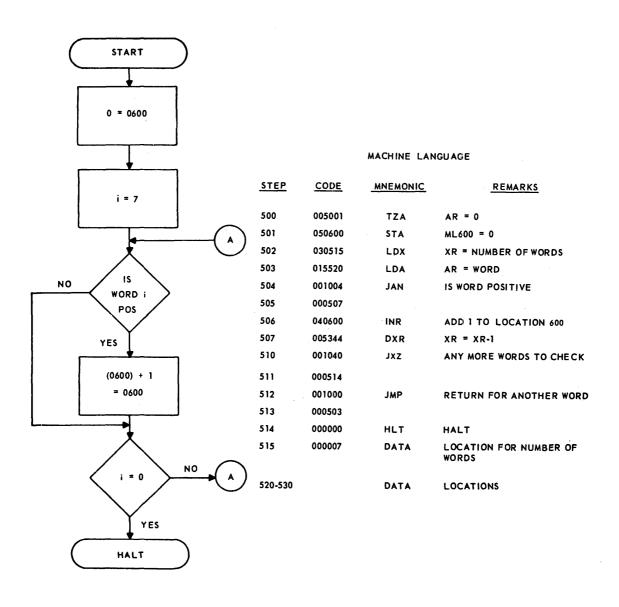

Figures II-5 and II-6 apply flow diagrams to problems involving decisions. The problem is to make a flow diagram and write the machine language for a program that will count the number of positive numbers contained in a group of four core memory words. The count is kept in location 600.

Machine language programs are written in the language that a specific computer understands. In the following programs, the code column numbers are the machine language; the mnemonics are nothing more than a memory aid. Refer to the table in figure II-5 for an example of a program using machine language.

#### 3.5 LOOPING

Problems programmed for computer solutions have some repetitious aspects; a repetitious process drawn on a flow chart appears as a loop. A single flow chart can have several loops, and loops can be nested within one another.

Looping indicates a return to an earlier operation thus avoiding a sequence of almost identical operation boxes. When the return is made, the computation will involve either a new data item or a new estimate of a computed quantity. The operation will remain the same, however. Looping is used in solving the problem illustrated in the flow chart in figure II-6.

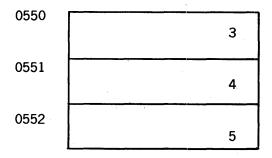

#### 3.6 INDEXING

Index registers reference a sequence of memory addresses and are used in nonloop situations to permit rapid access to tables in memory and to enable branches beyond range limits. Thus, indexing permits a number of operations to be executed rapidly.

In previous examples involving memory storage and various mathematical processes, subscripts were generally assigned to the variables. Operations to be performed were indicated in terms of these subscripts. For example,  $a_i$  represented the i value of a series of numbers a. To indicate that, after  $a_i$  was processed  $a_i + 1$  was to be processed, operation on the subscript was required: i + 1 = i. This means that 1 is to be added to the subscript, which generates the address to the next number.

To process a; as indicated, it is necessary to modify the appropriate instructions. They can be modified by treating them as data and adding 1 to the operation and addresses once each loop cycle. Three operations on the index register are required:

#### MACHINE LANGUAGE

| STEP    | CODE   | MNEMONIC | REMARKS               |

|---------|--------|----------|-----------------------|

| 500     | 005001 | TZA      | AR-0                  |

| 501     | 050600 | STA      | AR ML 600             |

| 502     | 010530 | LDA      | AR = WORD 1           |

| 503     | 001004 | JAN      | IS WORD NEGATIVE      |

| 504     | 000506 |          |                       |

| 505     | 040600 | INR      | ADD 1 TO LOCATION 600 |

| 506     | 010531 | LDA      | AR = WORD 2           |

| 507     | 001004 | JAN      | IS WORD 2 NEGATIVE    |

| 510     | 000512 |          |                       |

| 511     | 040600 | INR      | ADD 1 TO LOCATION 600 |

| 512     | 010532 | LDA      | AR = WORD 3           |

| 513     | 001004 | JAN      | IS WORD 3 NEGATIVE    |

| 514     | 000516 |          |                       |

| 515     | 040600 | INR      | ADD 1 TO LOCATION 600 |

| 516     | 010533 | LDA      | AR = WORD 4           |

| 517     | 001004 | JAN      | IS WORD 4 NEGATIVE    |

| 520     | 000522 |          |                       |

| 521     | 040600 | INR      | ADD 1 TO LOCATION 600 |

| 522     | 000000 | HLT      | HALT                  |

| 530-533 |        | DATA     | LOCATIONS             |

VT11-1165

Figure II-5. Count of Positive Numbers

VT11-1166

Figure II-6. Loop Program

a. Setting the index register1 = i

b. Increasing or decreasing the index register i + 1 = i or  $i \cdot 1 = i$

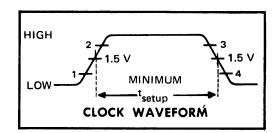

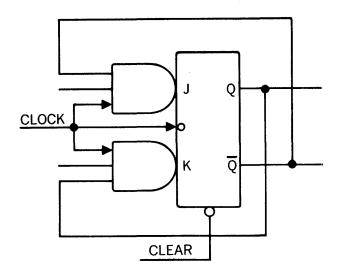

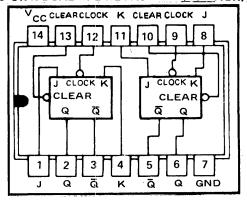

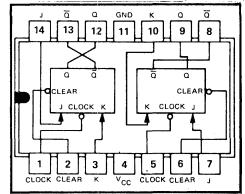

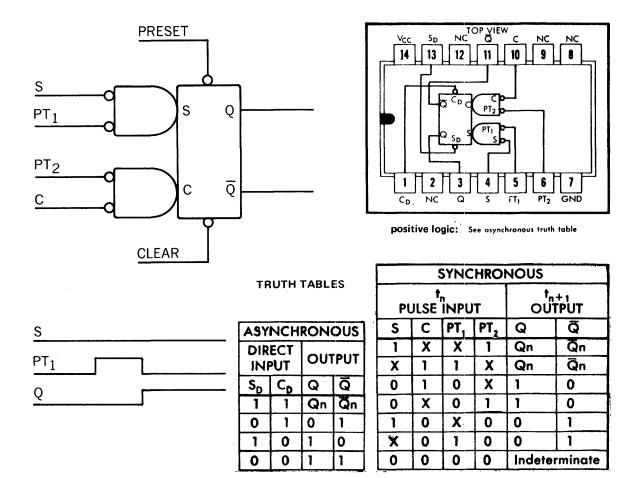

c. Testing the value of the index register  $(i \cdot n) = 0$