| varian | data | machines | (1 |

|--------|------|----------|----|

|--------|------|----------|----|

### VARIAN MICROPROGRAMMING

GUIDE

Specifications are subject to change without notice. Address comments regarding this document to Varian Data Machines, Publications Department, 2722 Michelson Drive, Irvine, California, 92664.

#### **PREFACE**

Preface (about the guide itself -- prerequisites, its organization and why).

Microprograms are aptly called **firmware** to place them between the realms of software and hardware. Where those two conventional divisions of a computer overlap is an area which provides many of the best features of both. The use and benefits of microprogramming depend upon the user having an understanding of both and their complex interaction.

The reader of this guide should have some knowledge of the hardware components of a computer system, such as the functions and uses of registers, schemes of handling interrupts etc. Programming techniques which make efficient assembly-language functions like indexing and high-speed algorithms will be useful here too. When a microprogram is executed thousands of times more often than any one application program, its fine tuning is also needed that many more times. Also the microprogrammer should know the problem-oriented languages used. To choose which operators to microprogram, the designer must be aware of the eventual applications. Combining operators which are often used in the same sequence could form a single microprogrammed operator with a greater overlapping of actions.

All components of a computer system seem to be increasingly complex yet easier and easier to use. Though microprogramming adds more complexity the result is to make a system easier to use. One goal of this guide is to bring microprogramming into the range of a good programmer. To that end the guide is written in simple language (with a minimum of exotic terms and a glossary to look up any of those) and a gradual progression from the big picture to the details through numerous examples. The examples are annotated and explained with the same tools that will aid in the planning as well as understanding.

This guide is both an introduction and a reference. If microprogramming is new to you, start at the beginning of this guide and use it as a tutorial. Later the book can be used for reference. The charts and examples are built up in a logical development so that the complete examples will be a pattern for your programming.

Varian Data Machines does not assume responsibility for microprograms written and implemented according to the recommendations outlined herein.

To improve the usefulness of this guide please return the reader questionaire in the back after reading and using this volume.

#### **Related Documentation**

The Writable Control Store manual (98 A 9906 08x) provides information about the installation, theory of operation, maintenance and test programs for the hardware storage of microprograms.

Information about the Varian 70 series processor is contained in the applicable system handbook and in more detail in the Processor Manual (98 A 9906 02x). The VORTEX Reference Manual (98 A 9952 10x) decribes the use of the VORTEX operating system. The MOS (Master Operating System) Reference Manual (98 A 9952 09x) provides similar information necessary to use microprogramming software with that operating system. (The x at the end of each document part number is the revision number and can be any digit 0 through 9.).

The following Varian manuals provide additional aids to the understanding of Varian Computer Systems.

| Title                       | Document Number |

|-----------------------------|-----------------|

| 72 System Handbook          | 98 A 9906 20x   |

| 73 System Handbook          | 98 A 9906 01x   |

| 74 System Handbook          | 98 A 9906 21x   |

| Core Memory Manual          | 98 A 9906 03x   |

| Semiconductor Memory Manual | 98 A 9906 04x   |

| Option Board Manual         | 98 A 9906 05x   |

| Power Supply Manual         | 98 A 9906 06x   |

## **TABLE OF CONTENTS**

| PREFACE                                    | iji  |

|--------------------------------------------|------|

| SECTION 1 INTRODUCTION                     |      |

| 1.1 ADVANTAGES                             | 1-1  |

| 1.2 GUIDE TO THIS MANUAL                   | 1.2  |

| 1.3 NOTATION IN THIS MANUAL                | 1.2  |

| 1.4 COMPONENTS                             | 1-3  |

| 1.4.1 Hardware for Microprogrammed Systems | 1.3  |

| 1.4.2 Writable Control Store               | 1.6  |

| 1.4.3 Software Modules                     | 1.8  |

| SECTION 2<br>CAPABILITIES                  |      |

| 2.1 GENERAL MICROINSTRUCTIONS              | 2-1  |

| 2.2 DATA TRANSFER AND                      |      |

| TRANSFORMATION                             | 2.2  |

| 2.2.1 ALU Input Sources                    | 2.2  |

| 2.2.2 ALU Functions                        | 2-8  |

| 2.2.3 ALU Output Destinations              | 2-11 |

| 2.2.4 Other Registers                      | 2-12 |

| 2.3 ADDRESSING                             | 2-13 |

| 2.3.1 General                              | 2-13 |

| 2.3.2 Normal Addressing                    |      |

| 2.3.3 Field Selection Addressing           | 2-13 |

| 2.3.4 Test Addressing                      | 2-14 |

| 2.3.4.1 Conditions                         | 2-15 |

| 2.3.4.2 Addresses in Branches              |      |

| 2.3.5 Page Jump Addressing                 |      |

| 2.3.6 Interrupt Addressing                 |      |

| 2.4 MAIN MEMORY CONTROL                    |      |

| 2.4.1 Unconditional Cycle Initiation       |      |

| 2.4.2 Conditional Cycle Initiation         |      |

| 2.4.3 Special Transfer                     |      |

| 2.4.4 Wait for Memory Done                 |      |

| 2.5 MICROPROGRAMMING EXAMPLE               |      |

| 2.6 TIMING CONSIDERATIONS                  |      |

| 2.7 ADDITIONAL CAPABILITIES                |      |

| 2.7.1 Register Field Control               |      |

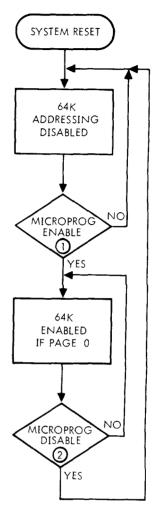

| 2.7.2 Memory Addressing to 64K             |      |

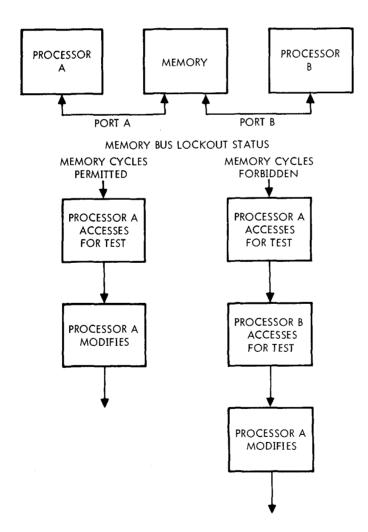

| 2.7.3 Memory Bus Lockout Status            |      |

| 2.7.4 Stack Use                            | 2-28 |

| 2.7.5 Memory Addressing Using the          |      |

| Optional Memory Map                        |      |

| 2.7.6 Memory Protection                    |      |

| 2.7.7 Address Comparator Logic             | 2-29 |

| 2.8 QUESTIONS ABOUT                        | 0.00 |

| MICROPROGRAMMING CAPABILITIES              | Z-30 |

## SECTION 3 TECHNIQUES

| 3.1 INTERFACE WITH 620 EMULATION               | <b>3</b> -1 |

|------------------------------------------------|-------------|

| 3.1.1 Execution of User Microprograms          |             |

| 3.1.2 Steps in Instruction Execution           | 3-1         |

| 3.1.3 Instruction Pipeline                     | <b>3</b> -1 |

| 3.1.4 ROM Standard States                      | 3.2         |

| 3.1.5 Summary of Branches Between WCS and      |             |

| ROM Control Store                              | 3.2         |

| 3.1.6 Varian 73 Register Usage                 | 3.3         |

| 3.2 FLOW DIAGRAM                               | 3.3         |

| 3.2.1 Rationale                                | 3.3         |

| 3.2.2 Format                                   | 3.3         |

| 3.3 FLOW DIAGRAM MNEMONICS                     | 3-5         |

| 3.4 FLOW DIAGRAM EXAMPLES                      |             |

| 3.4.1 BCS Entry Point Initialization           |             |

| 3.4.2 Memory-to-Memory Block Move              |             |

| 3.4.3 Reentrant Subroutine Call and Return     | 3-8         |

| 3.4.4 64K-Memory ADD to any of the             |             |

| General-Purpose Registers                      | 3-11        |

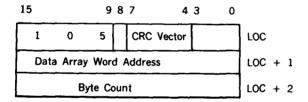

| 3.4.5 Cyclic Redundancy Check (CRC) Generation | 3-15        |

| SECTION 4                                      |             |

| MICROPROGRAM DATA ASSEMBLER, MID               | AS          |

| 4.1 BASIC ELEMENTS                             | 4-1         |

| 4.2 GENERAL FORM OF STATEMENTS                 | 4-2         |

| 4.3 STATEMENT DEFINITIONS                      | 4-2         |

| 4.3.1 Format Statement                         | 4-2         |

| 4.3.2 Program Statement                        | 4-3         |

| 4.3.3 Assembler Directives                     | 4-5         |

| 4.3.4 Comment                                  | 4-6         |

| 4.4 ASSEMBLY-LANGUAGE EXAMPLES                 |             |

| 4.5 MACRO CAPABILITY                           | 4-7         |

| 4.6 OPERATING INSTRUCTIONS                     | 4-8         |

| 4.6.1 VORTEX Environment                       | 4.8         |

| 4.6.2 MOS Environment                          | 4-8         |

| 4.6.3 Stand-Alone Environment                  | 4.8         |

| 4.7 ASSEMBLER INPUT AND OUTPUT                 | 4.0         |

| 4.8 ASSEMBLY ERROR MESSAGES                    | 4.9         |

## SECTION 5 **CODING FROM FLOW DIAGRAMS**

| 5.1   | GENERAL                                 | 5-l  |

|-------|-----------------------------------------|------|

| 5.2   | EXAMPLES OF MICROPROGRAMS IN            |      |

|       | ASSEMBLY LANGUAGE                       | 5-5  |

| 5.2.1 | BCS Entry Point Initialization          | 5-6  |

| 5.2.2 | Memory-to-Memory Block Move             | 5.9  |

| 5.2.3 | Reentrant Subroutine Call and Return    | 5-12 |

| 5.2.4 | 64K Add to General-Purpose Register     | 5-15 |

| 5.2.5 | Cyclic Redundancy Check Generation      | 5-16 |

|       |                                         |      |

|       | SECTION 6                               |      |

|       | MICROPROGRAM SIMULATOR, MICSIM          |      |

| 6.1   | BASIC ELEMENTS                          | 6.1  |

| 6.2   | GENERAL FORM OF STATEMENTS              |      |

| 6.3   | STATEMENT DEFINITIONS                   |      |

| 6.3.1 | Select Input Media (M)                  |      |

| 6.3.2 | •                                       |      |

| 6.3.3 |                                         |      |

| 6.3.4 |                                         |      |

| 6.3.5 | Alter/Display Simulator Registers (A)   |      |

| 6.3.6 |                                         |      |

| 6.3.7 |                                         |      |

| 6.3.8 |                                         |      |

| 6.3.9 |                                         |      |

| 6.3.1 |                                         |      |

| 6.3.1 | ` '                                     |      |

| 6.3.1 |                                         |      |

| 6.3.1 |                                         |      |

| 6.3.1 | •                                       |      |

| 6.4   | OPERATING INSTRUCTIONS                  |      |

| 6.4.1 | Program Loading                         |      |

| 6.4.2 | Initial Condition Selection             | 6-8  |

| 6.4.3 | Loading Simulator Central Control Store |      |

|       | (CCS) and Decoder Control Store (DCS)   | 6-8  |

| 6.4.4 | Other Control (As Required)             | 6-9  |

| 6.5   | PROGRAM EXECUTION                       | 6-9  |

| 6.6   | AFTER SIMULATION                        | 6.9  |

| 6.6.1 | Control Store Dump                      | 6-9  |

| 6.6.2 | [nitialization                          | 6-9  |

| 6.6.3 | Return to MOS, VORTEX                   | 6.9  |

| 6.7   | 620 EMULATION                           | 6.9  |

| 6.8   | MAIN MEMORY SIMULATION                  | 6-9  |

| 6.9   | SIMULATOR ERROR MESSAGES                | 5-10 |

| 6.10  | EXAMPLE OF SIMULATOR OUTPUT             | 5-11 |

## SECTION 7 MICROPROGRAM UTILITY PROGRAM, MIUTIL GENERAL FORM OF DIRECTIVE.......7-1 Select Page (P)......7-1 Load Control Store (L)......7-1 Dump Control Store (D)......7-2 Media Set and Reset (M)......7-2 7.3.6 Trace Execution (T)......7-2 Set Micro Execution Address (G)......7-3 Initialize WCS (I)......7-3 Set Halt Address (H)......7-4 **SECTION 8** DECODER CONTROL STORE, I/O CONTROL AND ADDITIONAL TOPICS DECODER CONTROL STORE......8-1 8.2 I/O CONTROL STORE.......8-3

# SECTION 9 GLOSSARY

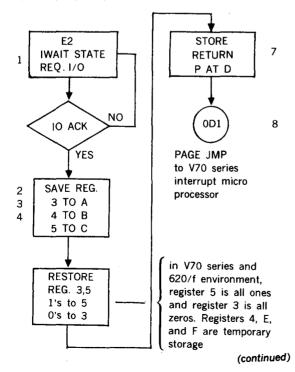

Example of I/O Microprogram:

8.3 MULTIPLE ENVIRONMENT APPLICATIONS .......8-8

Clear and Input to A......8-7

## LIST OF ILLUSTRATIONS

| Figure 1-1. | Simplified Comparison of a Microprogrammed       |      |

|-------------|--------------------------------------------------|------|

|             | and a Conventional Computer                      | 1.4  |

| Figure 1-2. | Varian 73 Processor Block Diagram                | 1-4  |

| Figure 1-3. | Varian 73 Processor Data Paths                   | 1.5  |

| Figure 1-4. | Writable Control Store Block Diagram             | 1.7  |

| Figure 1-5. | Steps for Realizing Microprograms                | 1-8  |

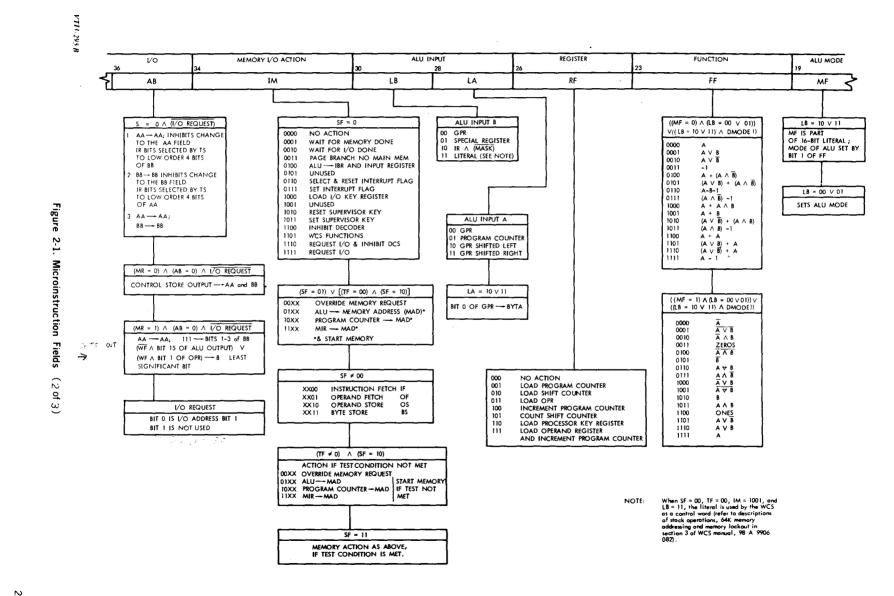

| Figure 2-1. | Microinstruction Fields (1 of 3)                 | 2-2  |

| Figure 2-1. | Microinstruction Fields (2 of 3)                 | 2-3  |

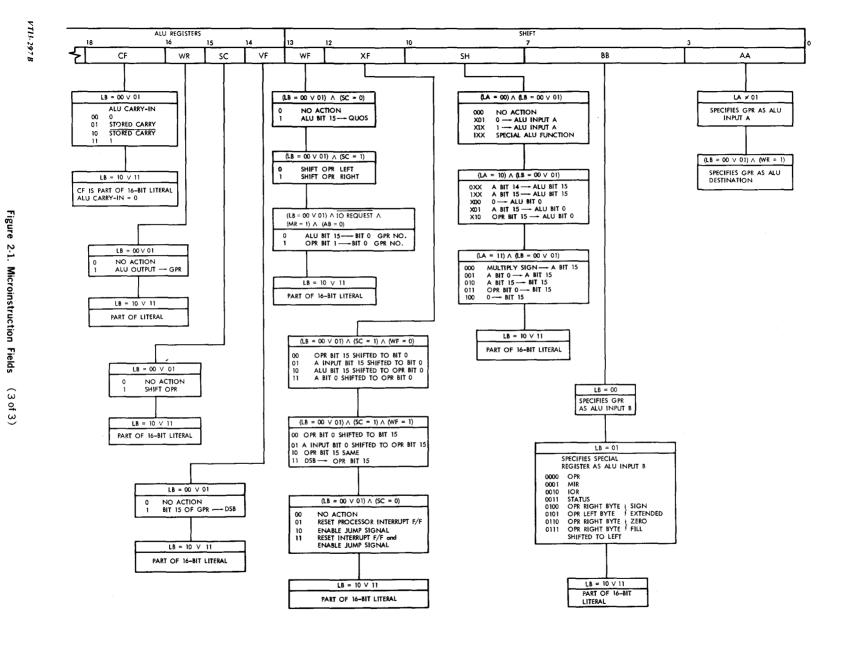

| Figure 2-1. | Microinstruction Fields (3 of 3)                 | 2-4  |

| Figure 2-2. | General-Purpose Registers, Operand Register      |      |

|             | and ALU Input                                    | 2-7  |

|             | Field Selection Address Contribution             |      |

| Figure 2-4. | Coding Example of an Operand-Store Sequence      | 2-19 |

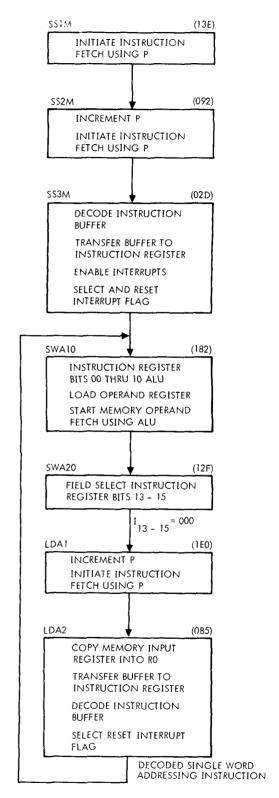

| Figure 2-5. | Flowchart for LDA Instruction                    | 2-23 |

| Figure 2-6. | Flow Diagram of LDA Instruction                  | 2-24 |

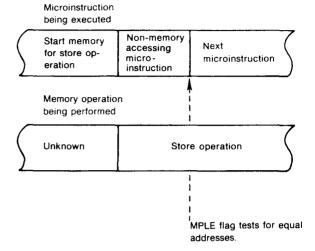

| Figure 2.7. | Flowchart of Memory Address Control              | 2-27 |

| Figure 2-8. | Memory Bus Lockout                               | 2-28 |

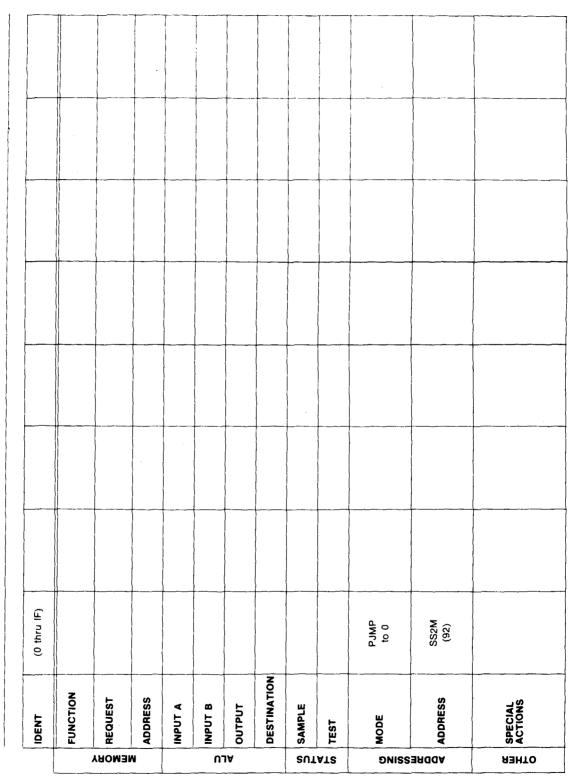

| Figure 3-1. | Sample Flow Diagram Form                         | 3-4  |

| Figure 3-2. | Flow Diagram for BCS Entry Point Initialization  | 3-9  |

| Figure 3-3. | Flow Diagram for Memory-to-Memory Block Move     | 3-10 |

| Figure 3-4. | Flow Diagram for Subroutine Call                 | 3-12 |

| _           | Flow Diagram for Subroutine Return               |      |

| Figure 3-6. | ADD from 64K-Memory to General-Purpose Register  | 3-14 |

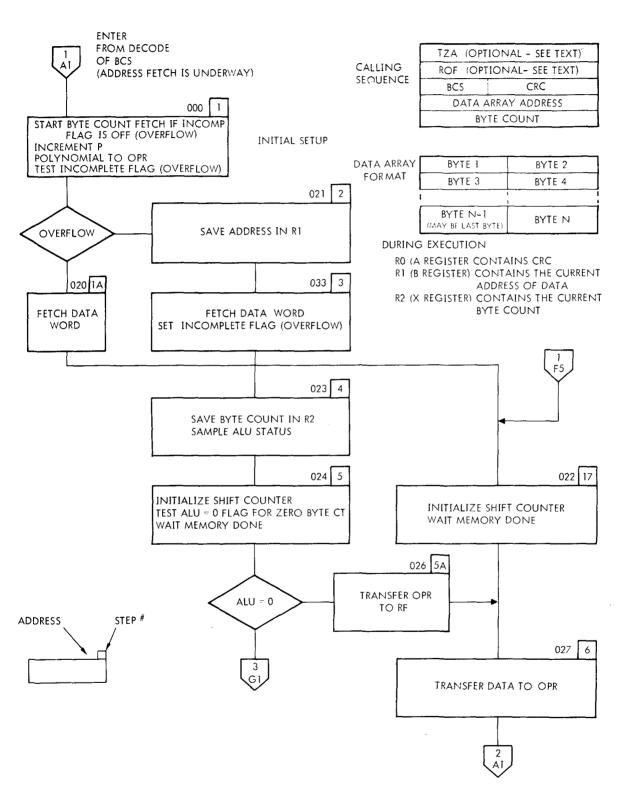

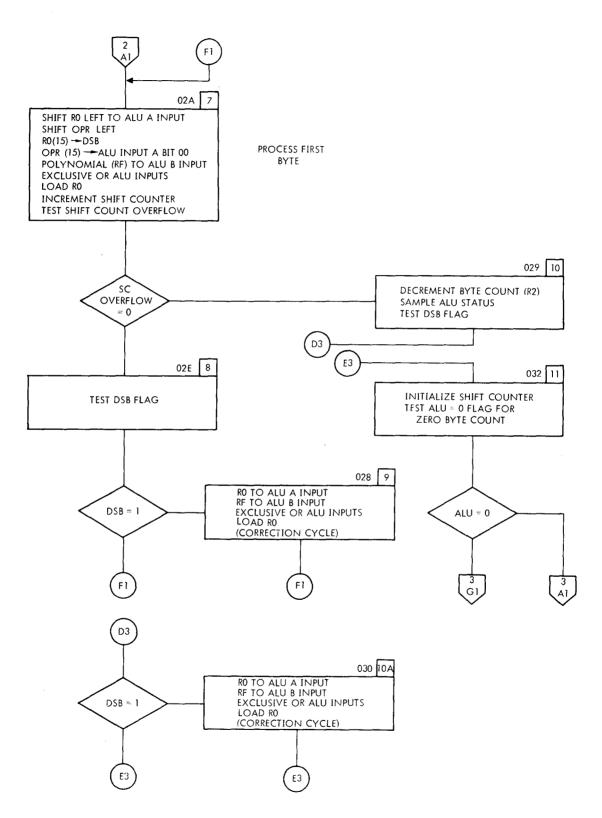

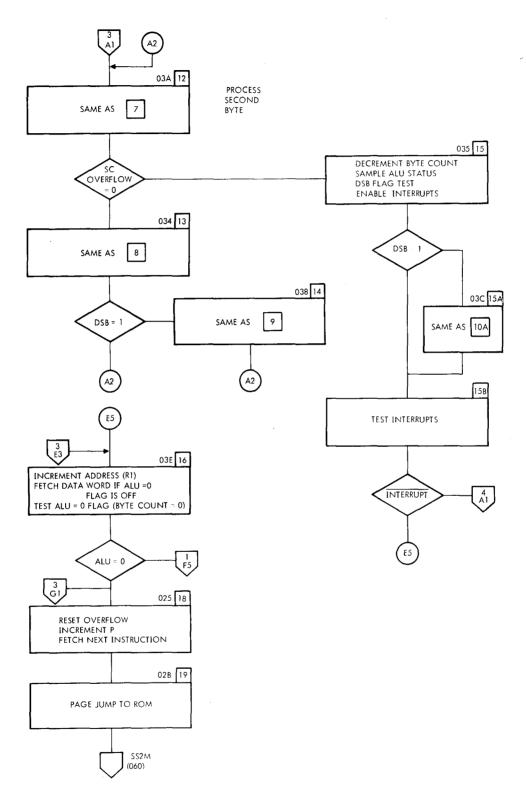

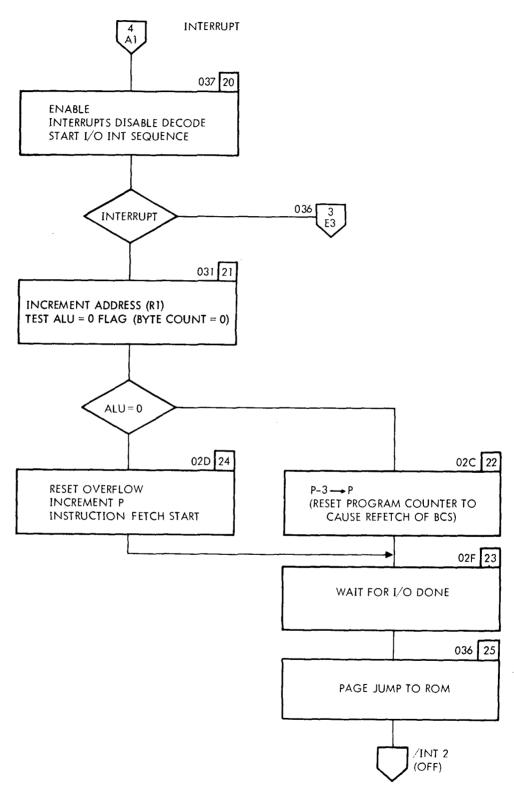

| Figure 3.7. | Flowchart for Cyclic Redundancy Check Generation |      |

|             | Microprogram (1 of 4)                            | 3-18 |

| Figure 3-7. | Flowchart for Cyclic Redundancy Check Generation |      |

|             | Microprogram (2 of 4)                            | 3-19 |

| Figure 3.7. | Flowchart for Cyclic Redundancy Check Generation |      |

|             | Microprogram (3 of 4)                            | 3-20 |

| Figure 3-7. | Flowchart for Cyclic Redundancy Check Generation |      |

|             | Microprogram (4 of 4)                            |      |

|             | Flow Diagram of CRC Generation (1 of 4)          |      |

|             | Flow Diagram of CRC Generation (2 of 4)          |      |

|             | Flow Diagram of CRC Generation (3 of 4)          |      |

| -           | Flow Diagram of CRC Generation (4 of 4)          |      |

| Figure 4-1. | Predefined Formats Recognized by MIDAS           | 4.3  |

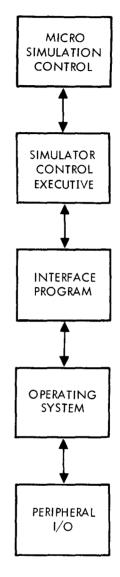

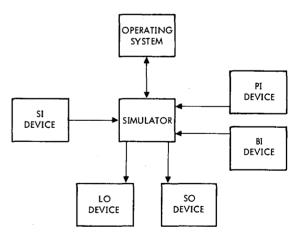

| Figure 6-1. | Microsimulator Control Flow                      | 6-1  |

| Figure 6-2. | Microsimulator Data Flow                         | 6-7  |

| Figure 6-3. | Simulator Output Format                          | 6-11 |

| _           | Simulator Output Format (continued)              |      |

|             | Simulator Output Format (continued)              |      |

|             | Simulator Output Format (continued)              |      |

| Figure 6-3. | Simulator Output Format (continued)              | 6-15 |

## LIST OF ILLUSTRATIONS (continued)

| Figure 6-3. Simulator Output Format (continued)                     | .6 16  |

|---------------------------------------------------------------------|--------|

| Figure 6-3. Simulator Output Format (continued)                     | 6-17   |

| Figure 6-3. Simulator Output Format (continued)                     | 6-18   |

| Figure 6-3. Simulator Output Format (continued)                     | 6-19   |

| Figure 6-3. Simulator Output Format (continued)                     | 6-20   |

| Figure 6-3. Simulator Output Format (continued)                     | 6-21   |

| Figure 6-3. Simulator Output Format (continued)                     | 6-22   |

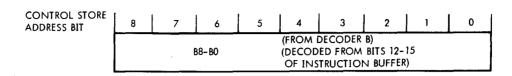

| Figure 8-1. Decoder Control Store Format                            | 8-2    |

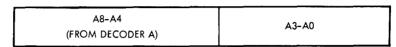

| Figure 8-2. Decoder Address Components                              |        |

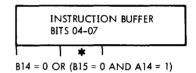

| Figure 8-3. I/O Microinstruction Format                             | _      |

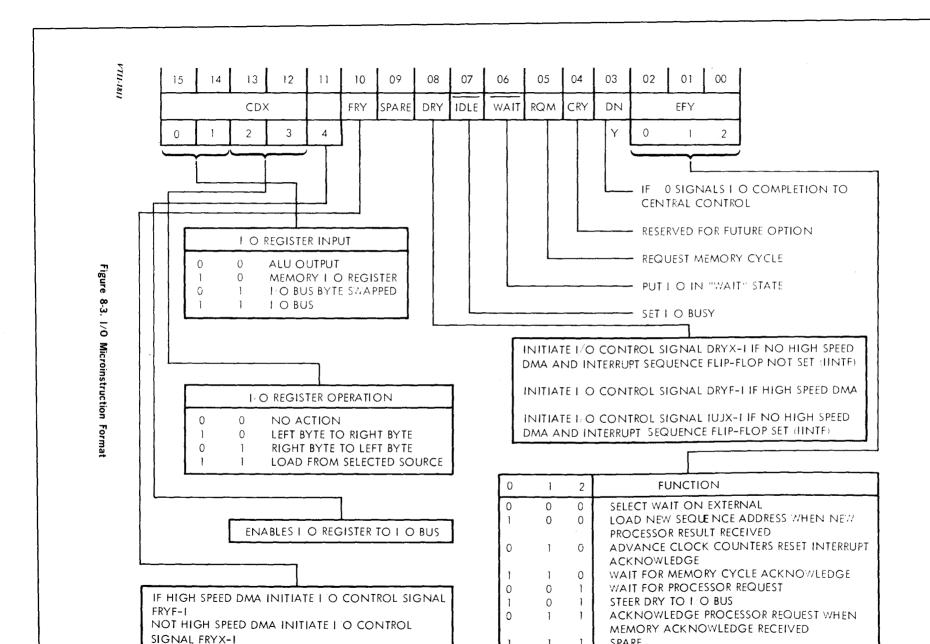

| Figure 8-4. I/O Control Simplified Block Diagram                    |        |

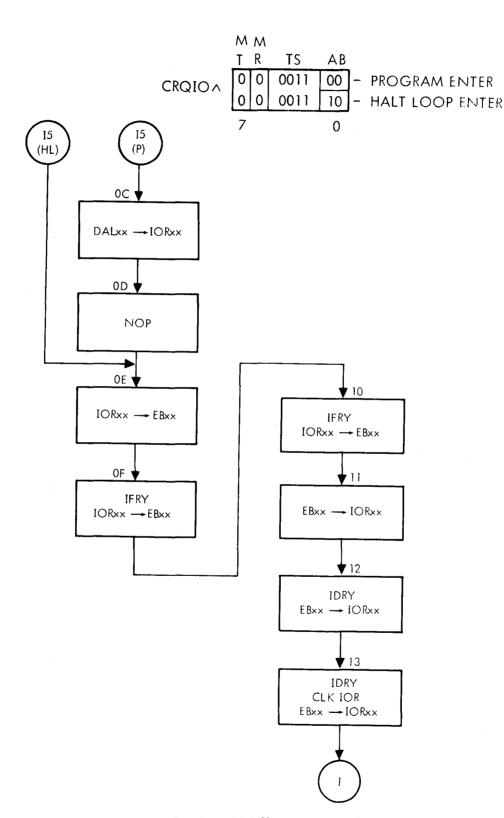

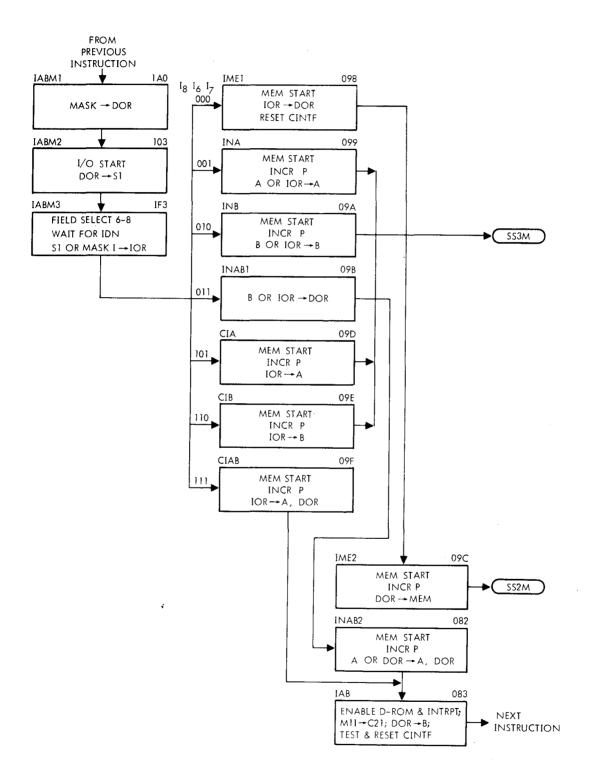

| Figure 8-5. Flowchart of I/O Microprogramming Example               |        |

| Figure 8-5. Flowchart of I/O Microprogramming Example (continued)   | 8-10   |

| 1107 05 707170                                                      |        |

| LIST OF TABLES                                                      |        |

| Table 2-1. ALU Input A Bus Selections                               | 2-6    |

| Table 2-2. ALU Input B Bus Selections                               | 2.8    |

| Table 2-3. ALU Operations                                           | . 2.9  |

| Table 2-4. Carry Flag Settings                                      |        |

| Table 2-5. ALU Output Data Destination                              | 2-11   |

| Table 2-6. Operand Register Shift Operations                        | .2-12  |

| Table 2-7. Overflow Flag Control                                    | . 2-16 |

| Table 2-8. Memory Operations                                        | .2-20  |

| Table 2-9. Register Field Control                                   | 2-26   |

| Table 2-10. Register Field Selection                                | 2-26   |

| Table 3-1. Mnemonics for Microprogramming Flow Diagrams             | 3.5    |

| Table 3-1. Mnemonics for Microprogramming Flow Diagrams (continued) |        |

| Table 3-1. Mnemonics for Microprogramming Flow Diagrams (continued) |        |

| Table 5-1. Conversion Table                                         | 5-1    |

| Table 5-1. Conversion Table (continued)                             | 5-2    |

| Table 5-1. Conversion Table (continued)                             | 5-3    |

| Table 5-1. Conversion Table (continued)                             | 5-4    |

| Table 5-2. User-Defined Opcodes                                     | 5.4    |

| Table 5-2. User-Defined Opcodes (continued)                         | 5-5    |

| Table 6-1. Summary of Microprogram Simulator Directives             | . 6-1  |

| Table 6-1. Summary of Microprogram Simulator Directives (continued) | 6-2    |

| Table 7-1. Summary of Utility Directives                            | . 7-1  |

| Table 8-1. I/O Microprogram Example Code                            | . 8-8  |

# SECTION 1 INTRODUCTION

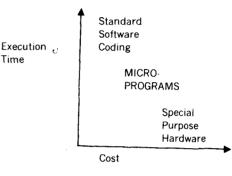

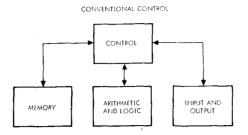

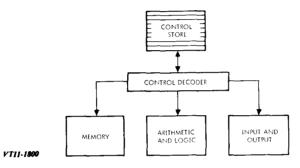

Most of this book discusses how to microprogram. As an incentive to read further, here are some general reasons why to microprogram. The advantages of microprogramming are based upon a comparison with a conventional system either completely without microprogramming or where it is not accessible (figure 1-1). After a brief summary of the advantages a comparison with a conventional system gives more details and a specific picture of a microprogrammed operation.

#### 1.1 ADVANTAGES

A basic reason to microprogram is the one stated at first. The initial idea was proposed for a "systematic" approach to the "usual somewhat ad hoc procedure" used to design the control system of a machine. The narrow view in the design of either software or hardware without an awareness of the other can lead to a less efficient functioning, like a refrigerator converted into a vacuum cleaner — there may be some common useful parts but we would push around a great deal that did not help the vacuuming. Good basic operators which match the eventual application will improve the entire efficiency.

The usual random logic can be reduced with a more structured organization. A conventional computer system uses a collection of counters, special flip-flops, decoding networks and other components unique to a particular purpose for control logic. In contrast a microprogrammed memory replaces most of this. The microprogram storage is formed of regular and repetitive units. There are fewer components thus increasing the reliability of the system.

The flexibility of the instructions in the control store offers the ability to change the system in ways so basic that they are not at all feasible in a fixed instruction set. Field changes can be made by merely changing the controlling microprograms. Final systems definition can be postponed until a later stage of the design. Performance can be economically expanded at a lower cost.

Emulation of a number of diverse devices, not only processors but peripheral controllers for instance, can be carried out on a single microprogrammed system. Simultaneous emulation of some devices can be made or the target system can be changed depending upon needs. This would save some reprogramming and retraining and yet gain the speed and reliability of a more advanced system. Also the documentation and minor logistic problems of a new machine would be avoided.

For more reliability and the continuous performance necessary in many uses of computers, diagnostics and servicing aids may be implemented in the control store. To pinpoint problems the microprocessor can both test and set states not available to the assembly-language programmer on a conventional machine.

#### Instructions Tailored To Particular Environments

In general, microprogrammed instructions permit more compact program representation. They use less main memory than the equivalent would in conventional code. Consequently, fewer memory fetches for anything other than data are needed.

As an example of a possible microprogrammed operator which reduces memory fetches, consider a common use of arrays. Higher-level programming languages, such as FORTRAN, BASIC, COBOL — in fact, nearly all — have facilities for expressing a repetitive linear data structure, a list or array. Arrays are an integral part of a large class of techniques for diverse problems. Yet good operators for arrays as such are not available as simple, single instructions in a conventional machine.

In usual machine code the function of adding two numerical arrays of the same size and number of elements usually requires a series of actions as follows for each pair of elements:

- a. load memory to register

- b. add memory to register

- c. store register result in memory

- d. update indices and close loop

The first two steps would each require a memory fetch and the last step as many as three memory fetches.

A microprogrammed instruction would provide initializing data descriptors and repetitively executing micro-operators

over the described arrays of data. To start the program segment would require several steps:

- a. load the starting address, increment and extent of each array

- b. load the result's starting address, increment and extent

- c. define the end and branch condition

This initialization could be followed by one instruction to execute the newly-defined operator equivalent to the series of typical instructions.

An extension of this principle of reducing memory retrieval of instructions occurs in some special cases where data normally resident in the stream of instructions can be removed and instead reside in special-purpose microroutines. For example, if the array addition algorithm above were limited to fixed-length arrays with fixed-size elements, the increment and extent parameters could be stored as local constants in the microprogram, eliminating the need to transfer this information in the initial sequence.

#### 1.2 GUIDE TO THIS MANUAL

The purpose of this section is to provide the user with a helpful idea of the structure of the remainder of the manual. The order of the following sections is based on the order in which a programmer needs the information to plan, then code, test and run microprograms.

Information in the sections

Introduction (Section 1)

Advantages of microprogramming

Guide to the remainder of the manual

Conventions (defining some words and notation) in the

manual

Components of microprogrammed systems

Capabilities (Section 2)

Micro operations available in central control store Building blocks of microprograms providing data transfer and transformations, conditional tests, and memory access

Techniques (Section 3)

Explanation of interface with the 620 emulation

Procedures to use flow diagrams to write

microprograms

Examples of microprograms

Microprogram Assembler (Section 4)

Directives to code microprograms

Macros

Operating instructions

Coding from Flow Diagrams (Section 5) Conversion steps and tables Examples from section 3 Microprogram Simulator (Section 6)

Directives

Operating instructions

Microprogram Utility (Section 7)

Directives

Operating instructions

Decoder control store, I/O control and additional topics (section 8)

Format and use of optional decoder control store I/O microprogramming procedures and example

Glossary (Section 9)

Terminology for microprogramming defined Mnemonics defined

#### 1.3 NOTATION IN THIS MANUAL

#### References to Microinstruction Fields

Within the microinstruction the fields are named with the two-letter references recognized by the micro-assembler. Some of the fields have names which are used in the text, such as the CF field conveniently called the carry field.

#### References Within Fields

The bits within the fields are often discussed one at a time. Several techniques are used to single out bits. A field may be represented with the letter X in bit positions not involved in the action being discussed. 1X for a two-bit field indicates that only the high-order bit is required to be one in this action, i.e., setting the field to 10 or 11. High-order and leftmost are synonymous to select a particular bit or group of bits. Similarly low-order and rightmost select the same bit or a contiguous set of bits. Finally less often a bit is mentioned by number with the convention that bits are numbered from right to left starting with zero.

#### Syntax of Directives

In the directive formats for the microprogramming software the syntax is given with the following conventions:

Boldface type indicates a required parameter

Italic type indicates an optional parameter

Upper-case type indicates that the item is to be entered exactly as written

Lower-case type indicates a variable and shows where the user enters a value for that variable.

The formation of a list of the same items is indicated by three consecutive periods.

For example, the syntax for the MIDAS FORM statement is as follows

label

FORM field(1), field(2),..., field(n)

Where:

label

is a symbol as defined in MIDAS

basic elements

each field

is a field identifier which is the field length in decimal, followed by an optional hexadecimal constant

enclosed in parentheses

#### Numbers

Microinstruction fields are given in binary notation unless indicated otherwise in the context of the reference.

#### **Definitions**

To remove one barrier that often exists to the understanding of microprogramming this section clarifies some terms we use.

In a computer system many different kinds of storage exist for data, instructions or both. Microprograms reside in the system's control store. All control store must be writable in some manner so that the control information can be introduced. The desire for greater speed often leads to the design of storage that can only be loaded once and even then only by mechanical or electromechanical means. These are designated as read only or ROM for read-only memory. This differentiates them from the arrays whose contents can be changed by the user. This is called writable control store (WCS).

The microprogram is a series of microinstructions. A microinstruction resides in one fixed-length word in control store. The microword is 64 bits long and selects the operations which occur in one machine cycle (with some exceptions). The individual operations, micro-operations or primitives, are defined by fields within the microword.

In this manual whenever you encounter unfamilar words look for the definition at the first use of the word or consult the glossary in section 9.

#### 1.4 COMPONENTS

#### 1.4.1 Hardware for Microprogrammed Systems

Though the software for microprogramming provides an interface for the user to program the system, to plan a good system one needs to be very aware of the actual functions of the hardware. The tangible parts of the microprogramming system are described below.

#### **Processor**

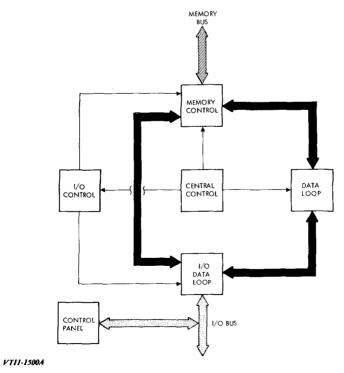

The major functional components of the Varian 70 series processor (figure 1-2) are central control, data loop, memory control, I/O data loop, and I/O control. The processor communicates with the computer control panel via the I/O bus.

The processor speed is 165 nanoseconds for a microinstruction.

#### Central Control

Central control provides supervision for most of the major components in the processor. Direct control is exercised over the data loop. Requests may be made to other components, such as memory and I/O control.

The key element in central control is a 64-bit control buffer. This buffer, which is simply a microinstruction, completely describes a set of actions for the other processor components. For example, the data loop might be instructed to increment one of the general-purpose registers. The memory control might be requested to begin the fetch of a 16-bit word from main memory. Thus, the control buffer holds the current microinstructions. It is somewhat analogous to the instruction register in assembly-language programming.

The 64 bits also specify the location of the new contents for the control buffer. The control buffer is always loaded from 64-bit central control store. Thus, execution of a microprogram basically consists of the control buffer being sequentially loaded with the appropriate 64-bit values. Central control store in a Varian 70 series system is divided into pages, each consisting of 512 64-bit words. Page zero of central control store always contains a set of microinstructions which direct the processor components to behave like a 620/f. This set of 512 microwords is thus called the 620/f emulation, and resides in read-only memory (ROM). Other central control store pages may be added with the writable control store (WCS) option, thus allowing the user to specify in detail the actions of the processor components.

The microprograms for the standard instruction set are described in the microinstruction flowcharts in the System Maintenance Manual and in assembly language in an appendix to this guide.

#### Data Loop

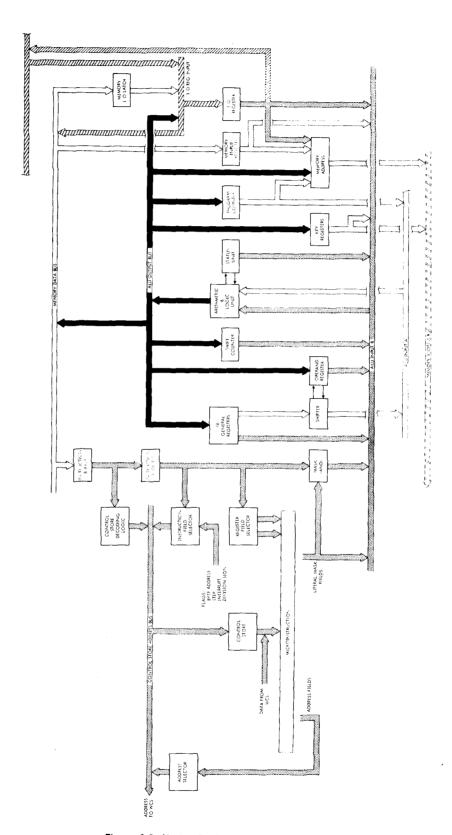

The data loop provides transfer paths, data transformation circuits, storage registers and counters (figure 1-3).

Under control of the central control buffer the arithmetic and logic unit (ALU) performs basic arithmetic functions

SIMPLIFIED GENERAL MICROPROGRAMMING

Figure 1-1. Simplified Comparison of a Microprogrammed and a Conventional Computer

Figure 1-2. Varian 73 Processor Block Diagram

VT13-292

Figure 1-3. Varian 73 Processor Data Paths

such as addition, subtraction, and the common logical functions including AND and OR. ALU output can be directed to a number of places, including registers and counters in the data loop, registers in the I/O data loop, and to memory control.

#### **Memory Control**

The memory control section of the processor performs tasks initiated by the central control, I/O control and options. These tasks consist of reading a 16-bit word from memory or writing a word or byte into memory.

Memory control acknowledges receipt of the signal to the requesting sections and signals when done with the task. When one request is accepted no others are acknowledged until the current one is completed, but central control can override its own prior request.

#### I/O Data Loop

The I/O data loop contains a multiplexor, I/O data register, and drivers and receivers. Three sources of data are applied to the I/O data loop: data from the I/O bus, data from the arithmetic and logic unit, and data from the memory I/O register (MIOR). The input data is selected by the I/O multiplexor under control of the I/O control signals and transferred on to the bidirectional I/O bus.

In addition to being applied to the I/O drivers, the output of the I/O data register is applied to the data loop and memory control sections.

#### I/O Control

The I/O control operates under control of an independent read-only memory (ROM). It performs I/O operations initiated either by the central control or I/O device activity. This permits I/O operations to proceed with minimal impact on internal processor functions. The I/O performs programmed I/O initiated by the central control. Both normal and high-speed direct memory access (DMA) are handled by the I/O control. I/O interrupts are processed by I/O control.

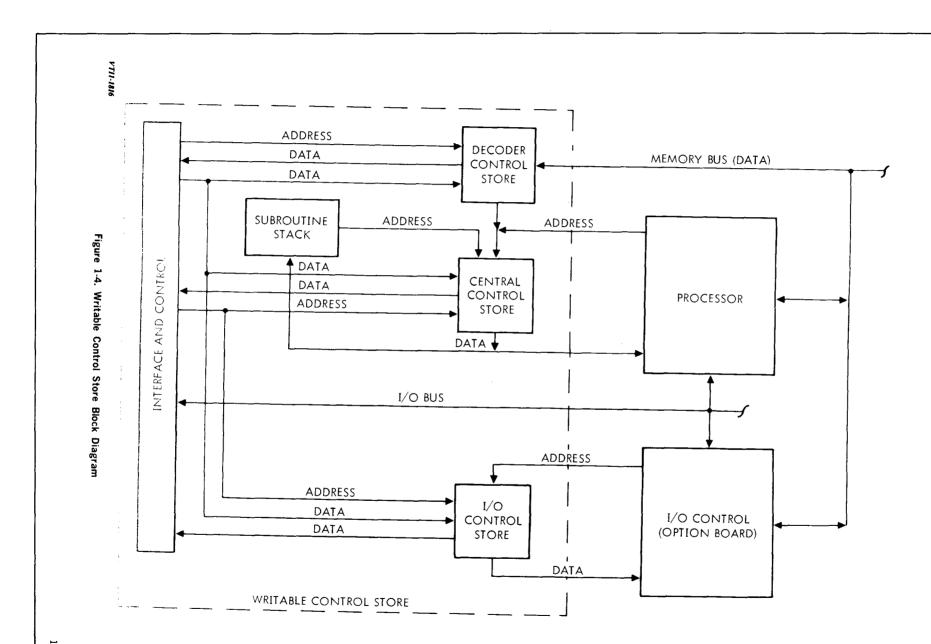

#### 1.4.2 Writable Control Store

The Writable Control Store (WCS) extends the processor's read-only control store to permit addition of new instructions, development of microprogrammed diagnostics, and optimal tailoring of the computer system to its applications.

Unlike the read-only control store which contains the Varian 70 series standard instruction set and cannot be altered, the WCS can be loaded from the computer's main

memory under control of I/O instructions. This capability of altering the contents of the WCS gives the user complete access to the resources of the computer system.

A test program for the WCS hardware is provided to assist in maintaining the system. Operating the test program is described in the maintenance manual for the WCS.

#### Configurations

The WCS is available in three configurations:

- One page (512 words) of control store and a subroutine stack (Model 7X-4001)

- 2. Half page of control store and a subroutine stack (Model 7X-4000)

- One page with a subroutine stack, a writable decoder control store and a writable I/O control store (Model 7X-4002)

Model 7X-4002 is shown in the block diagram of figure 1-4. The three control stores shown in this diagram are the writable counterparts for read-only components of the processor.

The decoder control store replaces the instruction buffer, decoder, and decoding logic in the processor to improve instruction set changes. It is formed from two 16-word by 16-bit memory arrays with the logic that decodes main memory instructions into an address for the central control store.

The central control store is a counterpart of the page zero of read-only storage. With each processor clock pulse, a 64-bit microinstruction is read from the central control store to specify the actions to occur. A typical microinstruction may define several operations such as selecting the next control store microinstruction to be executed, test conditions for branching, initiating memory operations and selecting ALU functions.

The I/O control store contains a 256-word memory array of 16-bit words.

A standard feature with all WCS models is the subroutine stack that increases storage efficiency by providing a call and return capability for subroutines of microinstructions. Up to 16 addresses for branches can be stored in the stack. Operations are provided for pushing, popping, and deleting an entry.

Up to three writable control store pages (2048 words including the page-zero read-only store) can be installed in a Varian 70 series computer system. Each writable control store page unit is contained on a printed-circuit board that plugs into a Varian 70 series mainframe.

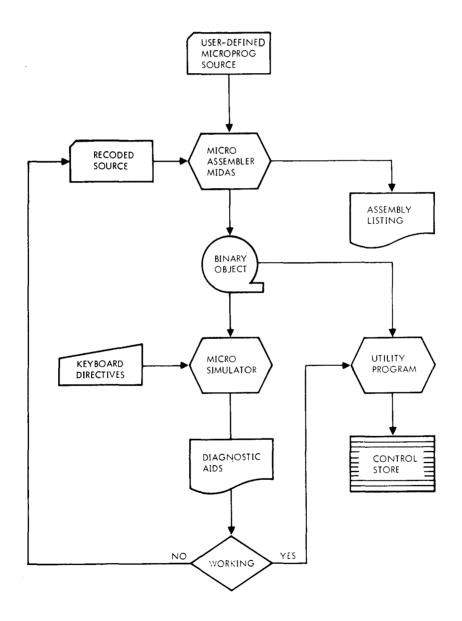

#### 1.4.3 Software Modules

Microprogram preparation uses a sequence of software provided with the WCS. First the program is written and assembled with a special assembler called MIDAS. Upon error-free assembly the code is run in a simulated environment which is completely independent of a WCS. The ability to trace and correct the execution is available with the microsimulator. These first two steps can occur without a WCS. Then only when the microprograms are checked completely the code can be loaded in the WCS

with the micro-utility program. In addition to loading the utility provides some diagnostics. These steps are depicted in figure 1-5.

All the components of the microprogramming software were designed to operate both under operating systems, MOS and VORTEX, and as stand-alone programs on the Varian 70 or 620 series computers. Operating systems require a minimum configuration (see the manual for the particular

VT11-1799

Figure 1-5. Steps for Realizing Microprograms

operating system). Table 1-1 lists the hardware requirements for microprogramming software.

#### Assembler

An assembler is a computer program which translates symbolic statements into machine instructions. The symbols are more meaningful than the strings of bit settings they represent. In addition to simply translating from symbolic to the executable code, the assembler assigns storage locations to the assembled instructions and produces a form of the instructions for loading into the processor's control store.

The microprogram data assembler (MIDAS) allows the user to prepare microprograms for the WCS. Through the use of operation mnemonics, symbolic addressing, address-field calculation, macro definitions, error detection and auto-

MIDAS is designed to provide the user with a tool for microprogram implementation. While relieving the user of much of the tedious housekeeping associated with generating microinstructions and their data fields, it also allows the user to describe the microinstructions at their most fundamental level.

#### Simulator

Verifying that the microprogram does indeed solve the problem is the next step. A logical step in implementing a microprogram is to run it with the microsimulator. The effects of executing a faulty microprogram are likely to be worse than those caused by poor assembly-language coding.

The simulator runs the output from the assembler within main-memory storage. At selected times conditions and the contents of data locations can be changed and examined. Projected changes can be simulated to evaluate eventual changes to the microprograms.

After determining that the code is error-free the WCS can be loaded with the utility program, which uses a command set as consistent as possible with the simulator.

#### Utility

Loading the WCS with the assembled and test microcode is performed by the microprogram utility, MIUTIL. In addition, on-line debugging directives are available through the utility.

Table 1-1. WCS Software Configuration Matrix

| Program             | Operating<br>System | 8 : | <b>M</b> em<br>12 16 |   |   |   | TTY<br>Keyboard/<br>Printer | TTY<br>PT<br>Reader | TTY<br>PT<br>Punch | High-<br>Speed<br>PT<br>Reader |

|---------------------|---------------------|-----|----------------------|---|---|---|-----------------------------|---------------------|--------------------|--------------------------------|

| Micro-<br>Assembler | VORTEX              |     | Х                    | R | 0 | 0 | x                           | N                   | N                  | 0                              |

| MIDAS               | MOS                 | ΧI  | R O                  | 0 | 0 | 0 | x                           | X                   | N                  | 0                              |

|                     | SA                  | Х   | R O                  | 0 | 0 | 0 | X                           | X                   | ×                  | 0                              |

| Micro-<br>Simulator | VORTEX              |     |                      | X | R | 0 | x                           | N                   | N                  | x                              |

| MICSIM              | MOS                 |     | Х                    | R | 0 | 0 | X                           | X                   | N                  | R                              |

|                     | SA                  |     | Х                    | R | 0 | 0 | X                           | X                   | N                  | R                              |

| Micro-<br>Utility   | VORTEX              |     | х                    | 0 | 0 | 0 | x                           | N                   | N                  | x                              |

| MIUTIL              | MOS                 | ΧF  | ₹ 0                  | 0 | 0 | 0 | X                           | X                   | N                  | R                              |

|                     | SA                  | X F | ₹ 0                  | 0 | 0 | 0 | x                           | X                   | N                  | R                              |

| WCS Test<br>Program |                     | Χľ  | 1 N                  | N | N | N | R                           | 0                   | N                  | x                              |

(continued)

Table 1-1. WCS Software Configuration Matrix (continued)

| Program             | Operating<br>System | High-<br>Speed<br>PT<br>Punch | Card<br>Reader | Card<br>Punch | Line<br>Printer | Mag<br>Tape | Rotating<br>Memory | WCS<br>Option |

|---------------------|---------------------|-------------------------------|----------------|---------------|-----------------|-------------|--------------------|---------------|

| Micro-              | VORTEX              | 0                             | R              | O             | R               | 0           | x                  |               |

| Assembler<br>MIDAS  | MOS                 | 0                             | R              | R             | R               | ×           | 0                  |               |

|                     | SA                  | 0                             | R              | 0             | R               | 0           | N                  |               |

| Micro-              | VORTEX              | N                             | R              | N             | R               | 0           | X                  |               |

| Simulator<br>MICSIM | MOS                 | N                             | R              | N             | R               | ×           | 0                  |               |

|                     | SA                  | N                             | R              | N             | R               | 0           | N                  |               |

| Micro               | VORTEX              | N                             | R              | N             | R               | 0           | X                  | X             |

| Utility<br>MIUTIL   | MOS                 | N                             | R              | N             | R               | ×           | 0                  | X             |

|                     | SA                  | N                             | R              | N             | R               | 0           | N                  | X             |

| WCS Test<br>Program |                     | N                             | N              | N             | N               | N           | N                  | x             |

### Legend:

X = minimum configuration

R = recommended (recommended in place of its minimum counter part)

O = optional (can be used but program will function completely without it)

N = not used with the program

## SECTION 2 CAPABILITIES

This section describes micro-operations available with Varian 70 series systems. The operations are grouped into the following categories:

- a. data transfer and transformation

- b. addressing and conditional actions

- c. memory access

- d. other controls

A basic example follows these sections. Some important timing considerations are presented at the conclusion of this section of capabilities.

This section describes only central control store programming.

I/O and decoder control stores are treated in section 8.

#### 2.1 GENERAL MICROINSTRUCTIONS

The 64 bits of the microinstruction are grouped into fields referenced by either an ordinal number or a two-letter name for the microprogram assembler. The full resources of the system can be exploited by the user who is familiar with all the defined microinstruction fields. To start most common operations, a limited set of fields is involved.

Because some of the bit combinations in the microword have no function, the user should be cautious and avoid coding those bit settings not defined. Undefined codes may be assigned new functions in the future.

ţ

THIS PAGE INTENTIONALLY LEFT BLANK

## 2.2 DATA TRANSFER AND TRANSFORMATION

#### 2.2.1 ALU Input Sources

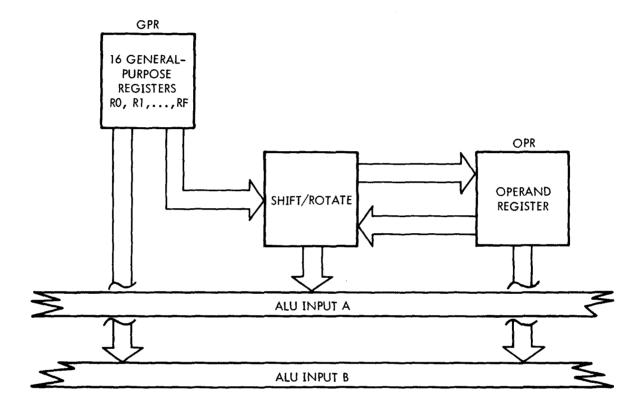

Input to the arithmetic and logic unit (ALU) is selected by a combination of fields. The ALU receives two inputs, A and B. Two buses can move information to the ALU but the same sources are not available for both buses. Some inputs to the ALU can be sent on either bus and some on both. The general purpose registers can be selected as input upon either bus and a specific register selected for each bus.

Any of the general-purpose registers can be shifted on its way on the A bus to the ALU. Shifting can be one bit position to the left or right.

Input to the ALU can be from one or two of the generalpurpose registers. The use of one of these registers is indicated by setting field LA to zero for input on the A bus, and LB for input on the B bus. The specific register is specified in AA and/or BB.

For example to use registers R2 and R4 as the input to the ALU

| field           | LB     | LA     | BB | AA |

|-----------------|--------|--------|----|----|

| value<br>(hex.) | 0      | 0      | 2  | 4  |

| Mnemonic        | B\$GPR | A\$GPR | R2 | R4 |

LA can also specify that the register indicated by AA is shifted or rotated. Shift left and shift right are indicated in the LA field and the shift field, SH.

#### Special Registers as ALU Input

By setting the LB field to one, SREG for special register the value in the BB field takes on a different meaning:

| 0 | OPR  | Operand register                 |

|---|------|----------------------------------|

| 1 | MIR  | Memory input register            |

| 2 | IOR  | I/O register                     |

| 3 | STAT | Processor status word            |

| 4 | ORSE | Operand right byte sign extended |

| 5 | OLSE | Operand left byte sign extended  |

| 6 | ORZF | Operand right byte zero fill     |

| 7 | OLZF | Operand right byte in the        |

|   |      | left byte position zero fill     |

Table 2-1. ALU Input A Bus Selections

ALU Input A Bus Source

Fields

| ALU Input A Bus Source                                            |    | Fields                    |    |

|-------------------------------------------------------------------|----|---------------------------|----|

|                                                                   | LA | SH                        | LB |

| Program counter                                                   | 01 | xxx                       | XX |

| General-purpose<br>register (any one<br>of 16) specified<br>in AA | 00 | Neither<br>X01 nor<br>X1X | οx |

| General-purpose<br>register (any one<br>of 16) specified in<br>AA | 00 | XXX                       | 1X |

| All zeros input                                                   | 00 | X01                       | 0X |

| All ones input                                                    | 00 | X1X                       | 0X |

| General register (in AA) shifted left                             | 10 | See<br>below              | οx |

| Bit 15 = register<br>bit 14                                       |    | oxx                       |    |

| Bit 15 = register<br>bit 15                                       | ı  | 1XX                       |    |

| Bit 00 = zero Bit 00 = register bit 15                            |    | X00<br>X01                |    |

| Bit 00 = operand register bit 15                                  |    | X10                       |    |

| General register (in AA) shifted right                            | 11 | See<br>below              | ох |

| Bit 15 = multiply<br>sign flag                                    | '  | 000                       | ,  |

| Bit 15 = register                                                 |    | 001                       |    |

| Bit 15 = register                                                 |    | 010                       |    |

| Bit 15 = operand register bit 00                                  |    | 011                       |    |

| Bit 15 = zero                                                     |    | 100                       |    |

|                                                                   |    |                           |    |

X indicates the bit in that position is of no consequence to this action.

VTI1-1802

Figure 2-2. General-Purpose Registers, Operand Register and ALU Input

#### Table 2-2. ALU Input B Bus Selections

ALU Input B Bus Source

Fields

|                                                                                                                                                                                               | LB | ВВ                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------|

| General-purpose<br>register (any one<br>of 16)                                                                                                                                                | 00 | Specifies<br>register |

| Operand register full word                                                                                                                                                                    | 01 | 0000                  |

| Operand register right byte with                                                                                                                                                              | 01 | 0100                  |

| sign extended Operand register left byte with                                                                                                                                                 | 01 | 0101                  |

| sign extended Operand register right byte with                                                                                                                                                | 01 | 0110                  |

| zeros in left byte Operand register right byte in left byte position; zeros in right                                                                                                          | 01 | 0111                  |

| Memory input register<br>(MIR)                                                                                                                                                                | 01 | 0001                  |

| I/O register (IOR)                                                                                                                                                                            | 01 | 0010                  |

| Processor status word<br>(STAT)                                                                                                                                                               | 01 | 0011                  |

| Instruction register masked by 16-bit literal constant consisting of fields MF, CF, WR, SC, VF, WF, XF, SH and BB. A one in the mask fields forces the corresponding ALU input bit to a zero. | 10 | Part of<br>mask       |

| 16-bit literal constant consisting of the ones complement of fields MF, CF, WR, SC, VF, WF, XF, SH and BB                                                                                     | 11 | Part of constant      |

NOTE: When the 16-bit literal or mask is used, the ALU mode is forced to the arithmetic mode if the FF field bit 1 is a zero and to the logical mode if the FF field bit 1 is a one. A carry of zero is forced. The ALU output may not be written into any general register in this case. The WR field, which would specify such an operation is disabled for use as part of the 16-bit literal or mask.

#### Processor Status Word

The processor status word may be applied to the ALU input B bus when the LB field equals 01 and the BB field equals 0011. Processor status bits are assigned as follows:

| Bit  | Function                     | Name |

|------|------------------------------|------|

| 00   | Not used (logic 1)           |      |

| 01   | Supervisor mode flag         | SUPR |

| 02   | ALU zero flag                | ALUZ |

| 03   | Shift counter bit 00         |      |

| 04   | Shift counter bit 01         |      |

| 05   | Shift counter bit 02         |      |

| 06   | Shift counter bit 03         |      |

| 07   | Shift counter bit 04         |      |

| 08   | Overflow flag                | OVFL |

| 09   | ALU all ones flag            | ALUO |

| 10   | ALU sign flag                | ALUS |

| . 11 | ALU carry flag               | ALUC |

| 12   | Processor key register bit 0 |      |

| 13   | Processor key register bit 1 |      |

| 14   | Processor key register bit 2 |      |

| 15   | Processor key register bit 3 |      |

#### 2.2.2 ALU Functions

Two sources for data, an action to be performed by the arithmetic and logic unit and a destination for the result are all specified in a single microinstruction.

The ALU function is determined by three fields in microinstruction. These fields, function, mode and carry, are grouped together to give meaningful names to some common operations, like ADD for addition. This entire group of fields can be set to execute combinations which do not have convenient names in the assembler.

One basic ALU action or an operator is chosen. There are three categories of operations. Arithmetic operations available at this level include addition, subtraction, increment etc. Logical operators which have convenient

single-word names are AND, OR, exclusive OR, NOT implication and equivalence. Also the ALU can perform more complicated logical functions explained later in this section.

Table 2-3 lists some of the more common arithmetic and logical operations and the corresponding fields.

Table 2-3. ALU Operations

| Assembler<br>Mnemonic | ALU<br>Action | FF   | MF | CF |

|-----------------------|---------------|------|----|----|

| ZERO                  | all zeros     | 0011 | 1  | 00 |

| ONES                  | FFFF          | 1100 | 1  | 00 |

| TRNA                  | Α             | 1111 | 1  | 00 |

| TRNB                  | В             | 1010 | 1  | 00 |

| INCA                  | A + 1         | 0000 | 0  | 11 |

| DECA                  | A — 1         | 1111 | 0  | 00 |

| ADD                   | A + B         | 1001 | 0  | 00 |

| SUB                   | A-B           | 0110 | 0  | 11 |

| SHFA                  | A + A         | 1100 | 0  | 00 |

| AND                   | $A \wedge B$  | 1011 | 1  | 00 |

| ØR                    | $A \lor B$    | 0001 | 0  | 00 |

| EOR                   | A ¥ B         | 0110 | 1  | 00 |

| NOTA                  | Ã             | 0000 | 1  | 00 |

| NOTB                  | ₿             | 0101 | 1  | 00 |

<sup>\*</sup>cannot be used when input B is mask or literal

#### ALU Mode

There are two modes available for the ALU, arithmetic and logical. In the arithmetic mode the user selects a type of carry input to the ALU to be used with the arithmetic action. In logical functions the value of the carry field (CF) is ignored. The mode is directly set as either arithmetic or logical by the MF field. Indirectly the mode can be set when the actual mode field is part of a literal or literal mask. If the LB field is 10 or 11 in binary, the MF and CF fields are part of a 16-bit constant. In this case the ALU mode is taken from the bit 1 setting of the FF field (consequently this limits the functions available with a literal or mask).

#### Carry Flag

The CF field specifies carry input to the ALU as follows:

| CF | Value of Carry In       |

|----|-------------------------|

| 00 | Zero                    |

| 01 | Stored carry            |

| 10 | Stored carry complement |

| 11 | One                     |

The carry flag ALUC, bit 11 of STAT, is altered only if SF is set to zero or two, TF to zero and the GF field to XX1X. Under these conditions carry is set or reset to the carry produced by the ALU. The only meaningful conditions for carry are the arithmetic functions such as add, increment, decrement and subtract. For these conditions the carry flag is set as follows. MF is zero for all of the following.

Table 2-4. Carry Flag Settings

| FF   | Function                             | If Carry In = 0                                                                                                                                                                                           | If Carry In = 1                                                                                                                                                                                    |

|------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000 | Α                                    | Reset                                                                                                                                                                                                     | Set if result = 0                                                                                                                                                                                  |

| 0001 | AVB                                  | Reset                                                                                                                                                                                                     | Set if result = 0                                                                                                                                                                                  |

| 0010 | ΑVĒ                                  | Reset                                                                                                                                                                                                     | Set if result = 0                                                                                                                                                                                  |

| 0011 | _1                                   | Reset                                                                                                                                                                                                     | Set unconditionally                                                                                                                                                                                |

| 0100 | A + (A Λ Ē)                          | x                                                                                                                                                                                                         | X                                                                                                                                                                                                  |

| 0101 | $(A \lor B) + (A \lor \overline{B})$ | x                                                                                                                                                                                                         | X                                                                                                                                                                                                  |

| 0110 | A-B-1                                | Set if $[(A_{15} = B_{15}) \land (A \ge B)] \lor$<br>$[(A_{15} \ne B_{15}) \land (A < O)]$                                                                                                                | Set if $[(A_{15} = B_{15}) \land (A > B)] \lor$<br>$[(A_{15} \neq B_{15}) \land (A < O)]$                                                                                                          |

| 0111 | (A ∧ Ē) −1                           | Set if result is ≠ -1                                                                                                                                                                                     | Set unconditionally                                                                                                                                                                                |

| 1000 | A + (A Λ B)                          | x                                                                                                                                                                                                         | X                                                                                                                                                                                                  |

| 1001 | A + B                                | Set if $[(A < O) \land (B < O)] \checkmark$<br>$[(A_{15} \neq B_{15}) \land$<br>$(A_{15} = O) \land$<br>$( A  \ge  B )] \lor$<br>$[(A_{15} \neq B_{15}) \land$<br>$(B_{15} = O) \land$<br>$ B  \ge  A )]$ | Set if $[(A < O) \land (B < O)] \lor$<br>$[(A_{15} \ne B_{15}) \land (A_{15} = O) \land$<br>$(A \ge B)] \lor$<br>$[(A_{15} \ne B_{15}) \land (B_{15} = O) \land$<br>$(B \ge A)] \lor [Result = O]$ |

| 1010 | (A ∨ B̄) + (A ∧ B)                   | X                                                                                                                                                                                                         | X                                                                                                                                                                                                  |

| 1011 | (A ∧ B) −1                           | Set if result ≠ -1                                                                                                                                                                                        | Set unconditionally                                                                                                                                                                                |

| 1100 | A + A                                | Set if $A_{15} = 1$                                                                                                                                                                                       | If A <sub>15</sub> = 1                                                                                                                                                                             |

| 1101 | (A ∨ B) + A                          | X                                                                                                                                                                                                         | X                                                                                                                                                                                                  |

| 1110 | (A V B) + A                          | X                                                                                                                                                                                                         | X                                                                                                                                                                                                  |

| 1111 | A — 1                                | Set if result ≠ -1                                                                                                                                                                                        | Set unconditionally                                                                                                                                                                                |

#### **Arithmetic Operations**

The FF field determines an arithmetic operation as indicated below when the MF field is 0. Carry input is set independently. When bit 1 of FF is zero the arithmetic mode is selected when the actual mode field is part of a mask or literal. The expressions in parentheses are evaluated first from left to right. Any further evaluation is performed from left to right.

#### **Logical Operations**

When MF is one, the logical operations occur as indicated below by FF field settings. The carry field is ignored. Symbol indicates exclusive OR operation.

## **Arithmetic Functions**

| FF Value | <b>ALU Action</b>                     | SYMBOLS                         |

|----------|---------------------------------------|---------------------------------|

| 0        | Α                                     | V Inclusive OR                  |

| 1        | AVB                                   | ★ Exclusive OR                  |

| 2        | ΑVΒ̈́                                 | + Addition                      |

| 3        | All ones                              | <ul> <li>Subtraction</li> </ul> |

| 4        | A + (Α Λ Ē)                           | logical AND                     |

| 5        | $(A \lor B) + (A \land \overline{B})$ | č complement                    |

| 6        | A —B —1                               |                                 |

| 7        | A ∧ Ã —1                              |                                 |

| 8        | $A + (A \wedge B)$                    |                                 |

| 9        | A + B                                 |                                 |

| Α        | $(A \lor \bar{B}) + (A \land B)$      |                                 |

| В        | (A ∧ B) −1                            |                                 |

| С        | A + A                                 |                                 |

| Ð        | $(A \lor B) + A$                      |                                 |

| E        | $(A \lor \bar{B}) + A$                |                                 |

| F        | A —1                                  |                                 |

| FF Value | ALU Action              |

|----------|-------------------------|

| 0        | Α                       |

| 1        | A V B                   |

| 2        | ĀΛB                     |

| 3        | All zeros               |

| 4        | $\overline{A \wedge B}$ |

| 5        | Ē                       |

| 6        | A xo√ B                 |

| 7        | ΑΛĒ                     |

| 8        | Ā∨B                     |

| 9        | A XX B                  |

| Α        | В                       |

| В        | ΑΛĒ                     |

| С        | All ones                |

| D        | A∨Ē                     |

| E        | , <b>A∨B</b>            |

| _        |                         |

## 2.2.3 ALU Output Destinations

The ALU output will be determined by the function performed. This data can be directed by the microinstruction to the general-purpose registers, some of the special registers, counters, and indirectly to memory and I/O.

A multiple destination can be one of the general-purpose registers and a special register.

The direct assignments of the ALU result is specified by a combination of fields, WR, LB, AA and RF. The first three are used to specify any one of the 16 general-purpose registers while RF selects sending data to the program counter, operand register, shift counter or key register.

Table 2-5. ALU Output Data Destination

#### Destination

#### Control Fields

|                                                                                                                                       |            |    | roi rieius |      |    |

|---------------------------------------------------------------------------------------------------------------------------------------|------------|----|------------|------|----|

|                                                                                                                                       | RF         | WR | SF         | IM   | LB |

| DIRECT CONTROL                                                                                                                        |            |    | ·          |      |    |

| General register (any 1 of<br>16) (Specified in AA)                                                                                   |            | 1  |            |      | ox |

| Program counter                                                                                                                       | 001        | ,  |            |      |    |

| Operand register                                                                                                                      | 011 or     |    |            |      |    |

| Shift counter                                                                                                                         | 111<br>010 |    |            |      |    |

| Processor key register                                                                                                                | 110        |    |            |      |    |

| INDIRECT MEMORY CONTROL                                                                                                               |            |    |            |      |    |

| NOTE: Transfer occurs only if cycle is successfully initiated)                                                                        |            | ·  |            |      |    |

| Memory data bus                                                                                                                       |            |    | Not 00     | XX1X |    |

| Memory address register                                                                                                               |            |    | Not 00     | 01XX |    |

| Memory input register and instruction buffer                                                                                          | <br>       |    | 00         | 0100 |    |

| INDIRECT I/O CONTROL                                                                                                                  |            |    | 1          |      |    |

| I/O register                                                                                                                          |            |    | 00         | 111X | (  |

| NOTE: Transfer is under direct control of I/O control. Operation is specified by TS, AB, MR fields and contents of I/O control store. |            |    |            |      |    |

#### 2.2.4 Other Registers

#### Shift Counter

The shift counter is an 8-bit counter which may be incremented and tested independent of the ALU. It is thus useful in keeping track of iteration in a microprogram. The counter may be tested for overflow using test addressing. The overflow condition occurs when the shift counter is minus one.

An instruction which both increments and tests the shift counter will be testing the old value. If the counter is loaded with negative number and incremented to 0, the one instruction delay is no problem. This is because checking the old value for -1 produces the same result as checking the new value for zero.

#### **Program Counter**

The program counter is a 16-bit register which can be incremented and/or used as a memory address, independent of the ALU. The following are considerations when incrementing the program counter:

- a. if the same microinstruction uses the P register for a memory address, the new value of P will be used.

- b. if the microinstruction both increments P and uses P as an ALU input, unpredicatable results are obtained. In general, using P as an ALU input and incrementing P should not be done in the same instruction.

#### Processor Key Register (KEY)

A 4-bit processor key register supplies signals for memory operations initiated by the processor. These four bits in conjunction with the high-order bits of the normal memory address are used by the memory map option determine physical addresses. It should be noted that this key register is different from the map register used under VORTEX II. The latter is loaded over I/O and cannot be conveniently accessed from the micro level.

#### 1/O Key Register

A similar key register for I/O is a 4-bit register which supplies signals to the memory map option during memory operations initiated by the I/O control.

#### **Operand Register**

The operand register is a 16-bit register which has special shifting abilities. As previously noted, the ALU input A bus may have any of the 16 general-purpose applied shifted left or right one-bit position. In addition, the operand register may be shifted left or right independently or in conjunction with shifting of any general register. This can occur any time the 16-bit literal or mask is not in use.

When the LB field is equal to 0X (no literal/mask) the SC, WF and XF fields define operand register shifting.

When the SC field equals 0 no shifting takes place. When the SC field equals 1, the operand register is shifted left if the WF field equals 0 and right if the WF field equals 1.

For left shifts the next contents of the operand register bit 00 is specified by the XF field. If XF equals 00 operand register bit 15 is copied to bit 00 to permit independent circular shifting. If XF equals 01 bit 15 of the general register specified by the AA field is copied to bit 00.

This permits double-length circular shifting. If XF = 10 the complement of the ALU output bit 15 is copied to bit 00. If XF = 11 the operand register bit 00 is set to zero.

For right shifts the next contents of the operand register bit 15 is specified by the XF field. If XF equals 00 operand register bit 00 is copied to bit 15 to permit independent circular shifting. If XF equals 01 bit 00 of the general

Table 2-6. Operand Register Shift Operations

#### Control Field

| LB | sc | WF   | ΧF                  |

|----|----|------|---------------------|

|    | 0  |      |                     |

| 1X |    |      |                     |

| 0x | 1  |      |                     |

|    |    | 0    |                     |

|    |    |      | 00                  |

|    |    |      | 01                  |

|    |    |      | 10                  |

|    |    |      | 11                  |

|    |    | 1    |                     |

|    |    |      | 00                  |

|    |    |      | 01                  |

|    |    |      | 10                  |

|    |    |      | 11                  |

|    | 1X | 1X 0 | 0   1X   OX   1   O |

register specified by the AA field is copied to bit 15 to permit double-length circular shifting. If XF equals 10 the operand register bit 15 is maintained at its current state to permit independent arithmetic shifting. If XF equals 11 the shift flag (SHFT) is copied to bit 15.

#### 2.3 ADDRESSING

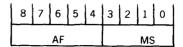

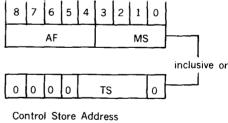

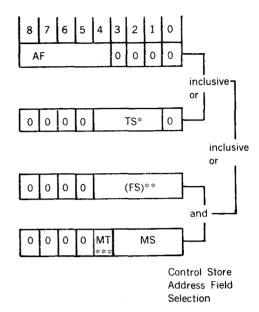

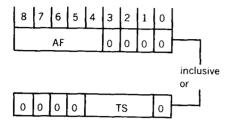

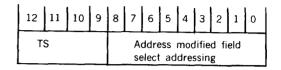

#### 2.3.1 General