# **VARIAN 75 SYSTEM SUPPLEMENT**

The statements in this publication are not intended to create any warranty, express or implied. Equipment specifications and performance characteristics stated herein may be changed at any time without notice. Address comments regarding this document to Varian Data Machines, Publications Department, 2722 Michelson Drive, P.O. Box E, Irvine, California, 92664.

98 A 9906 220

SEPTEMBER 1975

# TABLE OF CONTENTS

**SECTION 1 - INTRODUCTION**

|             | SECTION 2 · REGISTER USAGE          |      |

|-------------|-------------------------------------|------|

|             | SECTION 3 - DATA FORMATS            |      |

| 3.1         | Double-Precision Nonarithmetic Data | 31   |

| 3.2         | Double-Precision Arithmetic Data    | 31   |

| 3.3         | Byte Data                           | 3.   |

|             | SECTION 4 - ADDRESSING              |      |

|             | SECTION 5 INSTRUCTIONS              |      |

| 5.1         | Instruction Formats                 | 51   |

| 5.2         | Instruction Specifications          |      |

| 5.2.1       | Register-to-Memory Instructions     | 54   |

| 5.2.2       | Byte Instructions                   | 56   |

| 5.2.3       | Jump-If Instructions                | 5 /  |

| 5.2.4       | Double-Precision Instructions       | 5 10 |

| 5.2.5       | Immediate Instructions              | 5 13 |

| 5.2.6       | Register-to-Register Instructions   | 5 14 |

| 5.2.7       | Single Register Instructions        | 5 16 |

| <b>5</b> .3 | Instruction Execution Times         | 517  |

|             | SECTION 6 DAS ASSEMBLER             |      |

| 6.1         | Register to Memory Instructions     | 61   |

| 6.2         | Byte Instructions                   | 62   |

| 6.3         | Jump-If Instructions                | 6 2  |

| 6.4         | Double-Precision Instructions       | 6 2  |

| 6.5         | Immediate Instructions              | 6 2  |

| 6.6         | Register-to-Register Instructions   | 63   |

| 6.7         | Single Register Instructions        | 6.3  |

# **INDEX OF INSTRUCTIONS**

# CONTENTS

# LIST OF ILLUSTRATIONS

| Figure |                                         |     |

|--------|-----------------------------------------|-----|

| 1-1    | Varian 75 Computer System               | 12  |

| 1-2    | Equipment Cabinet Layout                | 1 3 |

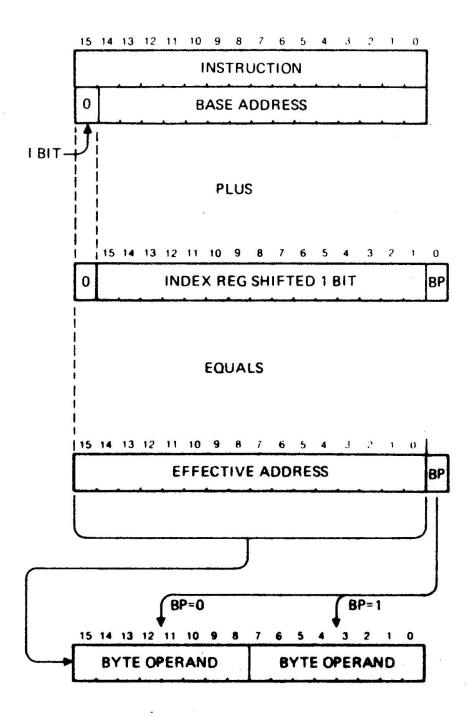

| 4-1    | Byte Addressing, Indexed Mode           | 4 2 |

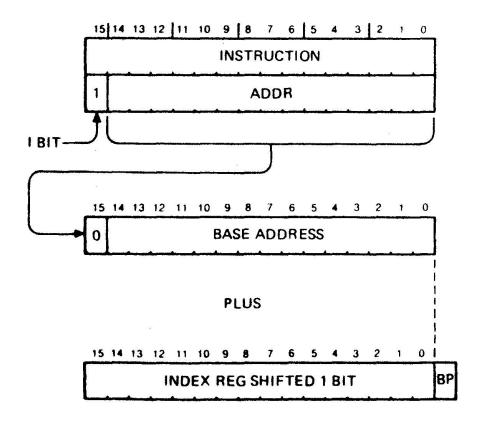

| 4-2    | Byte Addressing, Indexed Indirect Mode  | 4 3 |

|        | LIST OF TABLES                          |     |

| Table  |                                         |     |

| 1-1    | Specifications                          | 1 4 |

| 2-1    | Programming Registers                   |     |

| 2-2    | Binary Codes for V75 Register Selection | 22  |

| 4-1    | Addressing Modes                        | 4 1 |

| 5-1    | Execution Times for V75 Instructions    | 517 |

### SECTION 1 INTRODUCTION

This supplement, when used in conjunction with the Varian 74 System Handbook (document number 98A 9906 210), describes the Varian 75 Computer System.

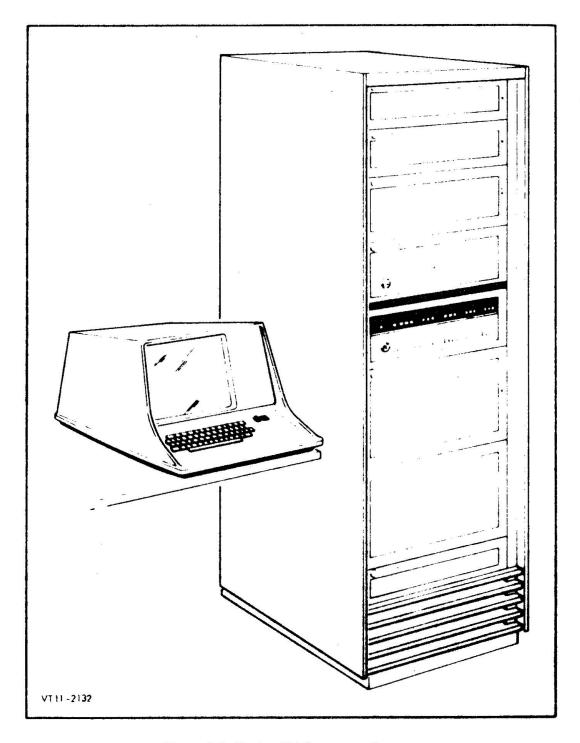

The Varian 75 (figure 1-1) is a general-purpose, microprogrammed computer system for scientific, industrial, and data-communication applications. While maintaining full compatibility with all V70 series software and peripherals, the V75 features a significantly expanded instruction set. In addition to the assembly language instructions available with other V70 series computers, the V75 has 27 instructions that permit a programmer to have access to 8 general-purpose registers and to operate on 8-bit, 16-bit, and 32-bit operands.

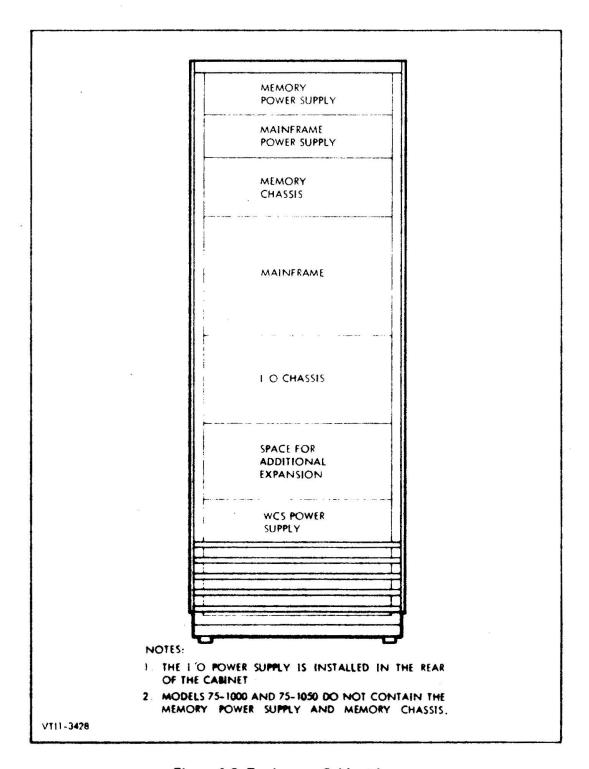

All V75 systems contain a 65,536-word memory with dual-port or single-port access and expansion capability to 262,144 words. Figure 1-2 shows the layout of components in the equipment cabinet.

Specifications for the V75 system are listed in table 1-1.

Figure 1-1. Varian 75 Computer System

Figure 1-2. Equipment Cabinet Layout

# Table 1-1. Specifications

|                                                                                     | The state of the s |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type                                                                                | General-purpose microprogrammed digital computer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Memory                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Semiconductor                                                                       | Dual-port, 330-nanosecond cycle time, 16-bit word, and optional byte parity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Core                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Word length                                                                         | Single-port with 800-nanosecond cycle time (990 nanseconds without interleaving).  8, 16, or 32 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Registers                                                                           | 24 registers. 8 16-bit registers are addressable by the V75 instructions (7 of these registers can be used as index registers and 4 can be used as 2 double-word registers). 16 16-bit registers can be used for microprogramming (8 of these are special purpose).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Arithmetic                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I/O Transfer Rates<br>(Maximum rates are given<br>for non-interleaved<br>operation) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Semiconductor<br>Memory                                                             | DMA: 969,000 words per second.  DMA (620 compatible): 372,900 words per second.  PMA: 1,102,000 words per second (writing).  1,010,000 words per second (reading).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Core Memory                                                                         | DMA: 897,800 words per second.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (450/660 ns)                                                                        | DMA (620 compatible): 361,800 words per second.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ,                                                                                   | PMA: 1,010,000 words per second (writing).<br>932,000 words per second (reading).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Core Memory                                                                         | DMA: 835,876 words per second.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (800/990 ns)                                                                        | DMA (620 compatible): 352,112 words per second. PMA: 713,000 words per second (writing).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Special High-Speed I/O                                                              | 673,000 words per second (reading).  A direct memory interface (DMI) that provides transfers up to 2,970,000 words per second on one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Instructions                                                                        | or more buses for non-standard devices.  187 standard, can be extended with writable control store. Floating point processor option provides an additional 14 instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### Table 1-1. Specifications (continued)

Addressing Modes ...... Byte addressing, word addressing, and double-word addressing, preindexed direct or indirect to 32,768 words using any of the 7 index registers. Direct to 2,048 words. Relative to P, X or B register to 512 words. Preindexing with X or B register. Multilevel indirect to 32,768 words. Indirect indexed. Immediate. Post indexing with X or B register. Extended mode to 32,768 words. Memory-map addressing to 262,144 words. Standard features ..... Power failure/restart Real time clock Multiply/divide I/O bus with DMA Automatic bootstrap loaders (paper tape, rotating memory, and Teletype) Keyboard-CRT terminal Memory map Writable control store Core memory interleaving Priority memory access Programmers control panel 65,536 words of main memory Equipment cabinet Power for approximately 10 peripheral controllers I/O chassis with 19 I/O slots Options ...... Byte parity Block transfer controller Priority interrupt module Buffer interlace controller Floating point processor Additional writable control stores, up to a maximum of 3. Logic levels ...... Internal (positive logic): High = +2.4 to 5.0V dc Low = 0 to +0.5V dc I/O bus (negative logic): High = +2.8 to +3.6V dc

Low = 0 to +0.5V dc

Table 1-1. Specifications (continued)

| Software      | Language processors                              |

|---------------|--------------------------------------------------|

| 3-57 (Wale    | Macro assembler                                  |

|               | FORTRAN IV                                       |

|               |                                                  |

|               | RPG II                                           |

|               | RPG IV                                           |

|               | BASIC                                            |

|               | COBOL                                            |

|               | Operating systems                                |

|               | BEST real time                                   |

|               | MOS batch                                        |

|               | VORTEX and VORTEX II multi-tasking               |

|               | Data base management                             |

|               | TOTAL                                            |

|               | Interactive                                      |

|               | Time-sharing subsystem                           |

|               | (TSS)                                            |

|               | Microprogramming support                         |

|               | Assembler                                        |

|               | Simulator                                        |

|               | Utility for loading and debugging                |

|               | Data communications                              |

|               | VTAM                                             |

|               | Application software                             |

|               | HASP/RJE                                         |

|               | Message switching                                |

|               | All of the above software operated with          |

|               | VORTEX II.                                       |

| Dimensions    | Equipment cabinet is (outside dimensions) 77     |

|               | inches high, 26 inches wide, and 36 inches deep  |

|               | (195.6 by 66 by 91.4 cm). The table top key-     |

|               | board-CRT terminal is approximately 15 inches    |

|               | high, 17 inches wide, and 27 inches deep (38.1   |

| 4             | by 43.2 by 68.6 cm).                             |

| Input voltage | 105 to 125V ac or 210 to 250V ac, at 50 or       |

|               | 60 Hz.                                           |

| Input current | With 115V ac, the maximum ac current require-    |

|               | ments for individual system components in the    |

|               | equipment cabinet are: 12 amperes ac for main-   |

|               | frame power supply, 12 amperes ac for memory     |

|               | power supply, 6 amperes ac for I/O power supply, |

|               | 4 amperes ac for WCS power supply, and 3 am-     |

# INTRODUCTION

# Table 1-1. Specifications (continued)

| tule is 0 to 40 degrees C (32 to 104 degrees F). | Operationalenvironment | peres ac for cabinet fans. The keyboard-CRT terminal requires 1.5 amperes ac.  0 to 50 degrees C (32 to 122 degrees F), 0 to 90 percent relative humidity without condensation. For keyboard-CRT terminal, operating temperature is 0 to 40 degrees C (32 to 104 degrees F). |

|--------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

### **SECTION 2 REGISTER USAGE**

The Varian 75 computer system contains eight registers which are available to the programmer. Table 2-1 lists the nomenclature and functional descriptions of the V75 programming registers along with corresponding registers of the other V70 series computers.

Table 2-1. Assembly-Programming Registers

| V75<br>Nomenclature | V75<br>Function                                                                                 | V70 Series<br>Nomenclature | V70 Series<br>Function              |

|---------------------|-------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------|

| R0                  | Byte or word accumulator,<br>or most-significant half of<br>double-precision register<br>R0 -R1 | А                          | Accumulator                         |

| R1                  | Word accumulator, index register, or least-significant half of double-precision register R0-R1  | В                          | Accumulator<br>or index<br>register |

| R2                  | General-purpose register                                                                        | X                          | Index register                      |

| R3                  | General-purpose register                                                                        |                            |                                     |

| R4                  | General-purpose register<br>or most-significant half<br>of double precision<br>register R4-R5   |                            |                                     |

| R5                  | General-purpose register or least-significant half of double precision register R4-R5           |                            |                                     |

| R6                  | General-purpose register                                                                        |                            |                                     |

| R7                  | General-purpose register                                                                        |                            |                                     |

In the V75 system, contents of the eight programming registers can be displayed or altered by using the appropriate controls and indicators on the control panel. The binary codes for selecting the eight registers (using the REG SELECT switches) are listed in table 2-2. Refer to section 11 of the V74 System Handbook for V75 control-panel operation since the controls and indicators for the V74 and V75 computers are the same.

### REGISTER USAGE

Table 2-2. Binary Codes for V75 Register Selection

| REG S | ELEC | T Swi | tches | Selected Register |

|-------|------|-------|-------|-------------------|

| 8     | 4    | 2     | 1     | _                 |

|       |      |       |       |                   |

| 0     | 0    | 0     | 0     | R0                |

| 0     | 0    | 0     | 1     | Ħ1                |

| 0     | 0    | 1     | 0     | R2                |

| 0     | 0    | 1     | 1     | R3                |

| 0     | 1    | 0     | 0     | R4                |

| 0     | 1    | 0     | 1     | R5                |

| 0     | 1    | 1     | 0     | R6                |

| 0     | 1    | 1     | 1     | R7                |

| 1     | 0    | 0     | 0,    |                   |

| 1     | 0    | 0     | 1.    |                   |

| 1     | 0    | 1     | 0,    |                   |

| 1     | 0    | 1     | 1 *   |                   |

| 1     | 1    | 0     | 0,    |                   |

| 1     | 1    | 0     | 1 *   |                   |

| 1     | 1    | 1     | 0,    |                   |

| 1     | 1    | 1     | 1 1   |                   |

<sup>\*</sup>These codes select registers that are used for WCS microprogramming. With two exceptions the contents of these registers can be displayed and altered using the control panel; however, alteration from the control panel should be done only for maintenance purposes or special applications. The register selected with the binary code of 1000 alway contains the contents of the instruction register. The registers selected with binary codes of 1011 and 1100 always contain all zeros and all ones, respectively; the contents of these two registers can not be altered from the control panel.

### **SECTION 3 DATA FORMATS**

The V75 instructions operate on three additional data formats: double-precision nonarithmetic data, double-precision arithmetic data, and byte data.

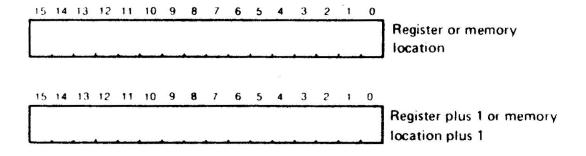

#### 3.1 DOUBLE-PRECISION NONARITHMETIC DATA

The format for double-precision nonarithmetic data consists of a 32-bit unsigned operand stored in consecutive memory locations or registers as illustrated below:

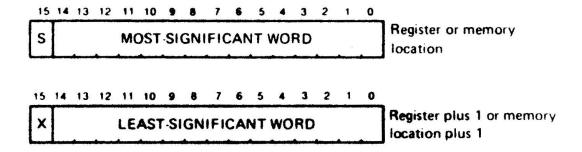

#### 3.2 DOUBLE-PRECISION ARITHMETIC DATA

The format for double-precision arithmetic data consists of a 32-bit twos complement integer stored in consecutive memory locations or registers as illustrated below:

Note: Bit 15 of the least-significant word is not used.

### DATA . JRMATS

# 3.3 BYTE DATA

The byte data format consists of 8-bit nonarithmetic characters stored as two bytes of a memory word in consecutive memory locations or as a single byte in the right half of register R0 (A) as illustrated below:

| 15 | 14 | 13 | 12 | 11 | 10 |         | 7     | 6. | 5        | 4 | 3  | 2 | 1 | 0 |                                         |

|----|----|----|----|----|----|---------|-------|----|----------|---|----|---|---|---|-----------------------------------------|

| L  | ٠  |    | 81 | TE |    | <b></b> |       | ٠  | ·Opposed | B | TE | • | ٠ |   | Memory location                         |

| 15 | 14 | 19 | 19 | 11 | 10 | •       | 7     |    | •        | 4 | 3  | • | • | • |                                         |

|    |    |    |    |    | 0  |         | <br>ŕ |    | s        |   | TE |   |   |   | Register RO                             |

| L  |    |    |    |    |    | _       | <br>L |    |          |   | _  |   | _ |   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

### **SECTION 4 ADDRESSING**

In addition to the addressing modes for other V70 series computers, the V75 includes byte addressing. Byte addressing is used in conjunction with the two V75 byte instructions.

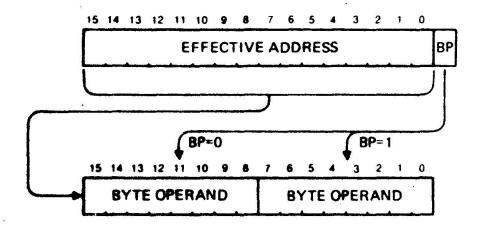

As shown in figures 4-1 and 4-2, byte addressing consists of an indexed mode and an indexed indirect mode. The base address word is summed with the contents of the index register (shifted arithmetically one bit to the right) to form the effective word address of the byte operand. The least-significant bit (bit 0) of the index register, referred to as the byte pointer (BP), determines the position of the byte operand. When the byte pointer is zero, the left byte (bits 8 through 15) is specified; when it is one, the right byte (bits 0 through 7) is specified. Indexed or indexed indirect addressing is specified by bit 15 (1 bit) of the address. When the I bit is zero, indexed addressing is specified; when it is one, indexed indirect addressing is specified. If indexed indirect addressing is specified, postindexing is used. One level of indirect addressing is the maximum for byte instructions. For the other V75 instructions (non-byte instructions), up to four addressing modes are possible. These four modes are direct, indexed, indirect, and preindexed indirect.

All four addressing modes are used with the 2-word register-to-memory and double-precision instructions. The first word of both the register-to-memory and double-precision instructions contains the instruction field and the index register field (RX). The second word contains the indirect bit (I bit) and the address (ADDR). Each of the four addressing modes and the corresponding RX field and I-bit values for these instructions are listed in table 4-1.

Only direct or indirect addressing is used with the V75 jump-if instructions. The remaining V75 instructions have no addressing modes.

| Table 4-1.          | . Addressing Modes |            |

|---------------------|--------------------|------------|

| Mode                | RX Field           | l Bit      |

| Direct              | 0                  | 0          |

| Indexed             | 1 thru 7           | 0          |

| Indirect            | 0                  | 1          |

| Preindexed indirect | 1 thru 7:          | . <b>1</b> |

Figure 4-1. Byte Addressing, Indexed Mode

Figure 4-2. Byte Addressing, Indexed Indirect Mode

# **SECTION 5 INSTRUCTIONS**

This section contains an explanation of new instruction formats and detailed specifications and execution times for each of the V75 instructions.

#### 5.1 INSTRUCTION FORMATS

Each of the V75 instructions follow one of the seven instruction formats listed below. The first five are double-word formats and the last two are single-word formats.

- a. Register to Memory

- b. Byte

- c. Jump If

- d. Double Precision

- e. Immediate

- f. Register to Register

- g. Single Register

For register-to-memory instructions, the format is:

| 15 14 | 13 | 12       | 11       | 10  | •   |    | 7  | 6 | 5           | 4       | 3            | 2 | 1  | 0           |

|-------|----|----------|----------|-----|-----|----|----|---|-------------|---------|--------------|---|----|-------------|

|       | 0  | PEF      | RAT      | 101 | V C | OD | E  |   |             | R       |              |   | RX |             |

| 1     | -A | <u> </u> | <b>*</b> | •   |     | Al | OD | R | <del></del> | <b></b> | <del>1</del> |   |    | <del></del> |

RX field (bits 0 through 2) specifies the index register.

R field (bits 3 through 5) specifies the source or destination register.

ADDR (second word) specifies the base address (see Section 4 for addressing modes).

I (second word) specified direct or indirect addressing (when I is one, indirect addressing is specified).

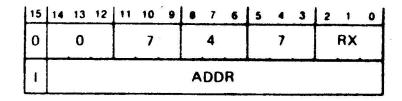

For byte instructions, the format is:

| 15 14 | 13 | 12        | 111 | 10      | • | 1.  | 7  | • | 5 | 4 | 3           | 2       | 1  | 0 |

|-------|----|-----------|-----|---------|---|-----|----|---|---|---|-------------|---------|----|---|

|       | 01 | PER       | AT  | ION     | C | ODI | Ε  |   |   |   |             |         | RX |   |

| 1     | _  | <b>^-</b> | •   | <b></b> |   | AD  | DR | - | • | - | <del></del> | <u></u> | •  |   |

#### INSTRUCTIONS

RX field (bits 0 through 2) specifies the index register.

ADDR (second word) specifies the base address (see Section 4 for addressing modes).

! (second word) specifies indexed or indexed indirect addressing (when I is one, indexed indirect addressing is specified).

For jump-if instructions, the format is:

| 15 14 | 13         | 12  | 11   | 10                                      | 9       | 8  | 7   | 6   | 5        | 4        | 3 | 2 | 1 | 0 |

|-------|------------|-----|------|-----------------------------------------|---------|----|-----|-----|----------|----------|---|---|---|---|

|       | OP         | ERA | ATIO | NC                                      | со      | DE |     |     |          | С        |   |   | R |   |

| 1     | _ <b>4</b> |     |      | *************************************** | <u></u> |    | ADI | DR. | <b>A</b> | <b>^</b> |   |   |   | • |

R field (bits 0 through 2) specifies the register to be tested.

C field (bits 3 through 5) specifies the test condition.

ADDR (second word) specifies the jump address (see Section 4 for addressing modes).

I (second word) specifies direct or indirect addressing (when I is one, indirect addressing is specified).

For double-precision instructions, the format is:

| 15 | 14 | 13  | 12       | 11       | 10          | 9       |    | 7  | 6  | 5 | 4 | 3 | 2       | 1  | 0           |

|----|----|-----|----------|----------|-------------|---------|----|----|----|---|---|---|---------|----|-------------|

|    | 1  | OPE | RA       | ATI      | ON          | СО      | DE |    |    |   |   |   |         | RX |             |

| -  |    | •   | <u> </u> | <u> </u> | <del></del> | <b></b> |    | AD | DR |   |   | - | <b></b> |    | <del></del> |

RX field (bits 0 through 2) specifies the index register.

ADDR (second word) specifies the base address (see Section 4 for addressing modes).

I (second word) specifies direct or indirect addressing (when I is one, indirect addressing is specified).

For immediate instructions, the format is:

| 15 14 | 13 | 12 11   | 10          | 9   | 8    | 7   | 6       | 5 | 4 | 3 | 2                                             | 1 | 0 |

|-------|----|---------|-------------|-----|------|-----|---------|---|---|---|-----------------------------------------------|---|---|

|       |    | OPE     | RA          | TIC | ON ( | COE | ÞΕ      |   |   |   |                                               | R |   |

|       |    | <b></b> | ^ · · · · · | •—  | IN   | 1M  | <b></b> | • | • | • | <u>l                                     </u> | A |   |

R field (bits 0 through 2) specifies the destination register. IMM (second word) specifies the 16-bit immediate operand.

For register-to-register instructions, the format is:

| 15 | 14 | 13  | 12  | 11 | 10 | •  | 6  | 7 | 6 | 5 | 4  | 3 | 2 | 1  | 0 |

|----|----|-----|-----|----|----|----|----|---|---|---|----|---|---|----|---|

|    | (  | OPE | ERA | TI | NC | co | DE |   |   |   | RS | i |   | RD | ) |

|    |    |     |     |    |    |    |    |   |   | ı |    |   | ļ |    |   |

RD field (bits 0 through 2) specifies the source register.

RS field (bits 3 through 5) specifies the destination register.

For single register instructions, the format is:

| 15 | 14 | 13 | 12 | 11 | 10 | 9   |     | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|-----|-----|----|---|---|---|---|---|---|---|

|    |    |    | 0  | PE | RA | ΓΙΟ | N C | OD | E |   |   |   |   | R |   |

|    |    |    |    |    |    |     |     |    |   |   |   |   | 1 |   |   |

R field (bits 0 through 2) specifies the operand register.

### **5.2 INSTRUCTION SPECIFICATIONS**

The instruction specifications for the V75 instructions are grouped according to the seven instruction formats listed in paragraph 5.1. The specification for each instruction includes: mnemonic, name, word diagram, format, type of addressing, and description.

INSTRU CIONS

## 5.2.1 Register-To-Memory Instructions

LD Load

| 15 | 14 | 13    | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2 | 1  | 0 |

|----|----|-------|----|----|----|---|---|----|---|---|---|---|---|----|---|

| 0  |    | 0     |    |    | 7  |   |   | 0  |   |   | R |   |   | RX |   |

| 1  |    | 5317- |    |    |    |   | A | DD | R |   |   |   |   |    |   |

Format:

Register-to-Memory

Addressing:

Direct, Indexed, Indirect, Preindexed Indirect

Description:

The contents of the effective memory address replace the con-

tents of the register specified by the R field.

es.

LD, R OFFSET, RX

ST Store

| Ŀ | 5 | 14 | 13  | 12      | 11      | 10       | 9 |     | 7  | •     | 5 | 4 | 1 | 2 | 1  | 0 |

|---|---|----|-----|---------|---------|----------|---|-----|----|-------|---|---|---|---|----|---|

| 1 | 0 |    | 0   |         |         | 7        |   |     | 1  | _     |   | R |   |   | RX |   |

|   | ı |    | iù. | <b></b> | <b></b> | <u> </u> |   | ADI | OR | 8 8 8 |   |   |   |   | 12 |   |

Format:

Register to Memory

Addressing:

Direct, Indexed, Indirect, Preindexed Indirect

Description:

The contents of the register specified by the R field replace

the contents of the effective memory address.

AD

Add

| 15 | 14 '13 | 12 | 11 | 10      | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2 | 1  | 0 |

|----|--------|----|----|---------|---|---|----|---|---|---|---|---|----|---|

| 0  | -0     |    |    | 7       |   |   | 2  |   |   | R |   |   | RX |   |

| _  | ····   |    |    | <b></b> |   | A | DD | R |   |   | • |   |    |   |

Format:

Register to Memory

Addressing:

Direct, Indexed, Indirect, Preindexed Indirect

Description:

Contents of the register specified by the R field are added to the effective memory address. The twos complement of the sum replaces the contents of the register specified by the R field. If both operands have the same sign and the result has

the opposite sign, the overflow flag is set.

58

Subtract

| 15 | 14 13 12 | 11 10 9     | 8 7 6 | 5 4 3 | 2 1 0 |

|----|----------|-------------|-------|-------|-------|

| 0  | 0        | 7           | 3     | R     | RX    |

| 1  |          | <del></del> | ADDR  |       |       |

Format:

Register to Memory

Addressing:

Direct, Indexed, Indirect, Preindexed Indirect

Description:

Contents of the effective memory address are subtracted from the contents of the register specified by the R field. The twos complement of the difference replaces the contents of the register specified by the R field. If the operands have opposite signs and the sign of the result equals the sign of the contents of the effective memory address, the overflow flag is set.

# 5.2.2 Byte Instructions

**LBT**

Load Byte

| 15 | 14 | 13 | 12 | 11 | 10 | 9         | 8 | 7  | 6 | 5        | 4        | 3 | 2 | 1        | 0 |

|----|----|----|----|----|----|-----------|---|----|---|----------|----------|---|---|----------|---|

| 0  |    | 0  |    |    | 7  |           |   | 4  |   |          | 6        |   |   | RX       |   |

| ı  | •  |    |    |    | •  | <b></b> - | A | DD | R | <b>L</b> | <b>^</b> | • | L | <b>.</b> | • |

Format:

Byte

Addressing:

Byte

Description:

The contents of the effective byte address replaces the contents of the right byte of register R0. The contents of the left

byte of register R0 are replaced with zeros.

SBT

Store Byte

Format:

Byte

Addressing:

Byte

Description:

The contents of the right byte of register RO replace the con-

tents of the effective byte address.

# 5.2.3 Jump-If Instructions

JZ

Jump If Register Zero

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2 | 1. | 0 |

|----|----|----|----|----|----|---|---|----|---|---|---|---|---|----|---|

| 0  |    | 0  |    |    | 6  |   |   | 7  |   |   | 2 |   |   | R  |   |

| ١  |    |    |    |    |    |   | А | DD | R |   |   |   |   |    |   |

Format:

Jump If

Addressing:

Direct, Indirect

Description:

If the register specified by the R field contains zero, the instruction at the effective jump address (ADDR) is executed. If the register (R) does not contain zero, the next instruction in sequence is executed. Contents of the register (R) are unaltered.

JNZ

Jump If Register Not Zero

| 15 | 14 | 13 | 12   | 111 | 10       | 9 | 8  | 7  | 6 | 5       | 4            | 3       | 2 | 1        | 0 |

|----|----|----|------|-----|----------|---|----|----|---|---------|--------------|---------|---|----------|---|

| 0  |    | 0  | 2077 |     | 6        |   |    | 7  |   |         | 3            |         |   | R        |   |

| 1  |    | •  | •    | •   | <b>.</b> | • | Al | DD | R | <b></b> | <del>4</del> | <b></b> | 4 | <b>-</b> | • |

Format:

Jump If

Addressing:

Direct, Indirect

Description:

If the register specified by the R field contains a value that is not zero, the instruction at the effective jump address (ADDR) is executed. If the register (R) contains zero, the next instruction in sequence is executed. Contents of the register (R) are unaltered.

JN

Jump If Register Negative

| 15 | 14 | 13      | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5        | 4       | 3 | 2 | 1 | 0 |

|----|----|---------|----|----|----|---|---|----|---|----------|---------|---|---|---|---|

| 0  |    | 0       |    |    | 6  |   |   | 7  |   |          | 4       |   |   | R |   |

| 1  |    | <b></b> | •  |    | •  |   | A | DC | R | <b>4</b> | <b></b> | • |   | • | • |

Format:

Jump If

Addressing:

Direct, Indirect

Description:

If the register specified by the R field contains a negative value, the instruction at the effective jump address (ADDR) is executed. If the register (R) contains a positive value (including zero), the next instruction in sequence is executed.

Contents of the register (R) are unaltered.

JP

## Jump If Register Positive

| 15 | 14 13 12 | 11 10 9  | 8 7 6 | 5 4 3 | 2 1 0 |

|----|----------|----------|-------|-------|-------|

| 0  | 0        | 6        | 7     | 5     | R     |

| ı  |          | <u> </u> | ADDR  |       |       |

Format:

Jump If

Addressing:

Direct, Indirect

Description:

If the register specified by the R field contains a positive value (including zero), the instruction at the effective jump address (ADDR) is executed. If the register (R) contains a negative value, the next instruction in sequence is executed. Contents

of the register (R) are unaftered.

JDZ

Jump If Double-Precision Register Zero

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6           | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|----|-------------|---|---|---|---|---|---|

| 0  |    | 0  | •  |    | 6  |   |   | 7  | • 2275 1144 |   | 6 | • |   | R |   |

| 1  |    |    |    |    |    |   | Α | DD | R           |   |   |   |   |   |   |

Format:

Jump If

Addressing:

Direct, Indirect

Description:

If the double-precision register specified by the R field contains zero, the instruction at the effective jump address (ADDR) is executed. If the value of the R field is 0, double-precision register R0-R1 is specified; if the value is 4, double-precision register R4-R5 is specified. If the double-precision register (R) does not contain zero, the next instruction in sequence is executed. Contents of the double-precision register (R) are unaltered.

JONZ

Jump If Double-Precision Register Not Zero

| 15 | 14 | 13 | 12   | 11 | 10 | 9 | 8 | 7  | 6 | 5       | 4 | 3 | 2 | 1 | 0 |

|----|----|----|------|----|----|---|---|----|---|---------|---|---|---|---|---|

| 0  |    | 0  |      |    | 6  |   |   | 7  |   |         | 7 |   |   | R |   |

| -  |    | •  | ···· |    |    |   | A | DD | R | <b></b> | • | • |   | • |   |

Format:

Jump If

Addressing:

Direct, Indirect

Description:

If the double-precision register specified by the R field contains a value that is not zero, the instruction at the effective jump address (ADDR) is executed. If the value of the R field is 0, double-precision register R0-R1 is specified; if the value is 4, double-precision register R4-R5 is specified. If the double-precision register (R) contains zero, the next instruction in sequence is executed. Contents of the double-precision register (R) are unaltered.

## 5.2.4 Double-Precision Instructions

DLD

**Double Load**

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6  | 5 | 4 | 3 | 2       | 1  | 0 |

|----|----|----|----|----|----|---|---|----|----|---|---|---|---------|----|---|

| 0  |    | 0  |    |    | 4  |   |   | DR | !  |   | 0 |   |         | RX |   |

| ı  |    |    | -  |    |    |   | Δ | DE | )R |   | · | • | <b></b> | •  | • |

Format:

**Double Precision**

Addressing:

Direct, Indexed, Indirect, Preindexed Indirect

Description:

Contents of the double-precision effective address replace the contents of the double-precision register specified by the DR field. If the value of the DR field is 6, double-precision register R0-R1 is specified; if the value is 7, double-precision register

R4-R5 is specified.

DST

**Double Store**

| 15 | 14 | 13 | 12       | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4       | 3        | 2       | ,  | 0            |

|----|----|----|----------|----|----|---|---|----|---|---|---------|----------|---------|----|--------------|

| 0  |    | 0  | 4        |    |    |   |   | DR |   |   | 1       |          | 1       | RX |              |

| 1  |    |    | <u> </u> |    |    | • | A | DD | R | 4 | <b></b> | <u> </u> | <b></b> |    | <del>^</del> |

Format:

**Double Precision**

Addressing:

Direct, Indexed, Indirect, Preindexed Indirect

Description:

Contents of the double-precision register specified by the DR field replace the contents of the double-precision effective address. If the value of the DR field is 6, double-precision register R0-R1 is specified; if the value is 7, double-precision

register R4-R5 is specified.

DADD

Double Add

| 15 | 14 | 13 | 12                                    | 11 | 10 | 9        | 8 | 7  | 6 | 5  | 4         | 3 | 2 | 1  | 0        |

|----|----|----|---------------------------------------|----|----|----------|---|----|---|----|-----------|---|---|----|----------|

| 0  |    | 0  | 4                                     |    |    |          |   | DR |   |    | 2         |   | e | RX |          |

| I  |    |    | · · · · · · · · · · · · · · · · · · · |    | •  | <b>-</b> | A | DD | R | 27 | ********* | • |   |    | <u> </u> |

Format:

**Double Precision**

Addressing:

Direct, Indexed, Indirect, Preindexed Indirect

Description:

Contents of the double-precision register specified by the DR field are added to the double-precision effective memory address. The twos complement of the sum replaces the contents of the double-precision register specified by the DR field. If the value of the DR field is 6, double-precision register R0-R1 is specified; if the value is 7, double-precision register R4-R5 is specified. If both double-precision operands have the same sign and the result has the opposite sign, the overflow flag is set.

**DSUB**

Double Subtract

| 15 | 14 | 13 | 12       | 111     | 10   | 9 |   | 7   | 6 | 5 | 4 | 3 | 2 | 1         | 0 |

|----|----|----|----------|---------|------|---|---|-----|---|---|---|---|---|-----------|---|

| 0  |    | 0  |          |         | 4    |   |   | DR  |   |   | 3 |   |   | RX        |   |

| 1  |    |    | <b>*</b> | <b></b> | •••• |   | p | NDD | R |   | • |   | 4 | <b>^-</b> |   |

Format:

**Double Precision**

Addressing:

Direct, Indexed, Indirect, Preindexed Indirect

Description:

Contents of the double-precision effective memory address are subtracted from the contents of the double-precision register specified by the DR field. The twos complement of the difference replaces the contents of the double-precision register specified by the DR field. If the value of the DR field is 6, double-precision register R0-R1 is specified; if the value is 7, double-precision register R4-R5 is specified. If the double-precision operands have opposite signs and the sign of the result does not equal the sign of the original contents of the specified double-precision register, the overflow flag is set.

DAN Double And

| 15 | 14 | 13 | 12          | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4        | 3 | 2 | 1  | 0 |

|----|----|----|-------------|----|----|---|---|----|---|---|----------|---|---|----|---|

| 0  |    | 0  |             |    | 4  |   |   | DR |   |   | 4        |   |   | RX |   |

| 1  |    |    | <del></del> |    |    |   | Δ | DE | R |   | <u> </u> |   |   | •  | • |

Format:

**Double Precision**

Addressing:

Direct, Indexed, Indirect, Preindexed Indirect

Description:

A bit by bit logical AND function is formed between corresponding bits of the double-precision register specified by the DR field and the double-precision effective address. The logical results replace the contents of the specified double-precision register. If the value of the DR field is 6, double-precision register R0-R1 is specified; if the value is 7, double-precision

register R4-R5 is specified.

DOR

Double Or

| 15 | 14 | 13 | 12       | 11 | 10 | •        |   | 7  | 6 | 5 | 4        | 3 | 2 | 1       | 0 |

|----|----|----|----------|----|----|----------|---|----|---|---|----------|---|---|---------|---|

| 0  |    | 0  |          | 4  |    |          |   | DR |   |   | 5        |   | 1 | RX      |   |

| 1  |    | •  | <b>*</b> |    |    | <b>`</b> | A | DD | R |   | <b>^</b> | • | • | <b></b> |   |

Format:

**Double Precision**

Addressing:

Direct, Indexed, Indirect, Preindexed Indirect

Description:

A bit by bit logical OR function is formed between corresponding bits of the double-precision register specified by the DR field and the double-precision effective address. The logical results replace the contents of the specified double-precision register. If the value of the DR field is 6, double-precision register RO-R1 is specified; if the value is 7, double-precision

register R4-R5 is specified.

DER

#### **Double Exclusive Or**

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2        | 1  | 0 |

|----|----|----|----|----|----|---|---|----|---|---|---|---|----------|----|---|

| 0  |    | 0  |    |    | 4  |   |   | DR |   |   | 6 |   |          | RX |   |

| ī  |    |    |    |    |    | · | A | DD | R |   | • |   | <u> </u> |    |   |

Format:

**Double Precision**

Addressing:

Direct, Indexed, Indirect, Preindexed Indirect

Description:

A bit by bit logical EXCLUSIVE-OR function is formed between corresponding bits of the double-precision register specified by the DR field and the double-precision effective address. The logical results replace the contents of the specified double-precision register. If the value of the DR field is 6, double-precision register R0-R1 is specified; if the value is 7, double-

precision register R4-R5 is specified.

### 5.2.5 Immediate Instructions

LDI

Load Immediate

| U | 1 |     | 7     | ,       |

|---|---|-----|-------|---------|

|   | 0 | 0 7 | 0 7 4 | 0 7 4 4 |

Format:

Immediate

Addressing:

None

Description:

The immediate operand (IMM) replaces the contents of the

register specified by the R field.

ADI Add Immediate

| 0 |          | 0        |  | 7 |   | 4  |   | 5 |   |   | R |  |

|---|----------|----------|--|---|---|----|---|---|---|---|---|--|

|   | <u> </u> | <u> </u> |  | · | L | MN | Λ |   | · | L |   |  |

Format:

**Immediate**

Addressing:

None

Description:

Contents of the register specified by the R field are added to the immediate operand (IMM). The twos complement of the sum replaces the contents of the register specified by the R field. If the operands have the same sign and the result has an opposite sign, the overflow flag is set.

### 5.2.6 Register-To-Register Instructions

T Transfer

| 15 | 14 1 | 3 12 | 11 | 10 | 9 |   | 7 | 6 | 5        | 4  | 3 | 2 | 1  | 0 |

|----|------|------|----|----|---|---|---|---|----------|----|---|---|----|---|

| 0  | (    | )    |    | 7  |   | × | 7 |   |          | RS |   |   | RD |   |

|    |      |      | L_ |    |   | L |   |   | <u> </u> |    |   | L |    |   |

Format:

Register to Register

Addressing:

None

Description:

The contents of the source register specified by the RS field

replace the contents of the destination register specified by the

RD field.

**ADR**

Add Register

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4  | 3 | 2 | 1  | 0 |

|----|----|----|----|----|----|---|---|---|---|---|----|---|---|----|---|

| 0  |    | 0  |    |    | 7  |   |   | 5 |   |   | RS |   |   | RD |   |

Format:

Register to Register

Addressing:

None

Description:

Contents of the source register specified by the RS field are added to the contents of the destination register specified by the RD field. The twos complement of the sum replaces the contents of the specified destination register. If both operands have the same sign and the result has the opposite sign, the overflow flag is set.

SBR

Subtract Register

| L | 15 | 14 | 13 | 12  | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4  | 3 | 2 | 1  | 0 |

|---|----|----|----|-----|----|----|---|---|---|---|---|----|---|---|----|---|

|   | 0  | 60 | 0  | 2 3 |    | 7  |   |   | 6 |   |   | RS |   |   | RD |   |