## **BUFFER INTERLACE CONTROLLER**

an option for the

Varian Data Machines

Computer Systems

Specifications are subject to change without notice. Address comments regarding this manual to Varian Data Machines, Publications Department, 2722 Michelson Drive, Irvine, California, 92664.

## TABLE OF CONTENTS

## SECTION 1 GENERAL DESCRIPTION

## SECTION 2 INSTALLATION

| 2.1   | PHYSICAL DESCRIPTIONINTERCONNECTION.  |     |

|-------|---------------------------------------|-----|

| 2.3   | INTERFACE DATA                        |     |

|       |                                       |     |

|       | SECTION 3 OPERATION                   |     |

| 3.1   | I/O INSTRUCTIONS                      | 3-1 |

| 3.2   | PROGRAMMING CONSIDERATIONS            |     |

| 3.3   | SAMPLE PROGRAM                        |     |

|       |                                       |     |

|       | SECTION 4                             |     |

|       | THEORY OF OPERATION                   |     |

| 4.1   | ADDRESS REGISTERS                     |     |

| 4.2   | SEQUENCE CONTROL                      |     |

| 4.3   | OPERATING SEQUENCE                    |     |

| 4.3.1 | · · · · · · · · · · · · · · · · · · · |     |

| 4.3.2 |                                       | 4-1 |

| 4.3.3 |                                       | 4.1 |

| 4.3.4 |                                       | 4.4 |

| 4.3.5 | 5 Transfer Termination                | 4-4 |

|       | SECTION 5 MAINTENANCE                 |     |

| 5.1   | TEST EQUIPMENT                        | 5-1 |

| 5.1   | CIRCUIT-COMPONENT IDENTIFICATION      | 5.1 |

| 5.3   | CIRCUIT-BOARD REPAIR                  |     |

## SECTION 6 MNEMONICS

## LIST OF ILLUSTRATIONS

| Figure 2-1. BIC Board (Component Side)                | . 2-1      |

|-------------------------------------------------------|------------|

| Figure 2-2. BIC/Peripheral Controller Interface       | . 2-2      |

| Figure 2-3. Interface for Peripheral Devices with and |            |

| without BIC                                           | . 2-3      |

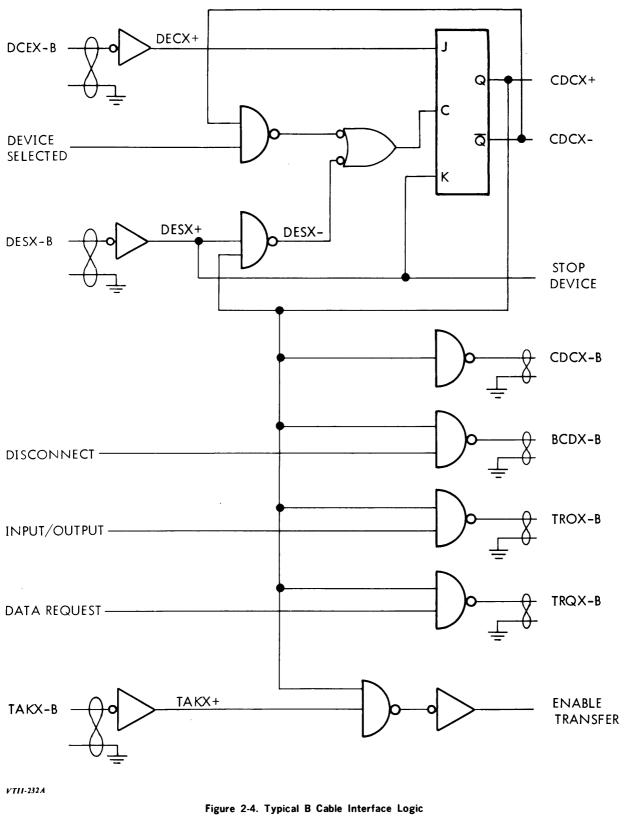

| Figure 2-4. Typical B Cable Interface Logic           | . 2-4      |

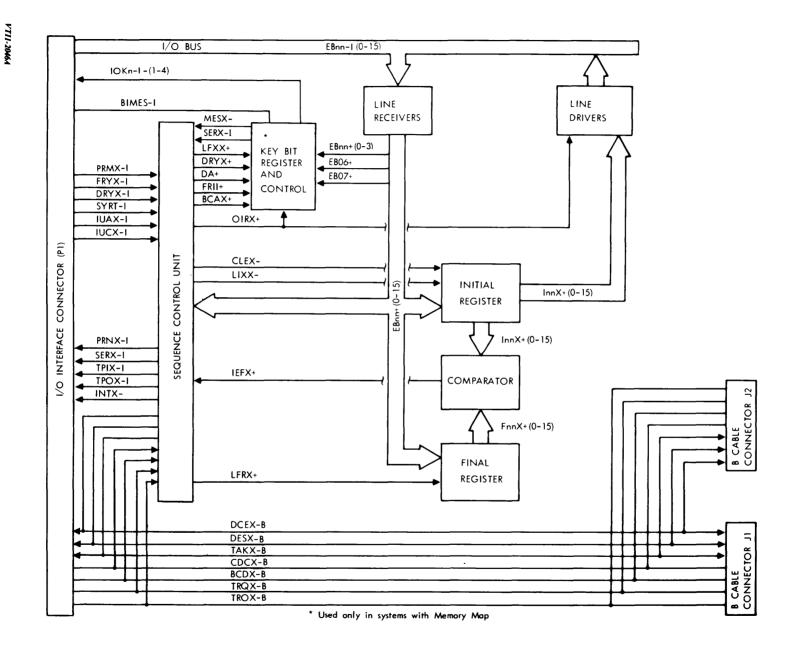

| Figure 4-1. BIC Block Diagram                         |            |

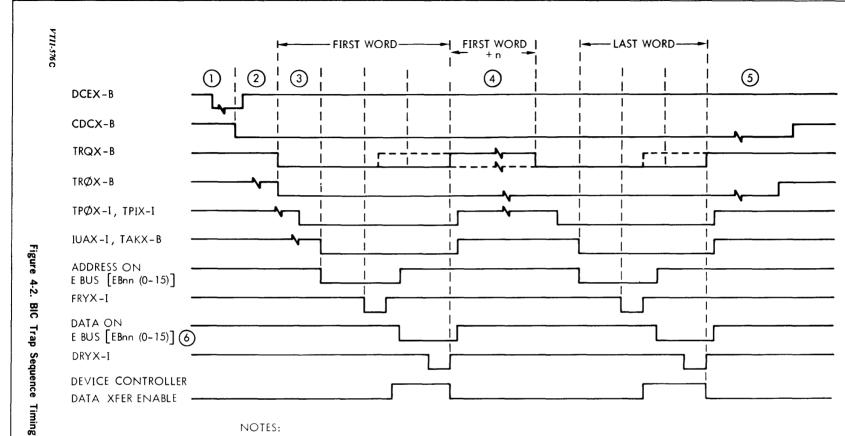

| Figure 4-2. BIC Trap Sequence Timing                  |            |

| LIST OF TABLES                                        |            |

| Table 1-1. BIC Specifications                         | . 1-1      |

| Table 2-1. BIC Inputs and Outputs                     | . 2-1      |

| Table 3-1. I/O Instructions                           | 3-1        |

| Table 3-2. Typical Service Routine                    | . 3-1      |

| Table 6.1. Manageria                                  | <i>c</i> 1 |

## **SECTION 1**

## **GENERAL DESCRIPTION**

The Buffer Interlace Controller (BIC) is a special-purpose hardware option for use with Varian computer systems. This manual is divided into six sections:

- · Features and specifications

- Installation and interconnection

- Operation

- Theory of operation

- Maintenance

- Mnemonics list

Volume 2 of this manual is assembled when the hardware is shipped and contains engineering documents such as logic diagrams, parts list, and installation drawings.

There are two versions of the BIC available. One version (without key bits) is for systems that do not have the memory map option and the other version (with key bits) is for systems that do have the memory map option.

The function of the BIC is to free the processor to perform other program functions during block word transfers between memory and peripheral controllers. Cycle-stealing trap requests inhibit the processing of a stored program for only the memory cycle required to transfer one word of data between memory and a peripheral controller. Operation register contents are not changed by the transfer, thus freeing the processor to execute an instruction from the stored program between successive data word transfers.

The BIC will perform DMA transfers at the peripheral device rate up to a maximum rate defined as follows:

$$R_{max} = \frac{I}{\frac{I}{R_{CPU max}} + T_{IUCX}}$$

where: R max is the maximum rate through a BIC (words/second)

R CPU is the maximum DMA rate for the processor (words/second)

T<sub>IUCX</sub> is the period of interrupt clock (seconds)

As an example, the maximum DMA rate for a Varian 70 series computer with core memory and a 990 nanosecond

interrupt clock period is 361,800 words/second. The maximum rate through the BIC is then:

$$R_{\text{max}} = \frac{1}{\frac{1}{361,800}} = 266,383 \text{ words/}$$

$$= 266,383 \text{ words/}$$

second

The BIC monitors trap requests initiated by the peripheral controllers.

Up to ten peripheral controllers can be connected to one BIC. Using standard I/O device addressing, a computer system can include up to four BICs.

The BIC is considered to be an I/O controller. Priorities for optional controllers having trap or interrupt capabilities are established by the order of their placement in the priority chain. The BIC is a system priority device; however the peripheral devices connected to it have no priority of their

Table 1-1 lists the BIC specifications.

Table 1-1. BIC Specifications

| Parameter                        | Description                                                                                                                     |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Organization                     | Contains input receivers and output drivers, two 16-bit address registers, a 4-bit key register, and a sequence control circuit |

| Control capability               | Up to ten peripheral controllers                                                                                                |

| I/O transfer rate                | Synchronized to peripheral device rate                                                                                          |

| I/O signal limits<br>(rise/fall) | Minimum 10 nanoseconds; maximum 100 nanoseconds                                                                                 |

| Logic levels<br>(internal)       | High = $+2.4$ to $+5.0$ V dc<br>Low = 0 to $+0.4$ V dc                                                                          |

| Logic levels (I/O bus)           | High = $+2.8 \text{ to } +3.6 \text{V dc}$<br>Low = 0 to $+0.5 \text{V dc}$                                                     |

| Size                             | Contained on one 7-3/4-by 12-inch (19.7 x 30.3 cm) printed-circuit board (continued)                                            |

### **GENERAL DESCRIPTION**

Table 1-1. BIC Specifications (continued)

| P | 20 | 21 | m | _ | ٠ | ۵ | , |

|---|----|----|---|---|---|---|---|

#### Description

Interconnection

Interfaces with I/O cable through backplane connector; connects to peripheral controllers through the backplane connector or through a

cable

Connectors

One 122-terminal card-edge connector (mates with female connector at back-plane) and two 44-terminal card-edge connectors (each mates with a 44-terminal connector on B cable for special configurations)

Power

+5V dc at 0.6A

Operating environment

0 to 50 degrees C; 10 to 90 percent relative humidity without condensation

# SECTION 2 INSTALLATION

The BIC has been packed and inspected to ensure its arrival in good working order. To prevent damage, take care during unpacking and handling. Check the shipping list to ensure that all equipment has been received. Immediately after unpacking, inspect the equipment for shipping damage. If damage exists:

- · Notify the transportation company

- · Notify Varian Data Machines

- · Save all packing material

## 2.1 PHYSICAL DESCRIPTION

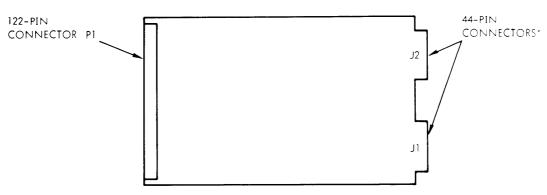

The BIC circuits are contained on a single printed-circuit (PC) board (p/n 44P0689). As illustrated in figure 2-1, the board contains three connectors P1, J1, and J2. Connectors J1 and J2 are wired in parallel and contain the peripheral control lines. Connector P1 also contains the same peripheral control lines as well as all I/O bus control signals for the BIC. Connectors J1 and J2 are used for special configurations

## 2.2 INTERCONNECTION

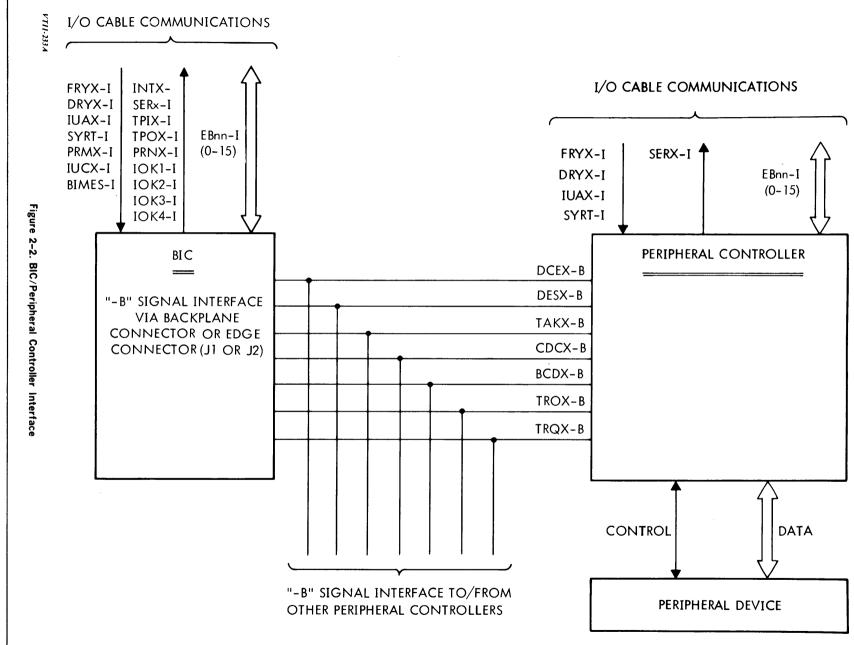

When two or more BIC controllers are installed in the same chassis, the B cable signals are connected only to the controller or controllers with which each BIC communicates. There are no B cable signals between BICs. If the BIC and the peripheral controllers are installed in different chassis, the interconnection is made through the J1 and J2 connectors. Figure 2-2 illustrates BIC/peripheral interconnections.

## 2.3 INTERFACE DATA

All BIC input/output signals utilize receiver driver stages to buffer internal circuits and external lines. The BIC interfaces with the computer via the "-I" signal lines and with peripheral controllers via the "-B" signal lines listed in table 2-1. The corresponding pin number of circuit card edge connector P1 follows each signal mnemonic (see logic diagram 91C0459). Refer to section 6 for definitions of the mnemonics.

Table 2-1. BIC Inputs and Outputs

|         | INPU | TS     |    |        | OUTPU   | τs     |     |

|---------|------|--------|----|--------|---------|--------|-----|

| BCDX-B  | 52   | EB10-I | 16 | DCEX-B | 56      | EB12-I | 18  |

| BIMES-I | 93   | EB11-I | 17 | DESX-B | 60      | EB13-I | 19  |

| CDCX-B  | 54   | EB12-I | 18 | EB00-I | 2       | EB14-I | 20  |

| DRYX-I  | 29   | EB13-I | 19 | EB01-I | 4.68.69 | EB15-I | 21  |

| EB00-I  | 2    | EB14-I | 20 | EB02-I | 6.71.72 | INTX-  | 75  |

| EB01-I  | 4,65 | EB15-I | 21 | EB03-1 | 8       | IOK1-I | 109 |

| EB02-I  | 6,70 | FRYX-I | 27 | EB04-I | 10      | IOK2-I | 110 |

| EB03-I  | 8    | 1UAX-I | 44 | EB05-I | 11      | IOK3-I | 112 |

| EB04-I  | 10   | IUCX-I | 45 | EB06-I | 12      | IOK4-I | 113 |

| EB05-I  | 11   | PRMX-I | 37 | EB07-I | 13      | PRNX-I | 42  |

| EB06-I  | 12   | SYRT-I | 43 | EB08-I | 14      | SERX-I | 31  |

| EB07-I  | 13   | TROX-B | 50 | EB09-I | 15      | TAKX-B | 58  |

| EB08-I  | 14   | TRQX-B | 49 | EB10-I | 16      | TPIX-I | 33  |

| EB09-I  | 15   |        |    | EB11-I | 17      | TPOX-I | 35  |

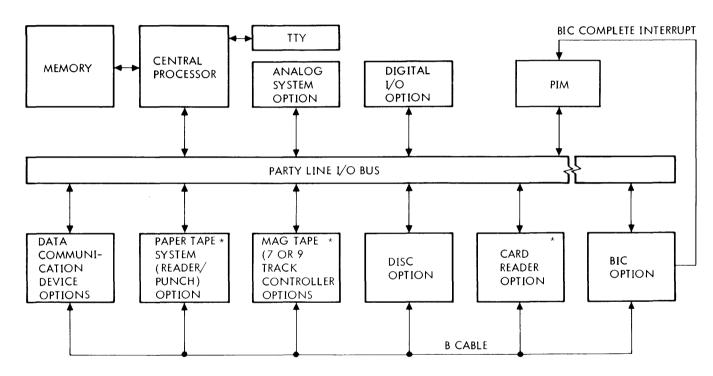

Many peripheral controllers, under software control. can transfer data either by programmed I. O or via BIC control. Controllers for peripherals such as discs and drums usually are not able to transfer data via programmed I. O due to their high transfer rates. Figure 2–3 shows a computer system with peripheral controllers that operate with and without BIC. Figure 2–4 is typical interface logic.

\* CONNECTORS J1 AND J2 ARE PARALLEL WIRED

VTI1-1792

Figure 2-1. BIC Board (Component Side)

INSTALLATION

\* CAPABLE OF BLOCK DATA TRANSFER VIA PROGRAMMED I/O CONTROL OR BIC CONTROL.

## SECTION 3 OPERATION

The BIC has no operating controls or indicators. It operates under program control.

#### 3.1 I/O INSTRUCTIONS

The BIC responds to the instructions listed in table 3-1. Two device addresses are assigned to each BIC to differentiate functions directed by the I/O instruction. Addresses 020 through 027 are reserved for BICs. Address/instruction codes in table 3-1 are for the first BIC in a system. If additional BICs are installed, the addresses shown should be incremented by two for each additional BIC (i.e., second BIC addresses should be 022 and 023).

Table 3-1. I/O Instructions

| Mnemonics                      | Octal<br>Code              | Description                                                                                          |

|--------------------------------|----------------------------|------------------------------------------------------------------------------------------------------|

|                                | Exte                       | ernal Control                                                                                        |

| EXC 020<br>EXC 021<br>EXC 0321 | 100020<br>100021<br>100321 | Activate BIC<br>Initialize<br>Enable loading of key bits                                             |

|                                |                            | Transfer                                                                                             |

| OAR 020<br>OBR 020<br>OME 020  | 103120<br>103220<br>103020 | Load initial register from A<br>Load initial register from B<br>Load initial register from<br>memory |

| OAR 021<br>OBR 021<br>OME 021  | 103121<br>103221<br>103021 | Load final register from A Load final register from B Load final register from memory                |

| INA 020<br>INB 020<br>IME 020  | 102120<br>102220<br>102020 | Read initial register into A Read initial register into B Read initial register into memory          |

| Mnemonics | Octal<br>Code | Description                          |

|-----------|---------------|--------------------------------------|

| CIA 020   | 102520        | Read initial register into cleared A |

| CIB 020   | 102620        | Read initial register into cleared B |

|           |               | Sense                                |

| SEN 020   | 101020        | Sense BIC not busy                   |

| SEN 021   | 101021        | Sense abnormal device stop           |

| SEN 0121  | 101121        | Senses if BIC has been stopped       |

|           |               | due to a memory-map error            |

### 3.2 PROGRAMMING CONSIDERATIONS

The user writes the programs that use the BIC. When preparing a program for use with the BIC, the programmer first initializes then senses the status of the BIC and the selected peripheral controller. After a not-busy response is received from both the BIC and the peripheral controller, the BIC address registers are loaded with the initial and final memory addresses of the block of data to be transferred, a BIC activate enable instruction is placed on the I/O cable, and the transfer is started. Although the program requires loops for use with sense instructions and to handle abnormal conditions, transfer of the data block is accomplished by the BIC without further program instructions.

The key bit register (for memory map option) is loaded by first issuing the "Enable (loading of) Key Bit Register" instruction (0100321) followed by one of the "Load Final Register" instructions (0103021, 0103121, 0103221).

## 3.3 SAMPLE PROGRAM

Table 3-2 shows a typical service routine for the BIC, a Teletype paper tape punch operation under BIC control. Using DAS symbols with corresponding machine language

Table 3-2. Typical Service Routine

| Memory   | Octal    |       |           | Variable       |                |             |

|----------|----------|-------|-----------|----------------|----------------|-------------|

| Location | Code     | Label | Operation | Field          | Comments       |             |

| 001000   |          |       | , ORG     | ,01000         |                |             |

| 001000   | 101020   | BIC0  | , SEN     | ,020,BIC1      | CK BIC NOT BUS | Y           |

| 001001   | 001007 R |       |           |                |                |             |

| 001002   | 100401   |       | , EXC     | ,0401          | INIT TTY       |             |

| 001003   | 100021   |       | , EXC     | ,021           | INIT BIC       |             |

| 001004   | 005000   |       | , NOP     | ,              |                |             |

| 001005   | 001000   |       | , JMP     | , <b>*</b> – 3 |                |             |

|          |          |       |           |                |                | (continued) |

### **OPERATION**

Table 3-2. Typical Service Routine (continued)

| Memory<br>Location | Octal<br>Code | Label | Operation | Variable<br>Field | Comments           |

|--------------------|---------------|-------|-----------|-------------------|--------------------|

| 001006             | 001002 R      |       | •         |                   |                    |

| 001007             | 101101        | BIC1  | , SEN     | ,0101,BIC2        | CK TTY WRITE READY |

| 001010             | 001014 R      |       | •         | , ,               |                    |

| 001011             | 005000        |       | , NOP     | ,                 |                    |

| 001012             | 001000        |       | , JMP     | ,*-3              |                    |

| 001013             | 001007 R      |       | •         | •                 |                    |

| 001014             | 103120        | BIC2  | , OAR     | ,020              | SET BIC I REG      |

| 001015             | 103221        |       | , OBR     | ,021              | SET BIC F REG      |

| 001016             | 100020        |       | , EXC     | ,020              | ACTIVATE BIC       |

| 001017             | 100101        |       | , EXC     | ,0101             | CONNECT WRITE REG  |

| 001020             | 101020        |       | , SEN     | ,020,BIC3         | CK BIC NOT BUSY    |

| 001021             | 001025 R      |       |           |                   |                    |

| 001022             | 005000        |       | , NOP     | ,                 |                    |

| 001023             | 001000        |       | , JMP     | ,*-3              |                    |

| 001024             | 001020 R      |       |           |                   |                    |

| 001025             | 101021        | BIC3  | , SEN     | ,021,BIC5         | CK ABN STOP        |

| 001026             | 001032 R      |       |           |                   |                    |

| 001027             | 007400        |       | , ROF     | ,                 |                    |

| 001030             | 102520        | BIC4  | ,CIA      | ,020              | INPUT BIC I REG    |

| 001031             | 000000        |       | , HLT     | ,                 |                    |

| 001032             | 007401        | BIC5  | , SOF     | ,                 | SET ABN FLAG       |

| 001033             | 001000        |       | , JMP     | ,BIC4             |                    |

| 001034             | 001030 R      |       |           |                   |                    |

|                    | 000000        |       | , END     | •                 |                    |

|                    |               |       |           |                   |                    |

octal codes, the program covers memory locations 01000 through 01034.

Once the program is loaded, the operator must insert the initial punch buffer address into the A register and the final address into the B register for each run. When started, the program will:

- a. initialize the BIC and Teletype punch

- b. initiate the data transfer

- c. read the contents of the BIC initial register into the A register at the completion of the transfer

- d. set the overflow indicator if the termination was abnormal

- e. halt

The punch buffer must contain only ASCII characters. The first character is 0222 (punch on) and the last is 0224 (punch off).

# SECTION 4 THEORY OF OPERATION

The BIC is functionally divided into address registers and a sequence control circuit (figure 4-1). A functional description of these circuits is provided in the following paragraphs.

### 4.1 ADDRESS REGISTERS

The two address registers contain the memory locations of output or input data, depending on the I/O instruction. The initial register stores the address of the first input or output word, and is incremented during each data-word transfer. When the block transfer is complete, the initial register contains the address  $+\ 1$  of the last data word to be transferred.

The final register stores the address of the last word to be transferred. Unless the peripheral device is abnormally stopped, the address in the final register will be one less than the address in the initial register when the block transfer is complete. When the initial and final registers reach comparison, the block word transfer is complete.

The key-bit register stores the four key bits that are used with the memory map. The key-bit register is not used on systems without the memory map. The enable instruction sets a flip-flop which directs the data being transferred by a load (of final register) instruction, into the key-bit register. The flip-flop is reset when the transfer is complete.

## 4.2 SEQUENCE CONTROL

The sequence control circuit generates the control signals which coordinate address and data transfer between the processor, BIC, and the peripheral controllers. The data are not routed through the BIC but are directly transferred between the peripheral controller and memory.

Under program control, the processor senses that the BIC is not busy and prepares the BIC to receive the initial and final data addresses. The processor then senses that the selected peripheral controller is not busy and loads the initial and final registers and the key register. The BIC is then activated and the peripheral controller is started. The BIC then assumes control of the data transmission, allowing the processor operational registers to be used by the program for other functions.

Data transfer is accomplished between memory and the peripheral controller via the I/O bus. The BIC counts the words transferred and when the data block transfer is complete, disconnects the peripheral controller and assumes a not-busy state. Data transfer may also be terminated upon request from the peripheral controller.

## 4.3 OPERATING SEQUENCE

The following paragraphs describe the sequence of operations of the BIC. Refer to the block diagram (figure 4-1), the timing diagram (figure 4-2), and the logic diagram 91C0459 in volume 2.

#### 4.3.1 Initial Conditions

The processor senses the BIC for a not-busy condition. The sense instruction places the BIC device address and a function code on the I/O bus. The BIC responds with a low SERX-I if it is not busy (CDCX-B low). The processor then executes the initialize instruction which generates a low INIT- which prepares BIC for receiving the initial and final addresses of the block data to be transferred.

The initial register is loaded from the I/O bus when data ready DRYX—I returns high and Llxx— is low.

The final register is loaded from the I/O bus when DRYX—I returns high, and LFRX + is high.

## 4.3.2 Device Selection

The processor executes the activate BIC instruction which causes DCEX-B to go low. This signal is sent to all peripheral controllers connected to the BIC. The processor then executes an instruction to select a peripheral device. This instruction with DCEX-B low, connects the selected device to the BIC and starts the device.

The connected peripheral controller sends a low CDCX-B to the BIC causing DCEX-B to go high, thus disabling the selection of any other peripheral controllers. When CDCX-B goes low, the connected peripheral controller also selects the state of TROX-B. When data is to be transferred to memory, a high TROX-B is sent. If data is to be transferred to memory, a low TROX-B is sent.

### 4.3.3 Data Address

When the connected peripheral controller is ready for the data transfer, it sends a low TRQX-B to the BIC. The BIC then sends a TPIX-I or low TPOX-I to the processor, depending on the state of TROX-B.

When the processor is ready for the data transfer, it sends a low IUAX—I to the BIC. IUAX—I going low generates a low TAKX—B which is sent to the peripheral controller to initiate the transfer. The BIC then causes OIRX + to go high which gates the memory address, that is in the initial register plus the key bits onto the I/O bus. The connected peripheral controller is thus enabled. FRYX—I, from the processor, going high terminates the address phase of the BIC. FRYX—I going high causes CLEX— to go high, which

Figure

**BIC Block Diagram**

#### NOTES:

- (1) TIMING REQUIRED TO ISSUE THE COMMAND TO CONNECT THE DEVICE.

- TIME REQUIRED FOR DEVICE TO REQUEST FIRST DATA TRANSFER AFTER STARTING.

- 3 TIME REQUIRED TO SERVICE CURRENT AND/OR HIGHER PRIORITY REQUESTS FOR I/O ACCESSES.

- (4) SIGNAL TRQX-B MAY BE BROUGHT LOW (TRUE) AGAIN, AS EARLY AS THE TRAILING EDGE OF DRYX-1. HOWEVER, SIGNAL TRQX-B MUST HAVE BEEN HIGH FOR AT LEAST 50 NANOSECONDS BEFORE GOING LOW.

- (5) END OF DATA BLOCK. SIGNAL CDCX MAY REMAIN HIGH BETWEEN BLOCKS.

- (6) INCLUDES KEY BITS IF PRESENT [IOKn-I (0-3)].

- (7) FOR DMA TIMING REFER TO THE APPLICABLE SYSTEM HANDBOOK.

#### THEORY OF OPERATION

causes the initial register to be incremented to the next memory address.

### 4.3.4 Data Transfer

The data transfer may be an output from or an input to the processor. For output, the processor places the data on the I/O bus, and the data is strobed into the peripheral controller by DRYX-I going high. For input, the peripheral controller places the data on the I/O bus when FRYX-I goes high and removes the data when DRYX-I goes high. BIC keeps TAKX-B low until the end of the transfer when IUAX-I goes high.

#### 4.3.5 Transfer Termination

When the contents of the initial and final registers become equal, the comparator circuit generates a high IEFX—. This creates a low DESX—B which is sent to the peripheral controller. The peripheral controller then causes CDCX—B to go high. This causes the BIC to assume a not busy state. The transfer of data is thus terminated.

When an abnormal device stop occurs, the peripheral controller terminates the transfer without regard to the contents

of the initial and final registers. The peripheral controller generates a low BCDX—B. This causes a low DESX—B to be sent to the peripheral controller. The peripheral controller responds with a high CDCX—B. This causes the BIC to assume a not busy state. The transfer of data is thus terminated. After an abnormal device stop, the processor can read the contents of the initial register to determine the number of words that were transferred. The number in the initial register will be the address of the last word transferred plus one.

An abnormal device stop can occur as a result of any of the following situations: the length of the data block is unknown, and the device has detected the end of the data; the peripheral controller has detected an invalid operation of the device; the processor has issued an instruction to stop the operation of the peripheral device.

Another abnormal stop is created when an error is detected by the memory map during a BIC operation. The error causes BIMES—I to go low. This causes a low DESX—B to be sent to the peripheral controller. The peripheral controller responds with a high CDCX—B. This causes the BIC to assume a not busy state. The transfer of data is then terminated

## SECTION 5 MAINTENANCE

Maintenance personnel should be familiar with the contents of this manual before attempting to troubleshoot the BIC. The Varian MAINTAIN II test program system (Test Programs Manual, 98 A 9952 06x)\* contains a BIC test program used to test various phases of the BIC operation. Further diagnosis can then be made by referring to this manual.

## **5.1 TEST EQUIPMENT**

The following test equipment and tools are recommended for maintenance:

- a. Oscilloscope, Tektronix type 547 with dual-trace plug-in unit, or equivalent.

- b. Multimeter, Triplett type 630 or equivalent.

- c. Soldering iron, 39-watt pencil type.

- d. Card extender VDM p/n 44P0540.

## 5.2 CIRCUIT-COMPONENT IDENTIFICATION

All reference designations used in the logic diagram appear on the BIC board adjacent to each component. Component part numbers can be found in the parts list in volume 2.

### 5.3 CIRCUIT-BOARD REPAIR

If it has been determined that circuit-board repair is required, it is recommended that the Varian Data Machines customer service department be contacted so that a new circuit board can be installed in the user's system and the faulty one returned to the factory for repairs. However, if the user decides to perform his own repairs, caution should be used so that the circuit board is not permanently damaged. Approved repair procedures should be followed such as the ones described in document IPC-R-700A prepared by the Institute of Printed Circuits.

<sup>\*</sup>The x at the end of the document number is the revision number and can be any digit 0 through 9.

## **SECTION 6 MNEMONICS**

|              | provides an alphabetized list of the signal sused in the BIC.                                       | Mnemonic | Description                                                                                                        |

|--------------|-----------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------|

|              | Table 6-1. Mnemonics                                                                                | EKBR     | Enable loading of key bit register. Gates the key bits into the key-bit register.                                  |

| Mnemonic     | Description                                                                                         | FRYX     | Function ready. Indicates the I/O bus contains an address.                                                         |

| ACEX         | Activate enable. Stores activation of BIC.                                                          | FiiX     | Final register bit. Stores bit ii of the final address.                                                            |

| ADSX<br>BCAX | Abnormal device stop. Stores end of data from peripheral controller.                                | IEFX     | Initial equals final. Indicates that the contents of the initial register is equal to the contents                 |

| BCAX         | Buffer controller activate. Stores the activation of the BIC and the peripheral controller.         | IFMX     | of the final register.  Initial equals final memory. Clears                                                        |

| BCDX         | Buffer controller deactivate. Initiates termination of data transfer by the peripheral controller.  |          | the BIC active flip-flop when the contents of the initial register is equal to the contents of the final register. |

| BIMES        | BIC map error stop. Stores the map error indication during a                                        | INIT     | Initialize. Resets BIC flip-flops to their initial condition.                                                      |

| CARx         | BIC operation.  Carry out. Increments the next higher position of the initial                       | INTX     | Interrupt request. Used to request an interrupt when the block transfer is complete.                               |

|              | register on overflow.                                                                               | IOKi     | Key-bit register output i to I/O bus.                                                                              |

| CDCX         | Controller device connected. Indicates that the peripheral controller to be connected is connected. | IUAX     | Interrupt acknowledge. Indicates that the processor is ready to send or receive data.                              |

| CLEX         | Clock enabled. Enables the initial register to be incremented.                                      | IUCX     | Interrupt clock. Provides timing for servicing BIC.                                                                |

| DA           | Device address decode. Gates the device address from the I/O bus.                                   | liiX     | Initial register data bit. Stores<br>bit ii of the initial address.                                                |

| DCEX         | Device connect enable. Enables the selection of a peripheral                                        | LFRX     | Load final register. Loads data on I/O bus into final register.                                                    |

| DESX         | Device stop. Stores the requirement to stop the peripheral device.                                  | LFXX     | Load final. Gates the I/O bus contents into the key-bit register when EKBR is set.                                 |

| DRYX         | Data ready. Indicates the I/O bus contains a word of data.                                          | LIXX     | Load initial register. Loads data on I/O bus into initial register.                                                |

| DSTX         | Device stop enable. Stores the end of the data transfer.                                            | MESX     | Map error stop. Indicates that there was a memory map error                                                        |

| EBii         | E-bus bit. Address or function code bits from the I/O bus.                                          |          | during a BIC operation.  (continued)                                                                               |

## **MNEMONICS**

|          | Table 6-1. Mnemonics (continued)                                        | Mnemonic Description |                                                                                |  |

|----------|-------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------|--|

| Mnemonic | Description                                                             | TAKX                 | Trap acknowledge. Indicates that the requirements for data transfer            |  |

| OIRX     | Output initial register. Gates                                          |                      | have been met.                                                                 |  |

|          | contents of initial register and key-bit register onto the I/O bus.     | TCOX                 | Trap command. Synchronizes trap request with interrupt clock.                  |  |

| PLUP     | Pullup voltage.                                                         | TPDX                 | Trap request detect. Detects the                                               |  |

| PRMX     | Priority in. Gives priority to BIC.                                     |                      | peripheral controller request for a trap.                                      |  |

| PRNX     | Priority out. Passes priority to next in line after BIC is serviced.    | TPIX                 | Trap in. Indicates that the BIC is ready to transfer data to the processor.    |  |

| RIXX     | Read initial register. Stores                                           |                      |                                                                                |  |

|          | requirement of processor to read contents of initial register.          | TPOX                 | Trap out. Indicates that the BIC is ready to transfer data from the processor. |  |

| RTPD     | Reset trap detect. Resets the trap                                      |                      |                                                                                |  |

|          | request detection flip-flop.                                            | TROX                 | Trap out (from peripheral). Indicates the direction (in or out) of the data    |  |

| SERX     | Sense response. Indicates whether the BIC is busy.                      |                      | transfer.                                                                      |  |

|          |                                                                         | TRQX                 | Trap request. Indicates that the                                               |  |

| SYRT     | System reset. Generates initialize signal when SYSTEM RESET is pressed. |                      | peripheral controller is ready for a data transfer.                            |  |