varian data machines /a varian subsidiary

DATA COMMUNICATIONS

MULTIPLEXOR

MANUAL

D.W. MCCUTCHEON

### **DATA COMMUNICATIONS MULTIPLEXOR MANUAL**

Specifications Subject to Change Without Notice

#### NOTE

This manual covers the following models

5201 Right-hand 16-line multiplexor

5202 Left-hand 16-line multiplexor

5203 Right-hand 32-line multiplexor

5204 Left-hand 32-line multiplexor

5205 Maximum 64-line multiplexor

5301 Asynchronous RS232 modem line adapter

5302 Direct-connection RS232 line adapter

5303 Direct-connection current-loop line adapter

5304 Direct-connection relay line adapter

5305 Synchronous RS232 modem line adapter

### TABLE OF CONTENTS

#### **SECTION 1 INTRODUCTION**

| 1.1 PHYSICAL DESCRIPTION                                     |      |

|--------------------------------------------------------------|------|

| 1.2 OPTIONS                                                  |      |

| 1.3 RELATED PUBLICATIONS                                     | 1-3  |

|                                                              |      |

| SECTION 2 MULTIPLEXOR UNIT                                   |      |

| SECTION 2 MIDELIFIEROR UNIT                                  |      |

| 2.1 INSTALLATION                                             | 2.2  |

| 2.1.1 Physical Description                                   |      |

| 2.1.1.1 Multiplexor Unit Board 1                             |      |

| 2.1.1.2 Multiplexor Unit Board 2                             |      |

| 2.1.2 Interfaces                                             |      |

| 2.1.2.1 E-Bus                                                |      |

| 2.1.2.2 Multiplexor Bus                                      |      |

| 2.2 THEORY OF OPERATION                                      |      |

| 2.2.1 E-Bus Interface (MU Board 2)                           |      |

| 2.2.2 Interface Buffer and Byte-Selection Logic (MU Board 1) |      |

| 2.2.3 Scan Counter and Decoder (MU Board 1)                  |      |

| 2.2.4 Instruction Decoder (MU Board 2)                       |      |

| 2.2.5 Interrupt Logic (MU Board 2)                           |      |

| 2.2.6 Trap Logic (MU Board 2)                                |      |

| 2.2.7 Control Logic (MU Board 1)                             |      |

| 2.2.8 Control-Character Checking Logic (MU Board 1)          |      |

| 2.2.9 Clock and Bit-Rate Generator (MU Board 1)              |      |

| 2.2.10 Multiplexor Bus (MU Board 2)                          |      |

| 2.2.11 DMA Logic (MU Board 2)                                |      |

| 2.3 MAINTENANCE                                              |      |

| 2.3.1 Functional Tests Requiring the DCM Test Program        |      |

| 2.3.2 Tests Not Covered by the DCM Test Program              |      |

| 2.3.3 Suggested Methods                                      |      |

| 2.4 PROGRAMMING                                              |      |

| 2.4.1 DCM Instructions                                       |      |

| 2.4.2 DCM Interrupts                                         |      |

| 2.4.2.1 Input Byte-Count Zero                                |      |

| 2.4.2.2 Output Byte-Count Zero                               |      |

| 2.4.2.3 Line Error                                           |      |

| 2.4.2.4 Status Change                                        |      |

| 2.4.2.5 Control-Character Detected                           |      |

| 2.4.2.6 Control                                              |      |

| 2.4.3 DCM DMA Control Table                                  |      |

| 2.4.4 Programming Sequences                                  |      |

| 2.4.4.1 Input Sequence                                       |      |

| 2.4.4.2 Output Sequence                                      |      |

| 2.4.4.3 Status-Request Sequence                              |      |

| 2.4.4.4 Computer-Control Sequence                            |      |

| 2.5 MNEMONICS                                                |      |

|                                                              | 2 37 |

| 4.2.7 Asynchronous Receiver/Transmitter                         |      |

|-----------------------------------------------------------------|------|

| 4.2.8 Transmit-Break Logic                                      |      |

| 4.2.9 RS232 Modem Interface                                     |      |

| 4.3 MAINTENANCE                                                 | 4 1  |

| 4.3.1 Functional Tests                                          |      |

| 4.3.2 Other Problems                                            | 4 1  |

| 4.4 PROGRAMMING                                                 | 4 1  |

| 4.4.1 Interrupts                                                | 4 1  |

| 4.4.1.1 Line Error                                              | 4 1  |

| 4.4.1.2 Status Change                                           | 4 1  |

| 4.4.2 Programming Sequences                                     |      |

| 4.4.2.1 Line Setup Sequence                                     |      |

| 4.4.2.2 Read Line-Status Sequence                               |      |

| 4.5 MNEMONICS                                                   |      |

|                                                                 |      |

| SECTION 5 SYNCHRONOUS RS232 MODEM LINE-ADA                      | PTER |

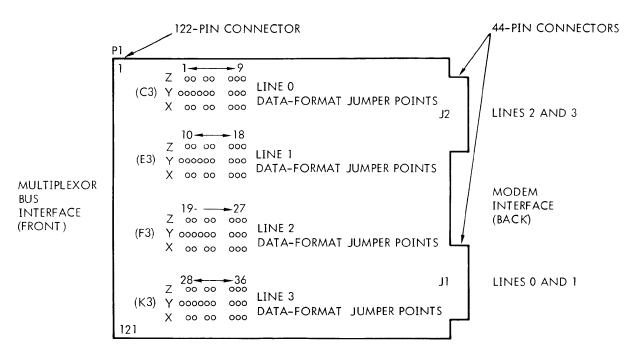

| 5.1 INSTALLATION                                                | 5-3  |

| 5.1.1 Physical Description                                      | 5-3  |

| 5.1.2 Interfaces                                                | 5-3  |

| 5.1.2.1 Multiplexor Bus                                         |      |

| 5.1.2.2 RS232 Modem Interface                                   | 5-3  |

| 5.1.3 Options                                                   |      |

| 5.1.4 Test Clock Selection                                      |      |

| 5.1.5 Protective Ground (RS232C Circuit AA)                     |      |

| 5.2 THEORY OF OPERATION                                         |      |

| 5.2.1 Multiplexor Bus Interface                                 |      |

| 5.2.2 Service Request Logic                                     |      |

| 5.2.3 Control Logic                                             |      |

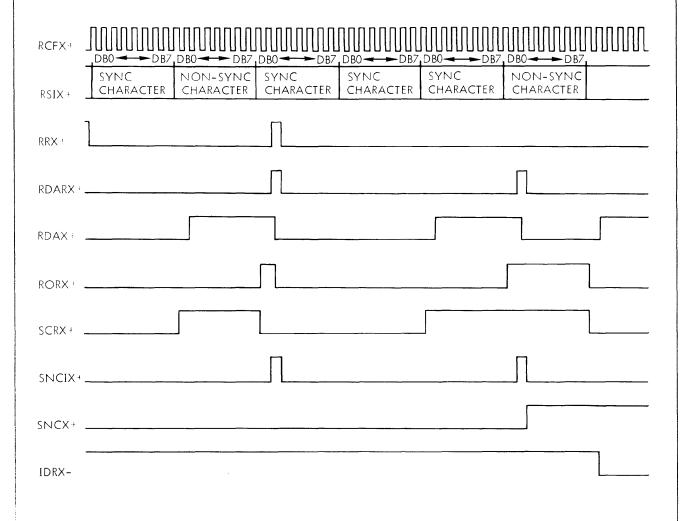

| 5.2.4 Synchronous Receiver/Transmitter                          |      |

| 5.2.5 Sync-Detection Logic                                      |      |

| 5.2.6 Control-Channel Edge-Detectors.                           |      |

| 5.2.7 RS232 Modem Interface                                     |      |

| 5.2.8 Strobe Logic                                              |      |

| 5.3 MAINTENANCE                                                 |      |

| 5.3.1 Functional Tests                                          |      |

| 5.3.2 Other Problems.                                           |      |

| 5.4 PROGRAMMING                                                 |      |

| 5.4.1 Interrupts                                                |      |

| 5.4.1.1 Line Error                                              |      |

| 5.4.1.2 Status Change                                           |      |

| 5.4.2 Programming Sequences                                     |      |

| 5.4.2.1 Line Setup Sequence                                     |      |

| 5.4.2.2 Read Line Status Sequence                               |      |

| 5.5 MNEMONICS                                                   |      |

| J.J. IMITEMORIOS                                                | 5.19 |

| LIST OF ILLUSTRATIONS                                           |      |

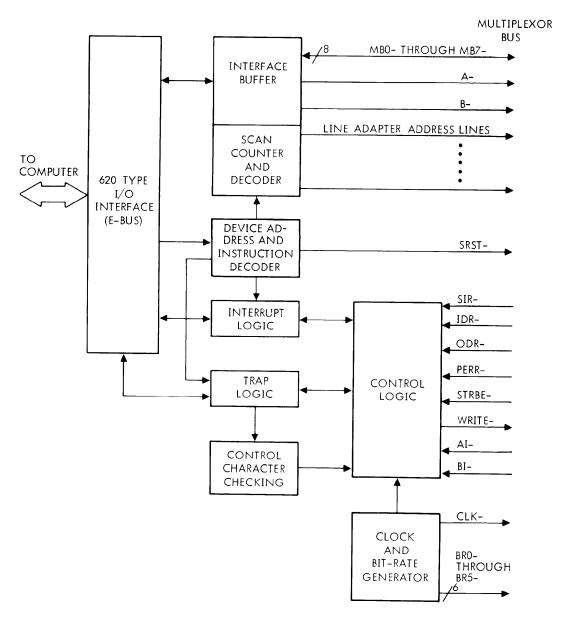

| Figure 1-1. Data Communications Multiplexor (DCM) Block Diagram | 1-2  |

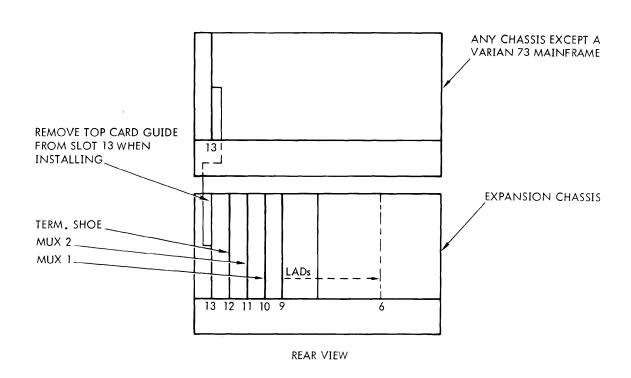

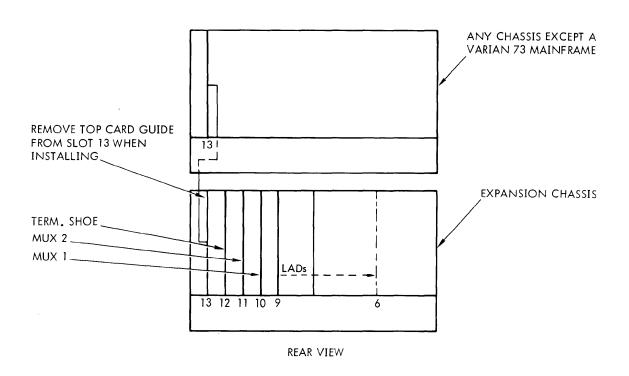

| Figure 1-2. Typical Installation                                | 1.3  |

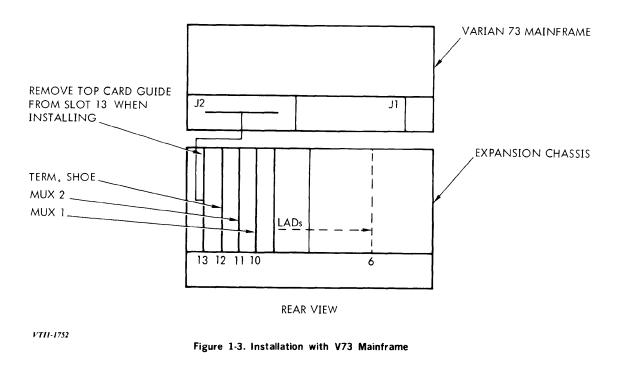

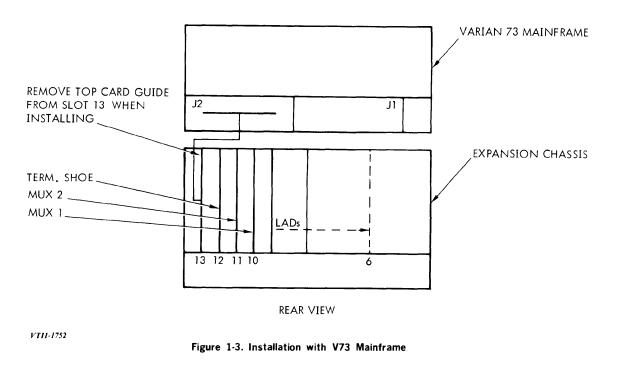

| Figure 1-3. Installation with V73 Mainframe                     | 1.3  |

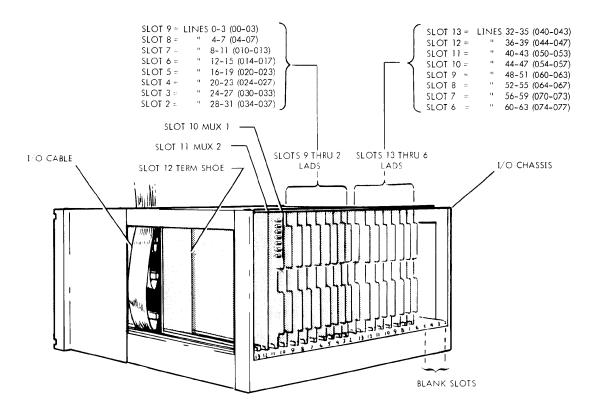

| Figure 1-4. 32-Line DCM Configurations                          | 1.4  |

| Figure 1-5. 64-Line DCM Configurations                          | 1.5  |

| Figure 2-1. DCM Multiplexor-Unit Simplified Block Diagram       | 2-1  |

|                                                                 |      |

# \_\_\_\_\_ varian data machines

| Table 2-13. Input Sequence     2-2                                      |

|-------------------------------------------------------------------------|

| Fable 2-14. Status Input Sequence   2-2                                 |

| Table 2-15. Processor Write Sequence2-27                                |

| Table 2-16. Processor Read Sequence2-28                                 |

| Table 2-17. Line Error Sequence2-28                                     |

| Table 2-18. Control Memory Contents2-29                                 |

| Table 2-19. DCM Instructions2-33                                        |

| Table 3-1. Direct-Connection LAD Specifications3-2                      |

| Table 3-2. Direct-Connection LAD Line-Interface Comparison              |

| Table 3-3. Cable Length vs. BPS Rate                                    |

| Table 3-4. RS232 Interface Pin Connections                              |

| Table 3-5. Current-Loop Interface Specifications3-5                     |

| Table 3-6. Current-Loop Interface Pin Connections                       |

| Table 3-7. Relay Interface Specifications3-7                            |

| Table 3-8. Relay Interface Pin Connections                              |

| Table 3-9. Line Bit-Rate Selection                                      |

| Table 3-10. Pin Functions of the Asynchronous Receiver/Transmitter 3-12 |

| able 4-1 Asynchronous RS232 LAD                                         |

| able 4-2. Line Bit-Rate Selection4-4                                    |

| able 4-3. Protective Ground Jumpers 4-6                                 |

| able 4-4 Pin Functions of the Asynchronous Receiver/Transmitter49       |

| able 4-5. RS232 Signal Locations 4-12                                   |

| Table 5-1. Synchronous RS232 LAD Specifications                         |

| able 5-2. Data Format Jumpers5-4                                        |

| able 5-3. Parity Jumpers 5-4                                            |

| able 5-4. Line Bit-Rate Selection                                       |

| able 5-5. Protective Ground Jumpers 5-5                                 |

| able 5-6. Pin Functions of the Synchronous Receiver/Transmitter 5-8     |

| Table 5-7. RS232 Signal Locations 5 12                                  |

## SECTION 1 INTRODUCTION

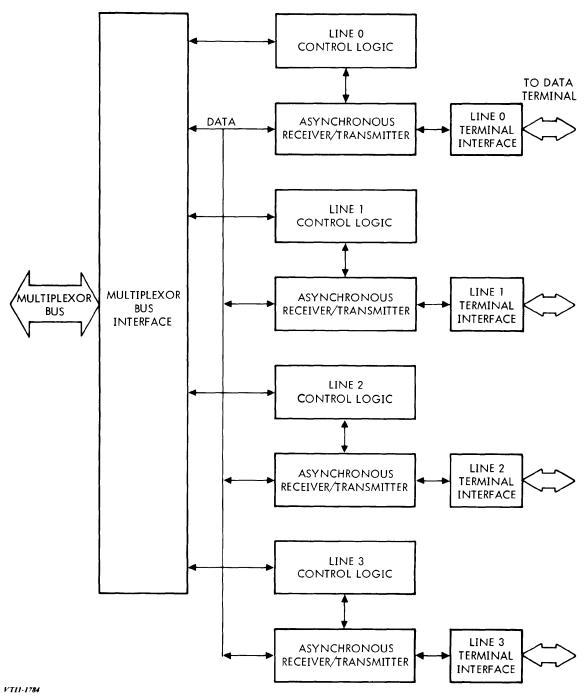

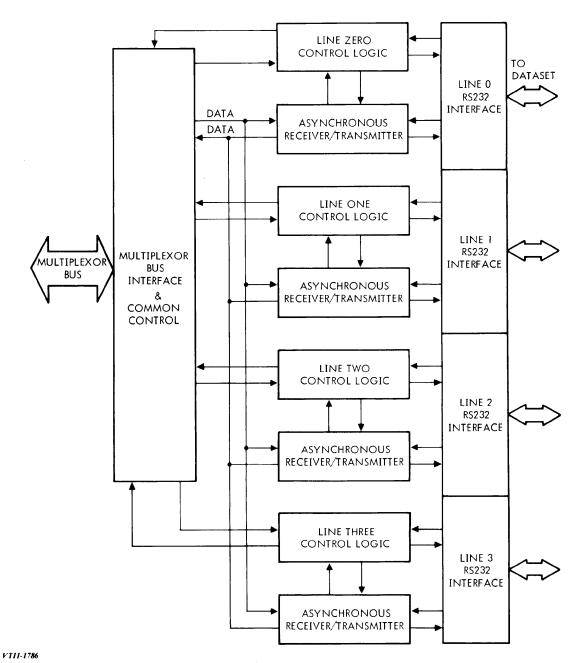

The data communications multiplexor (DCM, figure 1-1) provides a low cost multiport interface between Varian Data Machines computers (with 620-type I/O) and up to 64 full-duplex serial devices. These devices can be serial peripherals and/or serial modems. The DCM consists of a multiplexor unit (MU), multiplexor buses, and several types of line adapter (LAD). The multiplexor bus scheme allows a wide variety of LADs to be added as new needs arise.

The DCM provides communication between the LADs and the computer via programmed I/O and direct-memory access (DMA). The multiplexor logic handles interrupts and trap requests (DMA) internally, and therefore does not require an external priority interrupt module (PIM) or a buffer interlace controller (BIC). For DMA operation, the DCM uses a control table stored in the computer memory. The table contains control characters, output and input block-lengths, output and input buffer-locations, and control information for each line. DCM accesses this table through the computer DMA with individual line addresses as pointers.

The individual lines are set up under program control to begin a transfer-in, transfer-out, or both (full duplex). Once the line is set up the multiplexor inputs or outputs data to/from the line on a demand basis using the DMA port of the computer. The program is interrupted only for a line error, control-character detection, or at completion of the transfer. The data are automatically packed or unpacked by the multiplexor hardware.

The character assembly, disassembly, parity generation, parity checking, modem control and buffering tasks are handled at the LAD level.

Communication between the line adapters and the multiplexor is via the multiplexor bus, which consists of an eight-bit bidirectional bus, 12 control lines, and 12 addressing lines. The multiplexor also provides six bit-rate lines for the asynchronous LADs. These lines go to all LAD locations, and are connected as needed. The frequency of these lines is determined by hardware jumpering options on the multiplexor.

The DCM is usually installed in a 620 or V73 I/O expansion chassis. It consists of the two multiplexor printed-circuit boards, the LAD complement, and one or two half-backplane assemblies. Systems that handle over 32 lines require two half-backplanes and consequently one entire I/O expansion chassis.

In this manual, section 2 describes the MU and associated buses. Each subsequent section describes one type of LAD.

Each section concludes with a subsection containing applicable programming information. General DCM programming is discussed at the end of section 2. In each LAD

section, only programming peculiar to that line adaptor is discussed.

Logic diagrams and engineering drawings are contained in Volume 2 of this manual.

#### 1.1 PHYSICAL DESCRIPTION

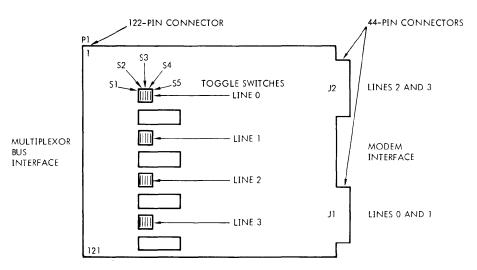

The DCM consists of two multiplexor printed circuit boards (MU), one or two special I/O backplanes, and up to 16 LAD boards (each LAD can handle four lines). Systems with 32 or fewer lines require only one backplane. See (figures 1-2 through 1-5). The DCM backplane(s) is (are) installed in a standard 620 or V73 I/O expansion chassis. A DCM system larger than 32 lines occupies the entire I/O chassis. If a single-backplane DCM occupies a chassis by itself, a righthand backplane should be used; but if the DCM is to share the chassis with an I/O backplane, a lefthand DCM backplane and a righthand I/O backplane must be used.

LADs are plugged into the backplane starting in slot 9 next to multiplexor board 1. The slot location of the LAD determines its addresses, i.e., the LAD in slot 9 handles lines 0 through 3 and the one in slot 10 handles lines 4 through 7 and so on. If the DCM systems is larger than 32 lines, slot 13 of the second backplane handles lines 32 through 35, etc. Interface to the modems or direct-connection terminals is through two connectors on the back of the LADs (see sections on individual LADs).

The DCM operates at 0 to 50 degrees C and 0 to 90 percent relative humidity (without condensation).

The MU requires a +5V dc ± 5 percent input at 3.5A while a typical LAD requires the following power inputs:

- + 5V dc  $\pm$  5 percent at 1.2 A

- + 12V dc ±2.5 percent at 100mA

- 12V dc  $\pm$  2.5 percent at 150 mA

#### 1.2 OPTIONS

The scan-length, scan-counter, and bit-rate lines can be hardwired to provide optimum performance for a particular system. There is also a priority scan in which the DCM resets to line 0 after the second service request. Details on these options are given in the applicable sections of the manual.

#### 1.3 RELATED PUBLICATIONS

The following publications are aids to understanding the DCM and the systems to which it is applicable.

Varian 73 System Handbook

98 A 9906 010

Varian 620 100s Computer Handbook

98 A 9905 003

VTI1-1751

Figure 1-2. Typical Installation

VTI1-1751

Figure 1-2. Typical Installation

REAR VIEW

VT11-1910

Figure 1-5. 64-Line DCM Configurations

## SECTION 2 MULTIPLEXOR UNIT

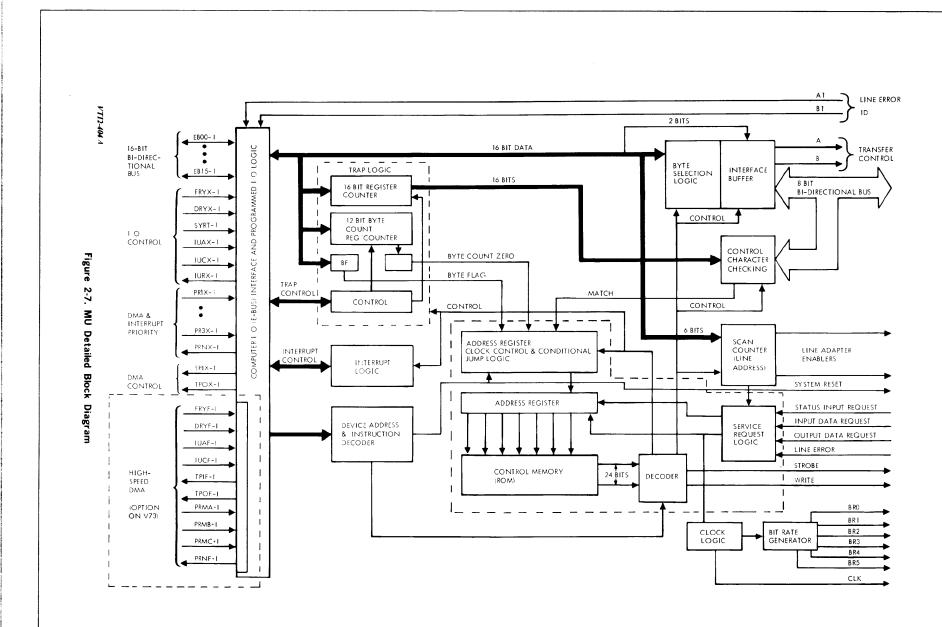

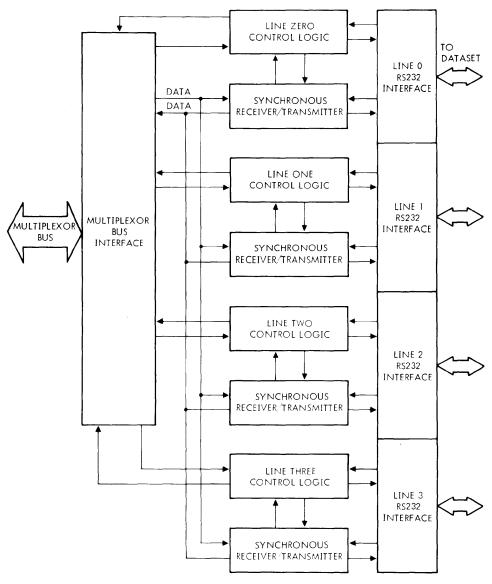

The multiplexor unit (MU, figure 2-1) is on two printed-circuit boards that fit slots in a special 620-type expansion chassis. It provides communication between the LADs and the computer via the programmed I/O and the DMA. The MU logic handles interrupts and (DMA) trap requests internally and therefore does not require an external priority-interrupt module (PIM) or a buffer-interlace control-

ler (BIC). In DMA operations, the MU uses a control table in the computer memory. The control table contains control characters, output- and input-block lengths, output- and input-buffer addresses and control information for each line. MU access to this table is through the computer DMA, using the individual line addresses as pointers.

VT11-1679.1

Figure 2-1. DCM Multiplexor-Unit Simplified Block Diagram

circuit board that contains 88 integrated circuits. The following paragraphs describe the jumpering options on this board.

Bit-Rate Selection: Board 1 contains two odd-bit-rate counters (variable bit rate counters). Counter number one provides for dividing the input or base frequency by any even number from 2 to 8190, and counter number two divides the base frequency by any even number for 2 to 1022. The output of these counters can then clock the asynchronous LADs. The frequency of the output is varied by adding (or deleting) jumper clips corresponding to the set bits of a binary number determined by the formula:

|     | base frequency        |     |

|-----|-----------------------|-----|

| n = |                       | - 1 |

|     | 2 x desired frequency |     |

where n is rounded to the nearest whole number and converted to binary; and is less than 4096 for counter one, and less than 512 for counter two.

Tables 2-2 and 2-3 give the jumper locations corresponding to the various bits and to the base-frequencies of counters 1 and 2, respectively. The outputs of counters 1 and 2 are at board-1 points X33 and X34, respectively. Table 2-4 gives values of n for some common frequencies.

Board 1 provides six clocks for the LADs. The frequencies of these clocks are determined by jumpers (table 2-5). The clocks are jumpered into the LADs at the backplane per system requirements.

Table 2-2 Odd-Bit-Rate Counter 1

#### **Jumper Locations**

| Value of n<br>(Binary Weight)                        | Jumper Locations (Board                                                                         |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Bit                                                  |                                                                                                 |

| 0 (1) 1 (2) 2 (4) 3 (8) 4 (16) 5 (32) 6 (64) 7 (128) | X15 to W15 X16 to W16 X17 to W17 X18 to W18 * X19 to W19 X20 to W20 * X21 to W21 * X22 to W22 * |

| 8 (256)<br>9 (512)<br>10 (1024)<br>11 (2048)         | X23 to W23<br>X24 to W24 *<br>X25 to W25<br>X26 to W26 *                                        |

#### **Base-Frequency Selection**

| Base Frequency | Jumper Locations (Board 1) |

|----------------|----------------------------|

| 9.8304 MHz     | V19 A to V14 *             |

| 4.9152 MHz     | V20 to V14                 |

| 2.4576 MHz     | V15 to V14                 |

| 1.2288 MHz     | V16 to V14                 |

| 0.6144 MHz     | V17 to V14                 |

| 0.3072 MHz     | V18 to V14                 |

<sup>\*</sup> Indicates standard configuration that provides an output frequency of 1760 Hz (16 times 110 Hz).

Note: Asynchronous LADs require a clock frequency that is 16 times the line bit-rate.

Table 2-3. Odd-Bit-Rate Counter 2

#### **Jumper Locations**

| (Binary Weight) | Jumper Locations (Board 1) |

|-----------------|----------------------------|

| Bit             |                            |

| 0 (1)           | X7 to W7                   |

| 1 (2)           | X8 to W8                   |

| 2 (4)           | X9 to W9                   |

| 3 (8)           | X10 to W10                 |

| 4 (16)          | X11 to W11                 |

| 5 (32)          | X12 to W12                 |

| 6 (64)          | X13 to W13                 |

| 7 (128)         | X14 to W14                 |

|                 |                            |

#### Base-Frequency Selection

1)

| Base Frequency | Jumper Locations (Board 1) |

|----------------|----------------------------|

| 9.8304 MHz     | V19B to V13 *              |

| 4.9152 MHz     | V20 to V13                 |

| 2.4576 MHz     | V15 to V13                 |

| 1.2288 MHz     | V16 to V13                 |

| 0.6144 MHz     | V17 to V13                 |

| 0.3072 MHz     | V18 to V13                 |

<sup>\*</sup> Indicates standard configuration.

Note: Asynchronous LADs require a clock frequency that is 16 times the line-bit rate.

Table 2-5. Bit-Rate Selection (continued)

#### Line Adapter Clock Inputs (at Backplane)

| Line | Input Pin   | Remarks                                                                                                   |

|------|-------------|-----------------------------------------------------------------------------------------------------------|

| 0    | <b>9</b> 2  | Speed A for RS232 asynchronous LAD, input for direct-connection LAD, test clock for RS232 synchronous LAD |

| O    | <b>L</b> 94 | Speed B for RS232 asynchronous LAD                                                                        |

| 1    | <b>9</b> 3  | Speed A for RS232 asynchronous LAD, input for direct-connection LAD                                       |

| 1    | 91          | Speed B for RS232 asynchronous LAD                                                                        |

| 2    | <b>9</b> 8  | Speed A for RS232 asynchronous LAD, input for direct-connection LAD                                       |

| 2    | 95          | Speed B for RS232 asynchronous LAD                                                                        |

| 3    | <b>9</b> 7  | Speed A for RS232 asynchronous LAD, input for direct-connection LAD                                       |

| 3    | 96          | Speed B for RS232 asynchronous LAD                                                                        |

The RS232 asynchronous LAD requires two clocks per line, the direct-connection LAD requires one clock per line, and the RS32 synchronous LAD requires only one clock input for testing.

Scan-length selection: The number of lines scanned by the multiplexor is adjustable (table 2-6). The standard configuration depends on the DCM model number (i.e., 16, 32 or 64).

Priority-mode selection: The DCM can be put in the priority mode by jumpering point W6 to W5 on board 1. This simply causes the DCM to begin scanning at line zero after alternate service requests (either from a line or from the computer). Normally the DCM continues to scan lines sequentially. When priority mode is selected, the higher-speed lines should have the numerically lower addresses. This mode should only be used when a few high-speed lines are being run concurrently with a large number of low-speed lines. If the line speeds are all relatively close together, this mode should not be used. In priority mode, the scan length should be as close to the actual number of lines in use as possible.

Table 2-6. Scan-Length Selection

| Scan Length | Jumpers (Board 1)             |  |  |  |  |  |  |

|-------------|-------------------------------|--|--|--|--|--|--|

| 4 lines     | Points W4, W3, W2 and W1 open |  |  |  |  |  |  |

| 8 lines     | X3 to W3                      |  |  |  |  |  |  |

| 16 lines    | X3 to W3; X1 to W1            |  |  |  |  |  |  |

| 32 lines    | X3 to W3; X1 to W1; X2 to W2  |  |  |  |  |  |  |

| 64 lines    | X3 to W3; X1 to W1; X2 to W2; |  |  |  |  |  |  |

|             | X4 to W4                      |  |  |  |  |  |  |

#### 2.1.1.2 Multiplexor Unit Board 2

Board 2 contains the interface to the computer I/O. It is packaged on a 7-3/4-by-12-inch multiplexor printed circuit board that contains 90 integrated circuits. The following paragraphs describe the jumpering options on the board.

**Device-Address Selection:** The standard device-address is 070, but can be changed to any address from 00 to 077 by jumpers (table 2-7).

Table 2-9. Control Table (LCB) Beginning-Address Selection

| Beginning        |            | Jump       | ers (Bo    | oard 2)    |            |            |          | Beginning        |            | Jump       | ers (Bo    | ard 2)     |            |            |          |

|------------------|------------|------------|------------|------------|------------|------------|----------|------------------|------------|------------|------------|------------|------------|------------|----------|

| Address<br>Octal | W15<br>V15 | W14<br>V14 | W13<br>V13 | W12<br>V12 | W11<br>V11 | W10<br>V10 | W9<br>V9 | Address<br>Octal | W15<br>V15 | W14<br>V14 | W13<br>V13 | W12<br>V12 | W11<br>V11 | W10<br>V10 | W9<br>V9 |

| 00000            | Х          | Х          | Х          | Х          | Х          | Х          | Х        | 40000            | Х          | -          | Х          | Χ          | Х          | Х          | Х        |

| 01000            | Х          | Х          | Х          | Х          | Х          | Х          | -        | 41000            | X          | -          | X          | X          | X          | X          | -        |

| 02000            | Х          | X          | Х          | Х          | Х          | -          | Χ        | 42000            | X          | -          | X          | Х          | Х          | -          | Х        |

| 03000            | Х          | Х          | Х          | Х          | Х          |            |          | 43000            | Х          |            | X          | X          | X          | -          | -        |

| 04000            | Х          | Х          | Х          | X          | -          | X          | Χ        | 44000            | X          | -          | X          | X          | -          | Х          | X        |

| 05000            | X          | Х          | Х          | X          | -          | X          |          | 45000            | Х          | -          | X          | X          | -          | Х          | -        |

| 06000            | Х          | Х          | Х          | Х          | -          | -          | Χ        | 46000            | Х          | -          | X          | X          | -          | -          | Х        |

| 07000            | Х          | Х          | Х          | X          | -          | -          |          | 47000            | X          | -          | X          | X          | -          | -          | -        |

| 10000            | Х          | Х          | Х          |            | Х          | Х          | Χ        | 50000            | X          | -          | Х          |            | X          | Х          | Х        |

| 11000            | Х          | Х          | Х          |            | Х          | Х          |          | 51000            | Х          | -          | X          | -          | Х          | Х          | -        |

| 12000            | X          | Х          | Х          |            | Х          |            | Χ        | 52000            | Х          | -          | Х          |            | Х          | -          | Х        |

| 13000            | Х          | Х          | Х          | -          | Х          | -          | -        | 53000            | X          | -          | Х          |            | Х          | -          | -        |

| 14000            | Х          | Х          | Х          |            |            | Х          | Χ        | 54000            | Х          |            | X          | -          |            | Х          | X        |

| 15000            | Х          | Х          | Х          |            |            | Х          |          | 55000            | Х          |            | Х          |            | -          | Χ          | -        |

| 16000            | X          | Х          | Х          | -          |            |            | Χ        | 56000            | Х          |            | Х          |            | -          |            | X        |

| 17000*           | Х          | Х          | Х          |            |            |            |          | 57000            | Х          | -          | Х          |            | -          |            | -        |

| 20000            | Х          | Х          |            | Х          | Х          | Х          | X        | 60000            | Х          |            |            | X          | Х          | Х          | X        |

| 21000            | Х          | Х          | -          | Х          | Х          | Х          |          | 61000            | Х          |            |            | Χ          | Х          | Х          |          |

| 22000            | Х          | Х          | -          | Х          | X          | -          | Χ        | 62000            | Х          | -          |            | X          | X          | -          | Х        |

| 23000            | Х          | Х          | -          | Х          | X          | -          |          | 63000            | Х          | -          | -          | X          | X          |            | •        |

| 24000            | Х          | Х          | -          | Х          | -          | Х          | Χ        | 64000            | Х          | -          | -          | X          | -          | Χ          | Х        |

| 25000            | Х          | Х          | -          | Х          | -          | Х          |          | 65000            | Х          |            |            | X          |            | Х          | -        |

| 26000            | Х          | X          | -          | Х          |            |            | Х        | 66000            | Х          |            | -          | X          |            |            | Х        |

| 27000            | Х          | X          |            | Х          | -          | -          | -        | 67000            | X          |            |            | X          |            | -          | -        |

| 30000            | Х          | X          | -          |            | X          | Х          | Χ        | 70000            | Х          | -          |            |            | X          | X          | X        |

| 31000            | Х          | X          |            | -          | Х          | X          |          | 71000            | Х          |            | •          | -          | X          | Х          | -        |

| 32000            | Х          | Х          |            | -          | Х          | -          | X        | 72000            | Х          |            |            |            | X          |            | X        |

| 33000            | Х          | Х          |            |            | Х          | -          |          | 73000            | Х          |            | -          | -          | X          |            | -        |

| 34000            | X          | X          |            | -          | -          | ×          | Х        | 74000            | Х          | -          | -          | -          |            | X          | Χ        |

| 35000            | X          | X          | -          | -          |            | X          |          | 75000            | X          | -          |            |            |            | Х          |          |

| 36000            | X          | X          | -          | -          | -          | -          | Х        | 76000            | Х          |            | -          |            |            |            | Χ        |

| 37000            | Х          | X          |            |            |            | -          | -        | 77000            | Х          | -          | -          | -          |            | -          |          |

<sup>\* =</sup> Standard configuration.

Note: X indicates that a jumper is required.

Table 2-10. DMA Mode-Selection Jumpers

| High-Speed DMA | Jumpers (Board 2) |        | Normal DMA | Jumpers (Board 2) |        |

|----------------|-------------------|--------|------------|-------------------|--------|

| 1              | S1 to S2          | FTEN-  | 1          | Z1 to Z2          | FSTRP- |

| 2              | Z3 to Z2          | FSTRP- | 2          | X1 to X2          | FSTRP+ |

| 3              | X3 to X2          | FSTRP+ | 3          | Y1 to Y2          | FSTDP+ |

| 4              | Y1 to Y2          | FSTDP+ |            |                   |        |

Note: Remove all existing jumpers when switching from one mode to another.

#### 2.1.2.1 E-Bus

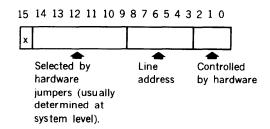

The DCM provides a standard interface to the 620-type I/O bus (see 620/f-100 Maintenance Manual 98 A 9908 150 for a description of the interface). Since the DCM generates the trap requests and interrupt requests, it must be assigned a position on the I/O priority line. The trap addressing for data is handled by software assignment, but the interrupt addresses, priority assignment, the device code, and the line-control-block addresses are determined by strapping.

#### 2.1.2.2 Multiplexor Bus

VTII-1754.4

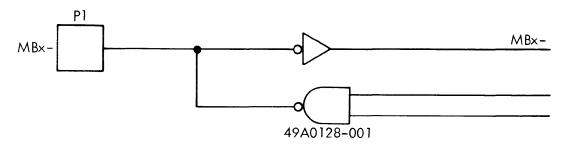

The MU interfaces with the LADs over a 38-line common bus comprising an eight-bit bidirectional bus (figure 2-3),

eight control lines, six bit-rate lines, twelve addressing lines, a clock line, two line-error lines, and a system-reset line (figure 2-1).

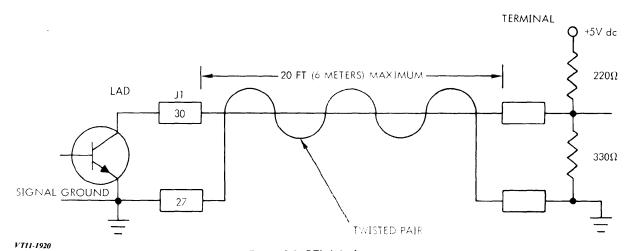

The LAD should present only one high-speed TTL load (2.0 milliamperes) to any of the MU output lines. Except for the bidirectional bus, which requires a 48-milliampere sink, all lines driven by the LAD are driven with open-collector gates capable of sinking 16 milliamperes in the low state.

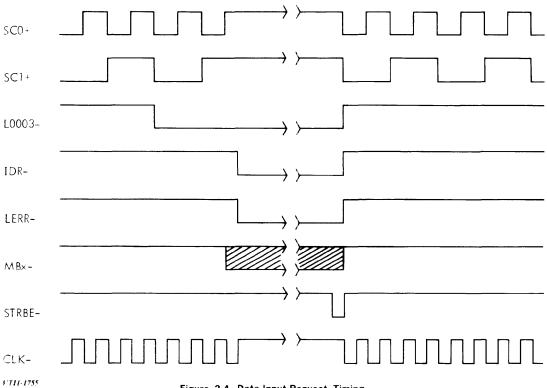

Figures 2-4, 2-5, and 2-6 show the relative timing for a data-input request, a status-input request, and a data-output request, respectively. Data are stable before the leading edge of the STRBE- pulse.

Figure 2-3. LAD Interface to the Eight-Bit Bidirectional Bus

Figure 2-4. Data-Input-Request Timing

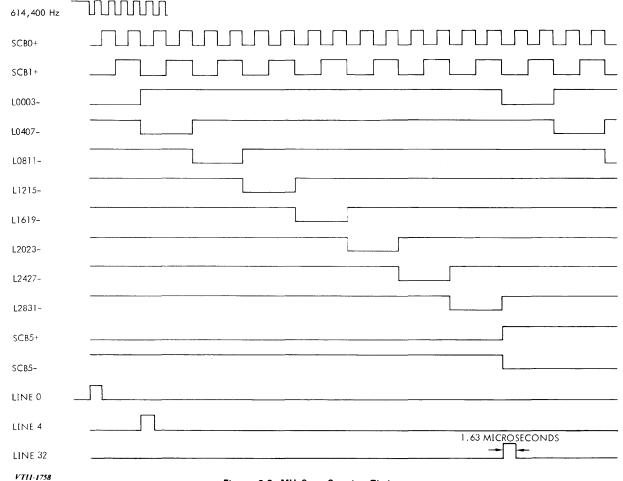

(SCB0- and SCB1-) and the most-significant output (SCB5+ and SCB5-). Each LAD receives one of the enabling terms (the actual term depends on what slot it occupies) SCB0-, SCB1-, SCB5+ or SCB5-. SCB5+ enables the LADs below line number 32 and SCB5-enables those above 31. SCB0- and SCB1- are decoded on the LAD for the individual line scanning.

The scan counter is clocked at 614,400 Hz (SCCLK+) as long as the control memory is in idle (CMB00- low). Once CMB00- goes high, SCLKE+ is held low, holding the scan counter at the line number being serviced.

The scan counter is loaded by LSC-. In normal operation, when the control memory is in idle, the scan counter is parallel-loaded with zeros each time it reaches a predetermined count. If the priority mode is selected, the scan counter is loaded with zeros after every other service request (SSCN+). During a control sequence the scan counter is also loaded with a line address over the programmed I/O. In this case, DTOA- enables LSC-, DTOA+ gates the six least-significant bits of the E-bus to the counter, and the counter is clocked at FSDRY+ time.

#### 2.2.4 Instruction Decoder (MU Board 2)

This block contains the data-transfer-out (DTO) and data-transfer-in (DTI) flip-flops for data-transfer control, as well as the gating for decoding the DCM external-control instructions.

The less-significant portion of the device address is decoded from EB01+, and EB02+ to obtain DVC0-through DVC7-. One of these signals is then jumpered to DVC05-. The more-significant portion is obtained by decoding EB03+, EB04+, and EB05+. The results of this are DVCE4- (device address 04x) and DVCE7- (device address 07x). Note that the decoded device-address is not enabled during IUAX+ or IUAF+. This prevents the DMA or interrupt address from being interpreted as an instruction. DVCDS- is gated with DVCE7- to form the DCM device-address 044 for common interrupt enable/disable instructions.

The programmed I/O data-transfer flip-flops are clocked by DVCFR+ (device address and FRYX+). If EB13+ or

Figure 2-8. MU Scan-Counter Timing

Figure 2-9. DCM Control Memory Word Format

| *Jump Address/F | Field D C B-                         | Field C I/O T R            | Field B               | Field A I                                                |  |

|-----------------|--------------------------------------|----------------------------|-----------------------|----------------------------------------------------------|--|

| 23 22 21 20 19  | 18 17 16 15 14                       | 13 12 11 10 9 8            | 7 6 5                 | 4 3 2 1 0                                                |  |

| 1 =             | ldle bit:                            | 0 = Not idle               | 1 =                   | Idle                                                     |  |

| R =             | Routine:                             | 0 = Output request routine | 1 =                   | Input request<br>routine (true<br>for entire<br>routine) |  |

| Τ =             | Trap:                                | 0 = No trap                | 1 =<br>(enab<br>B dec | les field-                                               |  |

| 1/0 =           | Input/Output<br>trap:                | 1 = Input trap             | trap (                | Output<br>valid for<br>ap instruc-                       |  |

| B =             | Enable B for status-change interrupt |                            |                       |                                                          |  |

| C =             | Free-running addre                   | ess clock (set to zero wh  | nen Field D           | is used)                                                 |  |

<sup>\*</sup> If Field C is all zeros, this field is used to control the ROM address counter clock (Field D).

| Field A | Description                          | Field C | Description               |

|---------|--------------------------------------|---------|---------------------------|

| 0000    |                                      | 0 0 0 0 |                           |

| 0001    | Stop scanner                         | 0 0 0 1 | Jump                      |

| 0 0 1 0 |                                      | 0 0 1 0 | Jump if byte count zero   |

| 0 0 1 1 | Start strobe                         | 0 1 0 0 | Jump if control character |

| 0 1 0 0 | Enable writing                       |         | detected                  |

| 0 1 0 1 | Disable writing                      | 1 0 0 0 | Jump if byte flag set     |

| 0 1 1 0 | Increment BA, decrement BC           |         | , , ,                     |

| 0 1 1 1 |                                      |         |                           |

| 1 0 0 0 | Input byte-count-zero interrupt      |         |                           |

| 1 0 0 1 | Output byte-count-zero interrupt     |         |                           |

| 1 0 1 0 | Line-error interrupt                 |         |                           |

| 1 0 1 1 | Status-change interrupt              |         |                           |

| 1 1 0 0 | Control-character-detected interrupt |         |                           |

| 1 1 0 1 | Control interrupt                    |         |                           |

| 1 1 1 0 |                                      |         |                           |

| 1 1 1 1 | Start interrupt                      |         |                           |

| Field B |   | В | DMA Transfer               | Field D       | Clock Address Counter If:   |

|---------|---|---|----------------------------|---------------|-----------------------------|

| 0       | 0 | 0 | Fetch/store byte count     | 0 0 0 0 0 0   |                             |

| 0       | 0 | 1 | Fetch/store buffer address | 000001        | DTO set                     |

| 0       | 1 | 0 | Fetch control character    | 000010        | DTO reset                   |

| 0       | 1 | 1 | Fetch key bits             | 0 0 0 0 1 0 0 | DTI set                     |

| 1       | 0 | 0 | Fetch/store data           | 0 0 0 1 0 0 0 | DTI reset                   |

| 1       | 0 | 1 | Fetch first byte (input)   | 0 0 1 0 0 0 0 | Trap/interrupt complete     |

| 1       | 1 | 0 | Fetch line-control byte    | 0 1 0 0 0 0 0 | No strobe (strobe complete) |

| 1       | 1 | 1 | Start trap                 |               |                             |

mode gates the switches TS0 through TS6 or pins 26 through 32 of J1 to the counter. The test mode also enables CACL- and causes CACCL+ to run free. The test mode enables the counter to be forced to any control-memory address using the switches or the J1 inputs (Note: all the switches must be opened to use the J1 inputs).

### 2.2.8 Control-Character Checking Logic (MU Board 1)

This block contains data-comparison logic. The 16-bit register/counter is loaded via DMA with a specific line's two control characters. The two control characters are then compared to the data character in the interface buffer. If the buffered character is one of the control characters, a control-character interrupt is generated.

### 2.2.9 Clock and Bit-Rate Generator (MU Board 1)

This block contains a crystal controlled 9.8304 MHz clock, a standard bit-rate generator and two variable bit-rate generators. The standard bit-rate generator provides the following rates:

$16 \times 9600 = 153,600 \text{ Hz}$

$16 \times 4800 = 76,800 \text{ Hz}$

$16 \times 2400 = 38,400 \text{ Hz}$

$16 \times 1200 = 19,200 \text{ Hz}$

$16 \times 600 = 9,600 \text{ Hz}$

$16 \times 300 = 4,800 \text{ Hz}$

$16 \times 150 = 2,400 \text{ Hz}$

$16 \times 75 = 1,200 \text{ Hz}$

Any of these rates can be jumpered (section 2.1.3) to any of six buffer gates, which in turn distribute the bit-rates to the LADs. The variable bit-rate generators provide the capability of dividing 9.8304, 4.9152, 2.4576, 1.2288, 0.6144, or 0.3072 MHz by an integer from 1 to 256 to give a rate (150 kHz maximum) that can be jumpered to any of the six buffer gates.

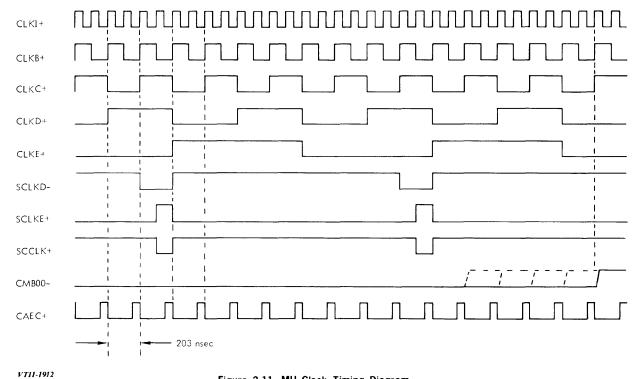

The crystal-controlled 9.8304 MHz oscillator produces a square wave (CLKI +), which is immediately divided down to produce CLKB +, the DCM main clock. It is divided down by a synchronous counter to produce CLKC +, CLKD +, and CLKE + (figure 2-11).

The standard bit rates are generated by simply continuing to count down  $\mathsf{CLKE} + .$

The odd-bit-rate counters consist of modulo-four synchronous counters. Counter 1 contains three modules and counter 2 contains two. The counters divide down the input frequency and count until they overflow. Upon overflow, they are loaded with the selected count and continue

Figure 2-11. MU Clock Timing Diagram

MULTIPLEXOR UNIT

the SMB bit is set in memory, the DCM hardware forces the most significant bit to one on all input data. If it is not set, the data are stored as they come from the line. The SMB + flip-flop is held reset unless CMB08 + is true. CMB08 + is true only during an input sequence.

The DMA 16-bit register/counter is a 16-bit ripple counter with parallel-loading capability. It is parallel-loaded during a DMA cycle. It holds the input or output buffer address during an input or output sequence, and also holds the control characters during the control-character check phase of an input sequence. During the control-character check, the output of the counter is compared with the multiplexor bus bits and the signal CCM— goes true if there is a match. The counter also contains logic for incrementing its contents. If the byte flag flip-flop is reset (BF— true), the counter is incremented by CLKCS+. This increments the buffer address before it is transferred back to processor memory if the second byte has been input or output.

An interrupt is initiated by FA17- which set flip-flop INTR+. INTR+ interrupt request) is then delayed by CLKB+ to allow the interrupt address to settle (INTDL-). Once INTDL- is set, the interrupt flip-flop (INT+) is set on the next IUCX- clock if the interrupts are enabled (EINT-). INT+ makes an interrupt request if the DCM has priority (PRMX+), and transfers the interrupt address onto the E-bus (INTA+ and INTB+) when the interrupt is acknowledged (IUAX+). INTA+ clears the interrupt request (INTR+ and INTDL-), and the INT+ flip-flop clears on the first IUCX- clock after the interrupt is complete.

# 2.3 MAINTENANCE

The following equipment is required to test the MU:

- Varian 620-series or V73 computer with at least 8K of memory

- b. An I/O expansion chassis for the DCM backplane(s)

- c. An I/O expansion power supply

- d. One card extender (44 D 0015-000 or 44 D 0540-000)

- e. Tektronix Type 547 or equivalent oscilloscope

- f. At least one asynchronous RS232 interface line adaptor (01 A 1470-000) with two test connectors (burndy edge connectors 57 A 0036-000) wired as follows:

| 1      | 1. | Pin 29 | to pin 35 | Data-terminal-ready to ring-indicator |

|--------|----|--------|-----------|---------------------------------------|

|        |    | Pin 35 | to pin 33 | Ring-indicator to dataset-ready       |

|        |    | Pin 29 | to pin 25 | Data-terminal-ready to carrier-on     |

| Line 0 | 2. | Pin 27 | to pin 37 | Request-to-send to clear-to-send      |

|        | 3. | Pin 31 | to pin 23 | Transmit-data to receive-data         |

|        | 4. | Pin 21 | to pin 18 | Control-out to control-in             |

|        | 5. | Pin 1 to pin 13  | Data-terminal-<br>ready to ring-<br>indicator     |

|--------|----|------------------|---------------------------------------------------|

|        |    | Pin 13 to pin 11 | Ring-indicator to                                 |

| Line 1 |    | Pin 1 to pin 7   | dataset-ready Data-terminal- ready to carrier- on |

|        | 6. | Pin 3 to pin 19  | Request-to-send to clear-to-send                  |

|        | 7. | Pin 5 to pin 9   | Transmit-data to                                  |

| l      | 8. | Pin 6 to pin 8   | Control-out to control-in                         |

The following additional jumpers can be added so the test connector can also be used on a synchronous RS232 interface LAD.

Pin 38 to pin 39 Pin 39 to pin 41 Pin 38 to pin 17 Pin 17 to pin 15

These jumpers tie the test clock to the receive/ transmit clock inputs.

When testing the MU, the asynchronous RS232 interface LAD lines should be set up for eight-bit data, two stop bits, no parity.

## g. Software tapes

MAINTAIN II Test Executive 92 U 0107-001 DCM Test Program 92 U 0106-009C

The following system configuration features must be checked before testing:

- Verify that the following features are jumpered according to special system specifications, if any, or to the standard configuration:

- Odd-bit-rate counters 1 and 2

- 2. The source for the six bit-rate (line-speed) signals

- 3. Scan length

- 4. Priority mode

- Device address

- 6. E-bus priority chain wiring

- 7. Base interrupt address

- 8. Base control table address (LCB)

- 9. High-speed or normal DMA selection

- b. If the system term shoe is located in the DCM, verify that +5V dc is wired to the term shoe slot on pins 118 and 121.

| Scan Length           | Mnemonic                             | Test Point                                       | Frequency                                         |

|-----------------------|--------------------------------------|--------------------------------------------------|---------------------------------------------------|

| 4,8,16,32,64          | SCB0-                                | P1 pin 97                                        | 307,200 Hz                                        |

| 4,8,16,32,64          | SCB1-                                | P1 pin 96                                        | 153,600 Hz                                        |

| 4,8,16,32<br>64       | SCB5-<br>SCB5-                       | P1 pin 99<br>P1 pin 99                           | High level<br>9,600 Hz                            |

| 4,8,16,32<br>64       | SCB5 +<br>SCB5 +                     | P1 pin 100<br>P1 pin 100                         | Low level<br>9,600 Hz                             |

| 4<br>8<br>16<br>32,64 | L0003-<br>L0003-<br>L0003-<br>L0003- | P1 pin 23<br>P1 pin 23<br>P1 pin 23<br>P1 pin 23 | 153,600 Hz<br>76,800 Hz<br>38,400 Hz<br>19,200 Hz |

| 8<br>16<br>32,64      | L0407-<br>L0407-<br>L0407-           | P1 pin 22<br>P1 pin 22<br>P1 pin 22              | 76,800 Hz<br>38,400 Hz<br>19,200 Hz               |

| 16<br>32,64           | L0811-<br>L0811-                     | P1 pin 21<br>P1 pin 21                           | 38,400 Hz<br>19,200 Hz                            |

| 16<br>32,64           | L1215-<br>L1215-                     | P1 pin 20<br>P1 pin 20                           | 38,400 Hz<br>19,200 Hz                            |

| 32,64                 | L1619-                               | P1 pin 27                                        | 19,200 Hz                                         |

| 32,64                 | L2023 <del>-</del>                   | P1 pin 26                                        | 19,200 Hz                                         |

| 32,64                 | L2427-                               | P1 pin 25                                        | 19,200 Hz                                         |

| 32,64                 | L2831-                               | P1 pin 24                                        | 19,200 Hz                                         |

Control-Memory Address Switches and Indicators: Ground J1 pin 25 or jumper pin X6 to X5 on MU board 1 and verify that the control memory address indicators (DS1 through DS7 on MU Board 1) can be turned on with the switches at location D10. When the side of the switch-rocker with the black dot is depressed, the switch is activated.

**Control-Memory Output:** Verify that the control-memory test-points at J1 (pins 1 through 24) are all high (except pins 24 and 8) when the DCM is in idle (control-memory address 000).

# 2.3.3 Suggested Methods

**DCM test program - Test 0:** Test 0 of the test program is a transmit-only test and is helpful in troubleshooting.

Sample program: The following program will be helpful in troubleshooting problems that cannot be found with the DCM test program. The program starts a transfer and at the end of the transfer (input or output byte-count zero), it initializes the DCM and begins again. If sense switch 3 is set, the program jumps back to the test executive at the completion of the transfer. Note that the output byte-count-zero interrupt occurs before the last two bytes have actually been transmitted, so these bytes are lost.

|         |         | Interrupt Traps |                                      |

|---------|---------|-----------------|--------------------------------------|

| 000060  | 002000  | JMPM            |                                      |

| 000061  | 000260  |                 |                                      |

| 000062  | 002000  | JMPM            |                                      |

| 000063  | 000260  |                 |                                      |

| 000064  | 001000  | JMP             |                                      |

| 000065  | 000270  |                 |                                      |

| 000066  | 001000  | JMP             |                                      |

| 000067  | 000271  |                 |                                      |

| 000070  | 001000  | JMP             |                                      |

| 000071  | 000272  |                 |                                      |

| 000072  | 002000  | JMPM            |                                      |

| 000073  | 000240  |                 |                                      |

| Address | Code    |                 |                                      |

| (Octal) | (Octal) | Instruction     | Remarks                              |

|         |         | Interrupt Halts |                                      |

| 000270  | 000004  |                 | Line error interrupt                 |

| 000271  | 000006  |                 | Status change interrupt              |

| 000272  | 000001  |                 | Control-character-detected interrupt |

$<sup>\</sup>mbox{\ensuremath{^{*}}}$  Change these instructions to reflect the correct device address if a nonstandard address is used.

# LCB Address

The LCB addresses for the line under test are entered here.

| Address | Code          | •                          |                               |

|---------|---------------|----------------------------|-------------------------------|

| (Octal) | (Octal)       | Instruction                | Remarks                       |

| 000500  | 017000        |                            | Input block-length address    |

| 000501  | 017001        |                            | Input buffer-address address  |

| 000502  | 017004        |                            | Output block-length address   |

| 000503  | 017005        |                            | Output buffer-address address |

| 000504  | 017006        |                            | Control-word address          |

|         | Lin           | e Control Block (Line zero |                               |

|         | sho           | own - base address 017000  | 0)                            |

| 017000  | 107770        |                            | Input block-length            |

| 017001  | 000600        |                            | Input buffer-address          |

| 017002  | 177777        |                            | Control characters            |

| 017003  | 000000        |                            | Spare                         |

| 017004  | 107770        |                            | Output block-length           |

| 017005  | 000650        |                            | Output buffer-address         |

| 017006  | 005500        |                            | Line control-word (includes   |

| 017007  | 000000        |                            | line address)                 |

| 017007  | 000000        |                            | Spare                         |

|         | Output Buffer |                            |                               |

| 000650  | 125252        |                            |                               |

| 000651  | 125252        |                            |                               |

| 000652  | 125252        |                            |                               |

| 000653  | 125252        |                            |                               |

|         |               |                            |                               |

Table 2-12. Output Sequence

| A | ODR | ESS | <u>S</u> |   |     |   | REMARKS                                                | 23 | 22  | 21   | 20    | 19     | 18  | 17 | 16 | 15 | 14 | 13  | 12   | 11 | 10  | 9 | 8 | 7  | 6    | 5 | 4_ | 3.   | 2   | 1_ | 0 |

|---|-----|-----|----------|---|-----|---|--------------------------------------------------------|----|-----|------|-------|--------|-----|----|----|----|----|-----|------|----|-----|---|---|----|------|---|----|------|-----|----|---|

| 6 | 5   | 4   | 3        | 2 | 1   | 0 |                                                        |    | Jum | p Ad | dress | /Field | d b |    | С  | В  |    | Fie | ld C |    | 1/0 | т | R | F  | ield | В |    | Fiel | d A |    | 1 |

| 0 | 0   | 0   | 0        | 0 | 0   | 1 | Stop scan; start trap; jump                            | 0  | 0   | 0    | 1     | 0      | 0   | 0  | 1  | 0  | 0  | 0   | 0    | 1  | 0   | 1 | 0 | 1  | 1    | 1 | 0  | 0    | 0   | 1  | 0 |

| 0 | 0   | 0   | 1        | 0 | 0   | 0 | Fetch byte count, enable write, wait for trap complete | 0  | 0   | 1    | 0     | 0      | 0   | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0   | 1 | 0 | 0  | 0    | 0 | 0  | 1    | 0   | 0  | 0 |

| 0 | 0   | 0   | 1        | 0 | 0   | 1 | Test byte count, start trap                            | o  | 0   | 1    | 0     | 1      | 1   | 0  | 1  | 0  | 0  | 0   | 1    | 0  | 0   | 1 | 0 | 1  | 1    | 1 | 0  | 0    | 0   | 0  | 0 |

| 0 | 0   | 0   | 1        | 0 | 1   | 0 | Fetch buffer address, wait for trap complete           | 0  | 0   | 1    | 0     | 0      | 0   | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0   | 1 | 0 | 0  | 0    | 1 | 0  | 0    | 0   | 0  | 0 |

| 0 | 0   | 0   | 1        | 0 | _1_ | 1 | Start trap                                             | 0  | 0   | 0    | 0     | 0      | 0   | 0  | 1_ | 0_ | 0  | 0   | 0    | 0  | 0   | 1 | 0 | 1_ | 11   | 1 | 0  | 0    | 0   | 0  | 0 |

| 0 | 0   | 0   | 1        | 1 | 0   | 0 | Fetch data, wait for trap complete                     | 0  | 0   | 1    | 0     | 0      | 0   | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0   | 1 | 0 | 1  | 0    | 0 | 0  | 0    | 0   | 0  | 0 |

| 0 | 0   | 0   | 1        | 1 | 0   | 1 | Start strobe                                           | 0  | 0   | 0    | 0     | 0      | 0   | 0  | 1  | 0  | 0  | 0   | 0    | 0  | 0   | 0 | 0 | 0  | 0    | 0 | 0  | 0    | 1   | 1  | 0 |

| 0 | 0   | 0   | 1        | 1 | 1_  | 0 | Start trap, test byte flag, inc.                       | 0  | 0   | 1    | 0     | 0      | 0   | 1  | 1  | 0  | 1  | 0   | 0    | 0  | _1  | 1 | 0 | 1  | 1    | 1 | 0  | _1_  | 1   | 0  | 0 |

| 0 | 0   | 0   | 1        | 1 | 1   | 1 | Store buffer address, wait for trap complete           | О  | 0   | 1    | 0     | 0      | 0   | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 1   | 1 | 0 | 0  | 0    | 1 | 0  | 0    | 0   | 0  | 0 |

| 0 | 0   | 1   | 0        | 0 | 0   | 0 | Start trap                                             | 0  | 0   | 0    | 0     | 0      | 0   | 0  | 1  | 0  | 0  | 0   | 0    | 0  | 1   | 1 | 0 | 1  | 1    | 1 | 0  | 0    | 0   | 0  | 0 |

| 0 | 0   | 1   | 0        | 0 | 0   | 1 | Store byte count, wait for trap complete               | 0  | 0   | 1    | 0     | 0      | 0   | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 1   | 1 | 0 | 0  | 0    | 0 | 0  | 0    | 0   | 0  | 0 |

| 0 | 0   | 1   | 0        | 0 | 1   | 0 | Test byte count zero                                   | 0  | 0   | 1    | 1     | 0      | 0   | 1  | 1  | 0  | 0  | 0   | 1    | 0  | 0   | 0 | 0 | 0  | 0    | 0 | О  | 0    | 0   | 0  | 0 |

| 0 | 0   | 1   | 0        | 0 | 1   | 1 | Wait for strobe complete                               | 0  | 1   | 0    | 0     | 0      | 0   | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0   | 0 | 0 | 0  | 0    | 0 | 0  | 0    | 0   | o  | 0 |

| 0 | 0   | 1   | 0        | 1 | 0   | 0 | Back to zero, disable write                            | 0  | 0   | 0    | 0     | 0      | 0   | 0  | 1  | 00 | 0  | 0   | 0    | 1  | 0   | 0 | 0 | 0  | 0    | 0 | 0  | 1    | 0   | 1  | 0 |

| 0 | 0   | 1   | 0        | 1 | 1   | 0 | Fetch line control byte, wait for trap complete        | 0  | 0   | 1    | 0     | 0      | 0   | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0   | 1 | 0 | 1  | 1    | 0 | 0  | 0    | 0   | 0  | 0 |

| 0 | 0   | 1   | 0        | 1 | 1   | 1 | Start strobe, jump                                     | 0  | 0   | 1    | 0     | 0      | 1   | 1  | 1  | 0  | 0  | 0   | 0    | 1  | 0   | 0 | 0 | 0  | 0    | 0 | 0  | 0    | 1   | 1  | 0 |

| 0 | 0   | 1   | 1        | 0 | 0   | 1 | Gen. int. (output byte-count zero)                     | 0  | 0   | 0    | 0     | 0      | 0   | 0  | 1  | 0  | 0  | 0   | 0    | 0  | 0   | 0 | 0 | 0  | 0    | 0 | 1  | 1    | 1   | 1  | 0 |

| 0 | 0   | 1   | 1        | 0 | 1   | 0 | Wait for DTO set                                       | 0  | 0   | 0    | 0     | 0      | 0   | 1  | 0  | 0  | 0  | 0   | 0    | 0  | 0   | 0 | 0 | 0  | 0    | 0 | 1_ | 0    | 0   | 1  | 0 |

| 0 | 0   | 1   | 1        | 0 | 1   | 1 | Wait for DTO reset                                     | О  | 0   | 0    | 0     | 0      | 1   | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0   | 0 | 0 | 0  | 0    | 0 | О  | 0    | 0   | 0  | 0 |

| 0 | 0   | 1   | 1        | 1 | 0   | 0 | Jump                                                   | o  | 0   | 1    | 0     | 0      | 1   | 1  | 1  | 0  | 0  | 0   | 0    | 1  | 0   | 0 | 0 | 0  | 0    | 0 | 0  | 0    | 1   | 1  | 0 |

| Α | DDF | RES | S | - |   |   | REMARKS                                   | 23 | 22  | 21   | 20     | 19     | 18  | 17 | 16 | 15  | 14 | 13  | 12    | 11 | 10  | 9 | 8 | 7_ | 6    | 5 | 4 | 3    | 2   | 1 0 |

|---|-----|-----|---|---|---|---|-------------------------------------------|----|-----|------|--------|--------|-----|----|----|-----|----|-----|-------|----|-----|---|---|----|------|---|---|------|-----|-----|

| 6 | 5   | 4   | 3 | 2 | 1 | 0 |                                           |    | Jui | mp A | ddress | s/Fiel | d D |    | С  | В   |    | Fie | eld C |    | 1/0 | Т | R | F  | ield | В |   | Fiel | d A | 1   |

| 0 | 0   | 0   | 0 | 0 | 1 | 1 | Stop scan; jump; enable B                 | 1  | 0   | 0    | 0      | 0      | 0   | 0  | 1  | 1   | 0  | 0   | 0     | 1  | 0   | 0 | 0 | 0  | 0    | 0 | 0 | 0    | 0   | 1 0 |

| 1 | 0   | 0   | 0 | 0 | 0 | 0 | Generate interrupt enable                 | 0  | 0   | 0    | 0      | 0      | 0   | 0  | 1  | 1   | 0  | 0   | 0     | 0  | 0   | 0 | 0 | 0  | 0    | 0 | 1 | 1    | 1   | 1 0 |

| 1 | 0   | 0   | 0 | 0 | 0 | 1 | Status change interrupt, wait for DTO set | 0  | 0   | 0    | 0      | 0      | 0   | 1  | 0  | 0   | 0  | 0   | 0     | 0  | 0   | 0 | 0 | 0  | 0    | 0 | 1 | 0    | 1   | 1 0 |

| 1 | 0   | 0   | 0 | 0 | 1 | 0 | Strobe                                    | 0  | 0   | 0    | 0      | 0      | 0   | 0  | 1  | 0   | 0  | 0   | 0     | 0  | 0   | 0 | 0 | 0  | 0    | 0 | 0 | 0    | 1   | 1 0 |

| 1 | 0   | 0   | 0 | 0 | 1 | 1 | Wait for strobe complete                  | 0  | 1   | 0    | 0      | 0      | 0   | 0  | 0  | o   | 0  | 0   | 0     | 0  | 0   | 0 | 0 | 0  | 0    | 0 | 0 | 0    | 0   | 0 0 |

| 1 | 0   | 0   | 0 | 1 | 0 | 0 | Wait for DTO reset; set write             | 0  | 0   | 0    | 0      | 0      | 1   | 0  | 0  | 0   | 0  | 0   | 0     | 0  | 0   | 0 | 0 | 0  | 0    | 0 | 0 | 1    | 0   | 0 0 |

| 1 | 0   | 0   | 0 | 1 | 0 | 1 | Strobe                                    | 0  | 0   | 0    | 0      | 0      | 0   | 0  | 1  | 0   | 0  | 0   | 0     | 0  | 0   | 0 | 0 | 0  | 0_   | 0 | 0 | 0    | 1   | 1 0 |

| 1 | 0   | 0   | 0 | 1 | 1 | 0 | Wait for strobe complete                  | 0  | 1   | 0    | 0      | 0      | 0   | 0  | 0  | 0 - | 0  | 0   | 0     | 0  | 0   | 0 | 0 | 0  | 0    | 0 | 0 | 0    | 0   | 0 0 |

| 1 | 0   | 0   | 0 | 1 | 1 | 1 | Jump to zero; disable write               | 0  | 0   | 0    | 0      | 0      | 0   | 0  | 1  | 0   | 0  | 0   | 0     | 1  | 0   | 0 | 0 | 0  | 0    | 0 | 0 | 1    | 0   | 1 0 |

Table 2-15. Processor Write Sequence

| Δ | DDF | RES | S_ |   |   |    | REMARKS                          | 23 | 22  | 21    | 20     | 19     | 18  | 17 | 16 | 15 | 14 | 13  | 12   | 11 | 10  | 9 | 8 | 7  | 6      | 5 | 4 | 3_  | 2 ′  | 0   |

|---|-----|-----|----|---|---|----|----------------------------------|----|-----|-------|--------|--------|-----|----|----|----|----|-----|------|----|-----|---|---|----|--------|---|---|-----|------|-----|

| 6 | 5   | 4   | 3  | 2 | 1 | 0  |                                  |    | Jur | np Ad | ddress | s/Fiel | d D |    | С  | -  |    | Fie | ld C |    | I/O | Т | R | Fi | ield E | 3 |   | Fie | ld A | 1   |

| 0 | 0   | 0   | 0  | 1 | 0 | 0  | Stop scan; jump                  | 1  | 0   | 0     | 1      | 0      | 0   | 0  | 1  | 0  | 0  | 0   | 0    | 1  | 0   | 0 | 0 | 0  | 0      | 0 | 0 | 0   | 0 1  | 0   |

| 1 | 0   | 0   | 1  | 0 | 0 | 0  | Generate interrupt               | 0  | 0   | 0     | 0_     | 0      | 0   | 0  | 1  | 0  | 0  | 0   | 0    | 0  | 0   | 0 | 0 | 0  | 0      | 0 | 1 | 1_  | 1_ 1 | 0   |

| 1 | 0   | 0   | 1  | 0 | 0 | 1  | Control int.; wait for DTO set   | 0  | 0   | 0     | 0      | 0      | 0   | 1  | 0  | 0  | 0  | 0   | 0    | 0  | 0   | 0 | 0 | 0  | 0      | 0 | 1 | 1   | 0 1  | 0   |

| 1 | 0   | 0   | 1  | 0 | 1 | 0  | Wait for DTO reset, enable write | 0  | 0   | 0     | 0      | 0      | 1   | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0   | 0 | 0 | 0  | 0      | 0 | 0 | 1   | 0 0  | 0 0 |

| 1 | 0   | 0   | 1  | 0 | 1 | 1_ | Start strobe                     | 0  | 0   | 0     | 0      | 0      | 0   | 0  | 1  | 0  | 0  | 0   | 0    | 0  | 0   | 0 | 0 | 0  | 0      | 0 | 0 | 0   | 1 ′  | ı o |

| 1 | 0   | 0   | 1  | 1 | 0 | 0  | Wait for strobe complete         | 0  | 1   | 0     | 0      | 0      | 0   | 0  | 0  | 0  | 0  | 0   | 0    | 0  | 0   | 0 | 0 | 0  | 0      | 0 | 0 | 0   | 0 (  | 0 0 |

| 1 | 0   | 0   | 1  | 1 | 0 | 1  | Disable write, jump to zero      | 0  | 0   | 0     | 0      | 0      | 0   | 0  | 1  | 0  | 0  | 0   | 0    | 1  | 0   | 0 | 0 | 0  | 0      | 0 | 0 | 1   | 0 1  | 0   |

Table 2-18. Control Memory Contents Table 2-18. Control Memory Contents (continued) **Address** 49A0194-007 49A0194-006 49A0194-005 Address 49A0194-010 49A0194-009 49A0194-008 **MSB** LSB MSB LSB

# Table 2-19. DCM Instructions

| Octal  | Mnemonic | Definition                               | Decription                                                                                                                                                    |

|--------|----------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100070 | EXC 070  | Initialize                               | Programmed system reset that clears the multiplexor and all associated LADs                                                                                   |

| 100170 | EXC 0170 | Clear control logic                      | Aborts current sequence and returns multiplexor to scanning mode, but does not disable interrupts                                                             |

| 100270 | EXC 0270 | Enable DCM interrupts                    | Enables the six DCM interrupts                                                                                                                                |

| 100470 | EXC 0470 | Disable DCM interrupts                   | Disables the six DCM interrupts                                                                                                                               |

| 100570 | EXC 0570 | Request control (write)                  | Permits computer to request use of multiplexor bus for LAD setup; the multiplexor generates a control interrupt upon completion of current operation          |

| 100670 | EXC 0670 | Request control (read)                   | Permits computer to request use of multiplexor bus for reading LAD status; the multiplexor generates a control interrupt upon completion of current operation |

| 100244 | EXC 0244 | Enable interrupts (common)               | DCM also responds to this general system interrupt-enabling instruction                                                                                       |

| 100444 | EXC 0444 | Disable interrupts (common)              | DCM also responds to this general system interrupt-disabling instruction                                                                                      |

| 102070 | IME 070  | Input data from DCM to memory            | Transfers a 16-bit character from the DCM, where the six                                                                                                      |

| 102170 | INA 070  | Input data from DCM to A register        | least-significant bits come<br>from the scan counter and the<br>remainder from the interface<br>buffer                                                        |

| 102270 | INB 070  | Input data from DCM to B register        | buller                                                                                                                                                        |

| 102570 | CIA 070  | Clear A register and input data from DCM | Clears destination register,<br>then transfers a 16-bit character                                                                                             |

| 102670 | CIB 070  | Clear B register and input data from DCM | from the DCM, where the six least-significant bits come from the scan counter and the remainder from the interface buffer                                     |

| 103170 | OAR 070  | Output data from A register to DCM       | Transfers a 16-bit character to the DCM, where the six least-                                                                                                 |

| 103270 | OBR 070  | Output data from B register to DCM       | significant bits go to the scan counter and the remainder to the interface buffer                                                                             |

| 103370 | OME 070  | Output data from memory to DCM           |                                                                                                                                                               |

### 2.4.2.6 Control

This interrupt is explained in section 2.4.4.4 on DCM programming sequences.

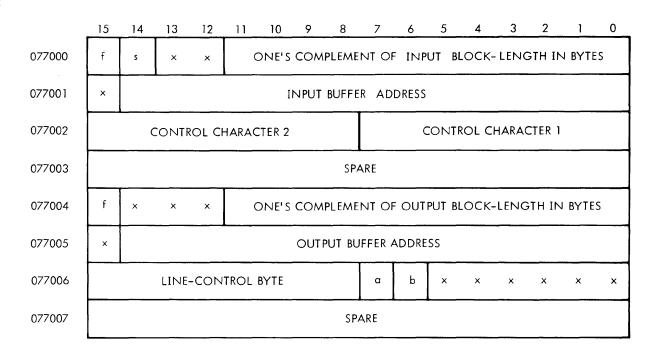

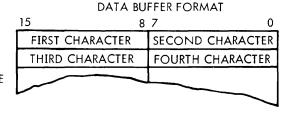

## 2.4.3 DCM DMA Control Table

The DCM works from line control tables (figure 2·13) stored in computer memory for all DMA operations. Each line control table uses eight memory locations. Thus, for a maximum 64-line system, 512 memory locations are allocated for the DCM.

The byte-transfer flag in the control table is hardware-set and determines which byte is to be transferred. The initial

x = UNUSED

f = BYTE-TRANSFER FLAG

O FOR LOWER EIGHT BITS

I FOR UPPER EIGHT BITS

ab = CODE FOR LINE-CONTROL BYTE

s = FORCES MSB BIT (8TH BIT) OF INPUT BYTE TO ONE

NOTE: ADDRESSES SHOWN ARE FOR LINE ZERO

WITH THE SIX MOST-SIGNIFICANT BITS

ALL STRAPPED ON

VTII-1759 A

Figure 2-13. Line Control Table

byte flag is reset. If the flag is not set, it is now set and the characters stored in memory with the new character in the less-significant byte position. After the character is stored, the byte count is decremented and restored in memory.

If the byte flag was set, the input buffer address word is incremented and the new address stored in memory. After the input character is stored in the input buffer and all the housekeeping completed, the two control characters are input to the multiplexor and compared to the input character. If there is a match, a control-character-detected interrupt is generated. Upon completion of the control-character check, the multiplexor checks to see if the byte count went to zero during this input sequence. If the byte

count is zero, an input byte-count-zero interrupt is generated. The byte-count check completes the input sequence, and scanning is resumed.

If there is an input request from a line whose byte count is already zero, the multiplexor clears the request and continues scanning (unless a line error is present, in which case the line error is reported).

**Note:** The DCM clears the less-significant byte whenever it loads data in the more-significant byte of a buffer word.

VTII-1761

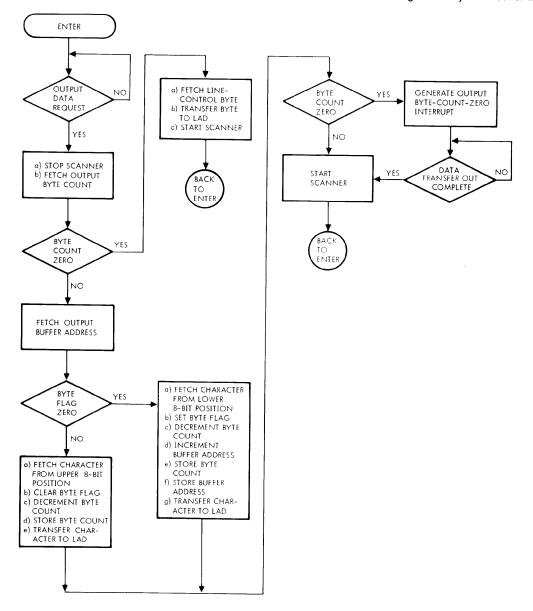

Figure 2-15. DCM Output Sequence

| line and resi<br>waits for the | data-transfer-out and then loads the indicated<br>umes scanning. For reading, the multiplexor<br>data-transfer-out that identifies the line and | CCLG-                      | Clear-control-logic signal from MU board 2                                                                       |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------|

| data and wa                    | be transferred, then fetches the appropriate its for the data-transfer-in. At the end of the anning resumes.                                    | CCM +                      | Control-character-match signal from MU board 2                                                                   |

| sequence, co                   | nultiplexor stops scanning during a control introl operations should be as fast as possible ne overruns and consequent data loss.               | CLK-                       | Clock for the LADs (nominally 614,400 Hz) (LADs place requests on line on the positive going edge of this clock) |

|                                | rol sequences are given in this manual in the g subsections of each LAD section.                                                                | CLKB+<br>CLKBF+            | 4.9152 MHz clock (square wave)                                                                                   |

|                                |                                                                                                                                                 | CLKC+                      | 2.4576 MHz clock (square wave)                                                                                   |

| 2.5 MNEN                       | MONICS                                                                                                                                          | CLKD+                      | 1.2288 MHz clock (square wave)                                                                                   |

| MU Board Or                    | ne                                                                                                                                              | CLKE +                     | 614,400 Hz clock (square wave)                                                                                   |

| Mnemonic                       | Definition                                                                                                                                      | CLKF+                      | 307,200 Hz clock (square wave)                                                                                   |

| A-                             | Decoded along with B- to indicate the type of information being                                                                                 | CLKI+                      | Fundamental clock frequency 9.8304 MHz                                                                           |

|                                | transferred to the LAD.                                                                                                                         | CMA00 +<br>thru            | Outputs of the control memory address counter                                                                    |

| AC+                            | Source for A- from the inter-<br>face buffer                                                                                                    | CMA06 +                    | Counts                                                                                                           |

| AC10+<br>thru<br>AC16+         | Parallel inputs to the control memory address counter                                                                                           | CMB00 +<br>thru<br>CMB23 + | Outputs of the control memory                                                                                    |

| AD+                            | A input to the interface buffer (EB07 +)                                                                                                        | CME00-                     | Enable control memory addresses 000 to 037                                                                       |

| B                              | See A-                                                                                                                                          | CME32-                     | Enable control memory addresses 040 to 077                                                                       |

| BC +                           | Source of B- from the inter-<br>face buffer                                                                                                     | CME64                      | Enable control memory addresses 0100 to 0137                                                                     |

| BD+                            | B input to the interface buffer (EB06+)                                                                                                         | CPURA +                    | CPU read control request from MU board 2                                                                         |

| BFA +                          | Byte flag (buffered) from MU board 2                                                                                                            | CPURS+                     | CPUR4 + synchronized with CLKB +                                                                                 |