varian data machines /a varian subsidiary

VARIAN 70 SERIES

PROCESSOR MANUAL

# VARIAN 70 SERIES PROCESSOR MANUAL

Specifications are subject to change without notice. Address comments regarding this document to Varian Data Machines, Publications Department, 2722 Michelson Drive, Irvine, California, 92664.

See the addendum at the back of this manual.

varian data machines/a varian subsidiary 2722 michelson drive/irvine, california 92664 © 1974 printed in USA 98 A 9906 023

**JULY 1974**

EN 82781

## **SECTION 4 THEORY OF OPERATION**

| 4.1 GENERAL                              |      |

|------------------------------------------|------|

| 4.2 FUNCTIONAL DESCRIPTION               |      |

| 4.2.1 Central Control                    |      |

| 4.2.2 Data Loop                          |      |

| 4.2.3 Memory Control                     |      |

| 4.2.4 I/O Data Loop                      |      |

| 4.2.5 I/O Control                        |      |

| 4.3 CENTRAL CONTROL CIRCUITS             |      |

| 4.3.1 Instruction Register               |      |

| 4.3.2 Instruction Field Selector         |      |

| 4.3.3 Instruction Decoder                |      |

| 4.3.4 Instruction Decoding Logic         |      |

| 4.3.5 Address Control                    |      |

| 4.3.6 Address Selector                   |      |

| 4.3.7 Control Store                      |      |

| 4.3.8 Buffer Control                     |      |

| 4.3.9 Register Field Selector            |      |

| 4.3.10 Control Store Buffer (Bits 32-63) |      |

| 4.3.11 Control Field Decoder             |      |

| 4.3.12 Memory, I/O, and Clock Control    |      |

| 4.3.13 Reset Logic                       |      |

| 4.3.14 Interrupt Logic                   |      |

| 4.3.15 Supervisor Control and Clocks     |      |

| 4.3.16 Execution Control.                |      |

| 4.4 DATA LOOP CIRCUITS                   |      |

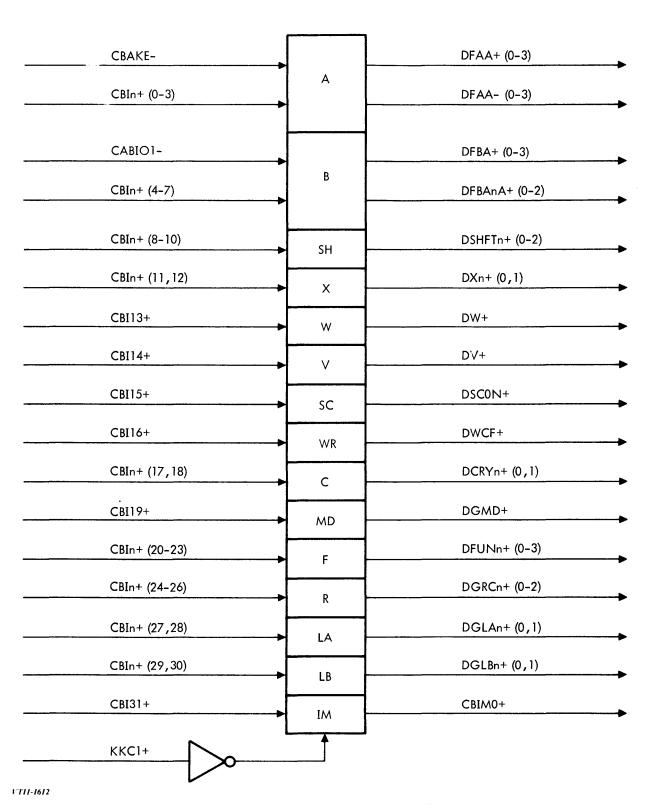

| 4.4.1 Control Store Buffer (Bits 0-31)   | 4 16 |

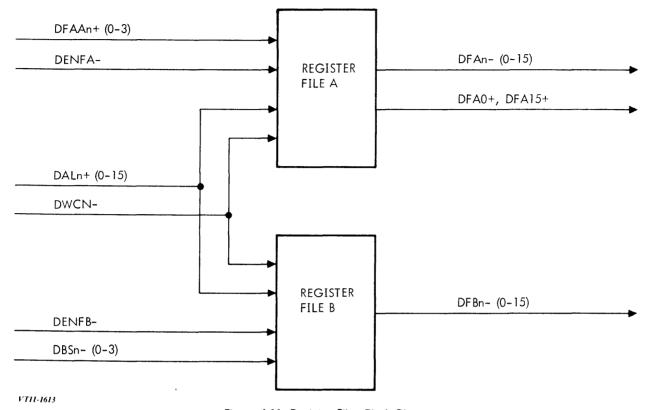

| 4.4.2 Register Files A and B             |      |

| 4.4.3 File Control                       |      |

| 4.4.4 Latch A Control                    |      |

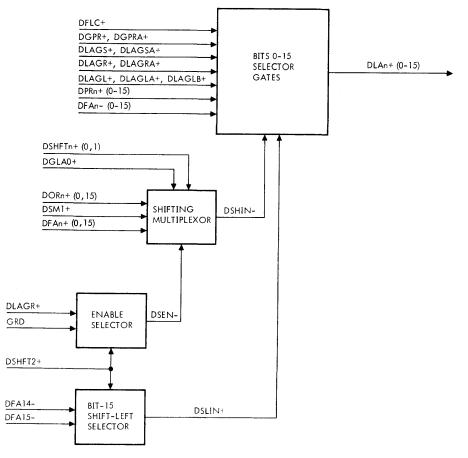

| 4.4.5 Latch A                            |      |

| 4.4.6 Latch B Control                    |      |

| 4.4.7 Latch B                            |      |

| 4.4.8 B Multiplexor                      |      |

| 4.4.9 Arithmetic and Logic Unit          |      |

| 4.4.10 ALU Control                       |      |

| 4.4.11 Register Control                  |      |

| 4.4.12 Shift Control                     |      |

| 4.4.13 Operand Control                   |      |

| 4.4.14 Operand Register                  | 4-29 |

| 4.4.15 Key Register                      | 4.29 |

| 4.4.16 Program Counter                   |      |

| 4.4.17 Shift Counter                     |      |

| 4.4.18 Status and Test Logic             |      |

| 4.5 MEMORY CONTROL CIRCUITS              |      |

| 4.5.1 Address Multiplexor                |      |

| 4.5.2 Address Latch                      |      |

| 4.5.3 Address Drivers                    |      |

| 4.5.4 Address Comparator                 |      |

| 4.5.5 Data Multiplexor                   |      |

| 4.5.6 Data Drivers                       |      |

| 4.5.7 I/O Latch                          |      |

| 4.5.8 Input Latch                        | 4-3  |

# TABLE OF CONTENTS

## **SECTION 1 GENERAL DESCRIPTION**

## **SECTION 2 INSTALLATION**

| 2.1 INSPECTION                                                | 2 · 1 |

|---------------------------------------------------------------|-------|

| 2.2 PHYSICAL DESCRIPTION                                      | 2-1   |

| 2.3 INTERCONNECTION                                           | 2.1   |

|                                                               |       |

| SECTION 3 OPERATION                                           |       |

|                                                               |       |

| 3.1 SWITCHES AND INDICATORS                                   | 3.    |

| 3.1.1 POWER Switch                                            |       |

| 3.1.2 STEP/RUN Switch and STEP and RUN Indicators             |       |

| 3.1.3 START Switch                                            |       |

| 3.1.4 BOOT Switch                                             |       |

| 3.1.5 Register-Entry Switches and Register-Display Indicators |       |

|                                                               |       |

| 3.1.6 DISPL CLR Switch                                        |       |

| 3.1.7 DISPLAY SELECT Switches and Indicators                  |       |

| 3.1.7.1 MEM Switch                                            |       |

| 3.1.7.2 STATUS Switch                                         |       |

| 3.1.7.3   Switch                                              |       |

| 3.1.7.4 P Switch                                              |       |

| 3.1.7.5 REG Switch                                            |       |

| 3.1.8 DISPL and ENTER Switches                                |       |

| 3.1.9 REG SELECT Switches and Indicators                      |       |

| 3.1.10 CLEAR and INCR Switches                                |       |

| 3.1.11 INT Switch                                             |       |

| 3.1.12 RESET Switch                                           |       |

| 3.1.13 SENSE Switches and Indicators                          |       |

| 3.1.14 BOOT SELECT Switch                                     |       |

| 3.2 MANUAL OPERATIONS                                         |       |

| 3.2.1 Displaying Register Contents                            |       |

| 3.2.2 Displaying Memory Contents                              |       |

| 3.2.3 Displaying Overflow Status                              |       |

| 3.2.4 Entering Data in Memory                                 | 3-5   |

| 3.2.5 Entering Data in a Register                             | 3-0   |

| 3.3 PROGRAM EXECUTION                                         | 3.6   |

| 3.3.1 Power On                                                | 3-6   |

| 3.3.2 Loading the Bootstrap Program                           | 3-6   |

| 3.3.3 Executing a Stored Program                              | 3-8   |

|                                                               |       |

# SECTION 4 THEORY OF OPERATION (continued)

| 4.9.3 Field-Selection Addressing                       | 4.72  |

|--------------------------------------------------------|-------|

| 4.9.4 Conditional-Test Addressing                      |       |

| 4.9.5 Interrupt Addressing                             |       |

| 4.9.6 Decoding Addressing                              | 4.75  |

| 4.10 CONTROL-PANEL CIRCUITS                            | 4-79  |

| 4.10.1 File Address Register                           | 4.79  |

| 4.10.2 Toggle Register                                 | 4- 79 |

| 4.10.3 Clock Generator                                 |       |

| 4.10.4 Run-Mode Control                                |       |

| 4.10.5 Interrupt Control                               |       |

| 4.10.6 Blink Oscillator                                |       |

| 4.10.7 Input Encoder and I/O Bus Drivers               |       |

| 4.10.8 I/O Control Buffer                              |       |

| 4.10.9 Display Register                                |       |

| 4.10.10 Display-Selection Register                     | 4.84  |

| 4.10.11 Pulse Register                                 | 4-84  |

| 4.10.12 Data-Display Drivers and Light-Emitting Diodes | 4-84  |

| 4.10.13 Switches, Debounce and Pull-Up Circuits        |       |

| 4.10.14 I/O Bus Terminators                            |       |

| 4.11 Microprogramming Examples                         |       |

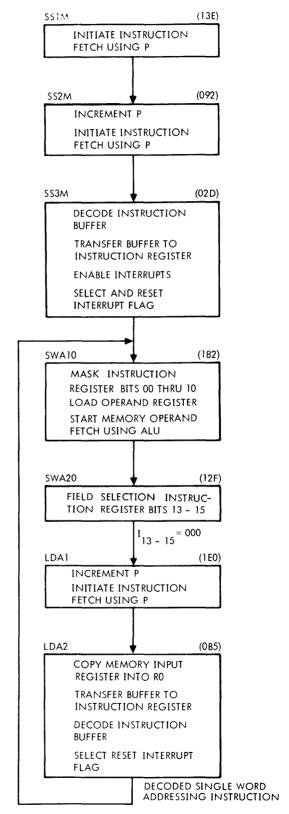

| 4.11.1 LDA Instruction                                 |       |

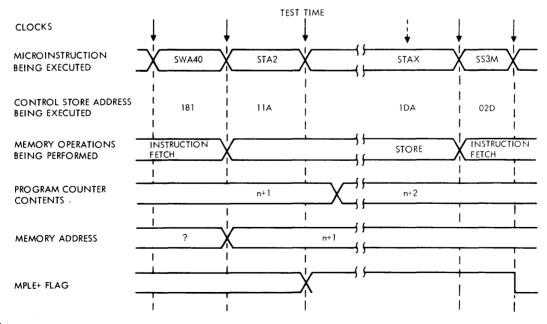

| 4.11.2 STA Instruction                                 | 4-00  |

| COTION C MAINTENANCE                                   |       |

| SECTION 5 MAINTENANCE 5.1 TEST EQUIPMENT               |       |

| 5.1 TEST EQUIPMENT                                     | 5 1   |

| 5.1 TEST EQUIPMENT                                     | 5 1   |

| 5.1 TEST EQUIPMENT                                     | 5 1   |

| 5.1 TEST EQUIPMENT                                     | 5 I   |

| 5.1 TEST EQUIPMENT                                     | 5 I   |

| 5.1 TEST EQUIPMENT                                     |       |

# SECTION 4 THEORY OF OPERATION (continued)

| 4.5.9 Instruction Buffer                                     | 4-32                                  |

|--------------------------------------------------------------|---------------------------------------|

| 4.5.10 Writing Drivers                                       | 4-32                                  |

| 4.5.11 Key Logic                                             | 4-32                                  |

| 4.5.12 Clock Generator                                       |                                       |

| 4.5.13 Control Sequencer                                     |                                       |

| 4.5.14 Priority Logic                                        |                                       |

| 4.5.15 Control Logic 1                                       |                                       |

| 4.5.16 Control Logic 2                                       |                                       |

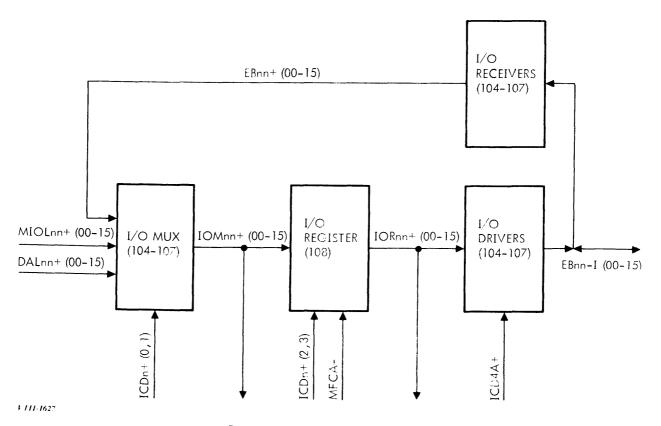

| 4.6 I/O DATA LOOP                                            |                                       |

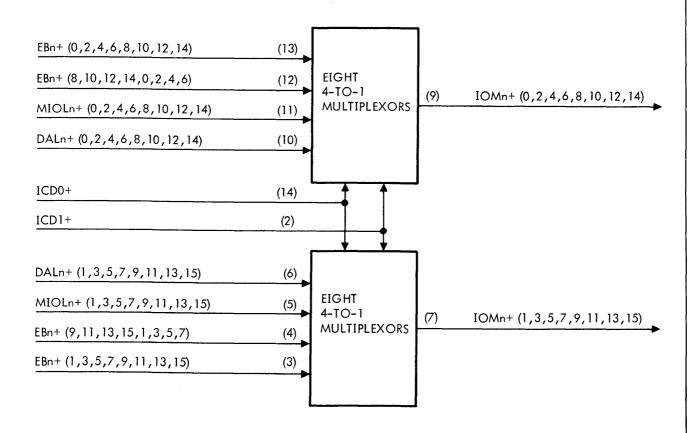

| 4.6.1 I/O Multiplexor                                        | 4-36                                  |

| 4.6.2 I/O Register                                           |                                       |

| 4.6.3 I/O Drivers and Receivers                              |                                       |

| 4.7 I/O CONTROL                                              | 4-37                                  |

| 4.7.1 Microinstruction Sequencing                            |                                       |

| 4.7.1.1 Address Selector                                     |                                       |

| 4.7.1.2 Address Counter                                      |                                       |

| 4.7.1.3 I/O Control Store                                    |                                       |

| 4.7.1.4 Buffer                                               |                                       |

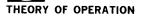

| 4.7.2 Decoding and Sequencing Control                        |                                       |

| 4.7.2.1 Address-Counter Loading Control                      |                                       |

| 4.7.2.2 Address Selector Control                             |                                       |

| 4.7.2.3 Clock Inhibitor                                      |                                       |

| 4.7.2.4 I/O Function Decoder                                 |                                       |

| 4.7.2.5 Inhibit-Idle Control                                 |                                       |

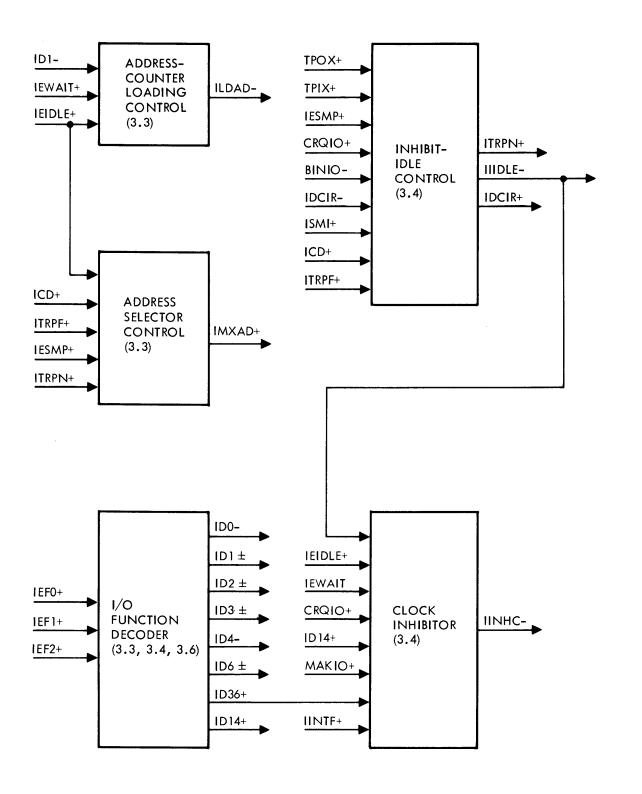

| 4.7.3 Interrupt and DMA Control                              |                                       |

| 4.7.3.1 Interrupt Clock Generator                            |                                       |

| 4.7.3.2 Sample Control Logic                                 |                                       |

| 4.7.3.3 Interrupt Acknowledgment Control                     |                                       |

| 4.7.3.4 Interrupt Flip-Flop                                  |                                       |

| 4.7.3.5 Interrupt Clock Inhibitor                            |                                       |

| 4.7.3.6 DMA Acknowledgment Control                           |                                       |

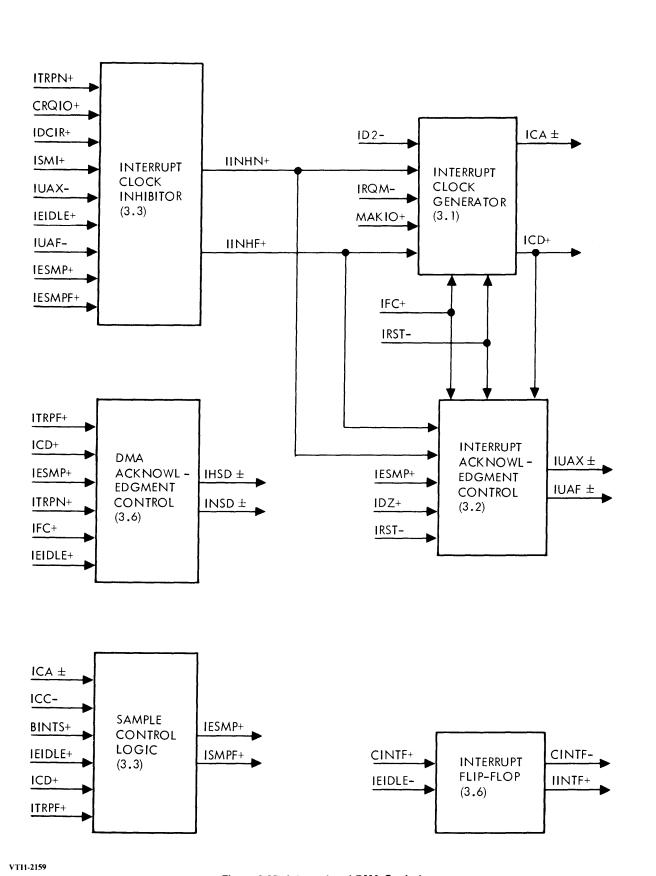

| 4.7.4 I/O Data-Loop Control                                  |                                       |

| 4.7.5 Processor-I/O Control                                  |                                       |

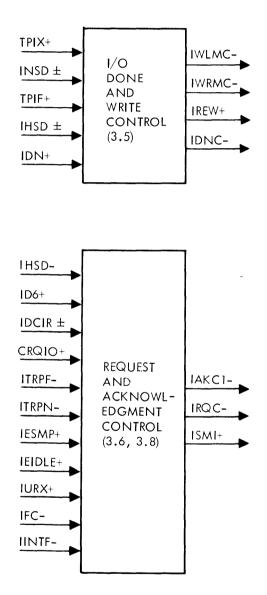

| 4.7.5.1 I/O Done and Write Control                           |                                       |

| 4.7.5.2 Request and Acknowledgment Control                   |                                       |

| 4.7.5.3 Miscellaneous Control                                |                                       |

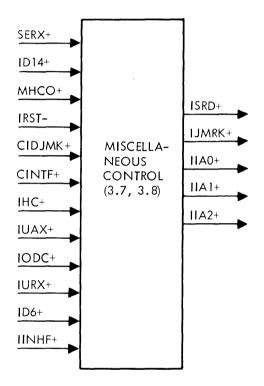

| 4.7.6 Drivers/Receivers and Miscellaneous Control            |                                       |

| 4.7.6.1 Drivers/Receivers                                    |                                       |

| 4.7.6.2 Buffers and Decoder                                  |                                       |

| 4.7.6.3 Function and Data Ready Control                      |                                       |

| 4.7.6.4 Memory Time-Out                                      |                                       |

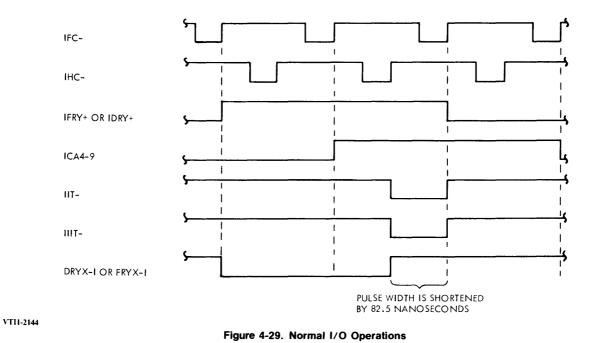

| 4.7.7 Programmed I/O Operation                               |                                       |

| 4.7.7 Programmed 1/O Operation                               |                                       |

| 4.7.9 Normal DMA Operations                                  |                                       |

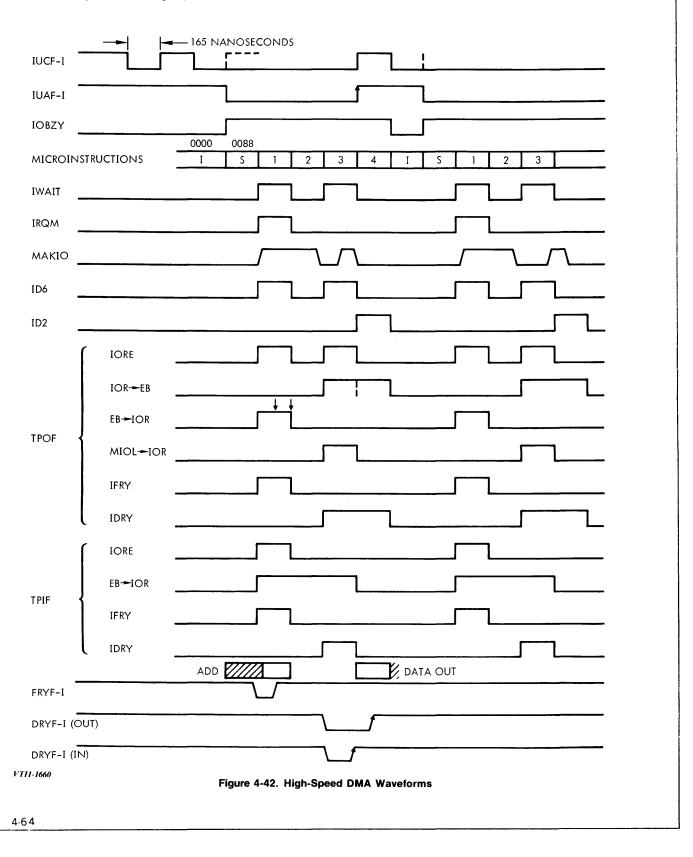

| 4.7.9 Normal DMA Operations 4.7.10 High-Speed DMA Operations |                                       |

| 4.7.10 High-Speed DMA Operations                             |                                       |

| 4.9 CONTROL-STORE ADDRESSING                                 |                                       |

| 4.9.1 Normal Addressing                                      |                                       |

| 4.9.1 Normal Addressing                                      | 4.72                                  |

| A 4 / INDITION 1.5 FIRID ACCITESSING                         | , , , , , , , , , , , , , , , , , , , |

# LIST OF ILLUSTRATIONS (continued)

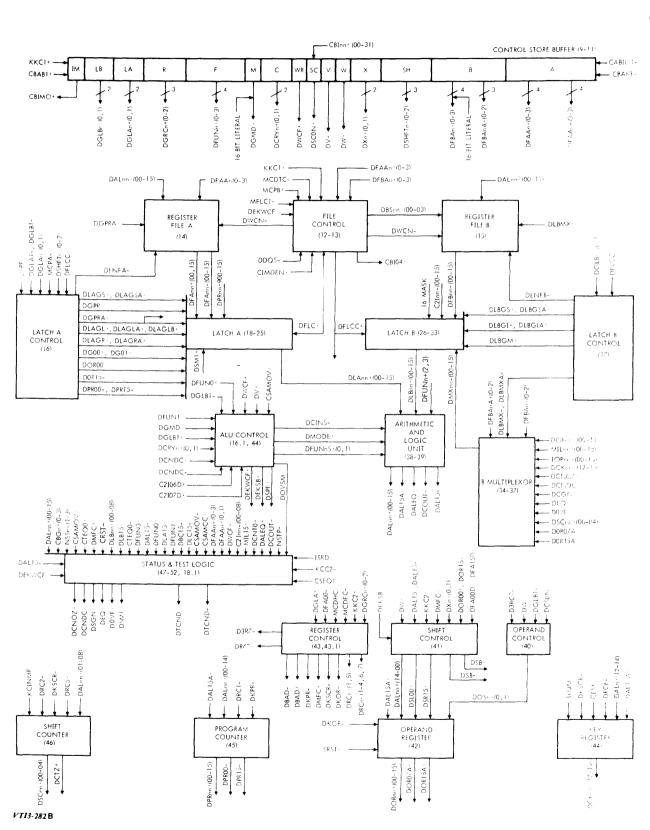

| Figure 4- | 9. Data Loop Block Diagram                      | 4-17 |

|-----------|-------------------------------------------------|------|

| Figure 4  | 10. Control Store Buffer (Bits 0-31)            | 4-18 |

| Figure 4- | 11. Register Files Block Diagram                | 4-19 |

| Figure 4  | 12. Latch A Block Diagram                       | 4-20 |

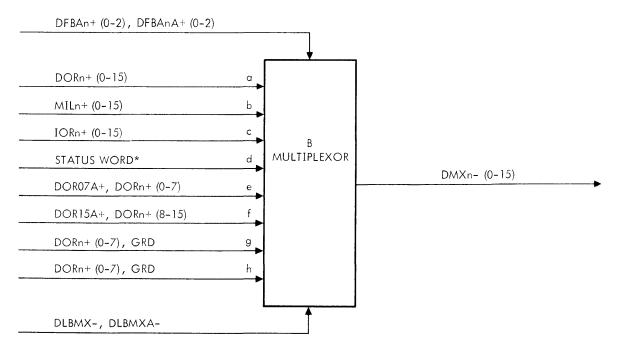

| Figure 4  | 13. B-Multiplexor Block Diagram                 | 4-23 |

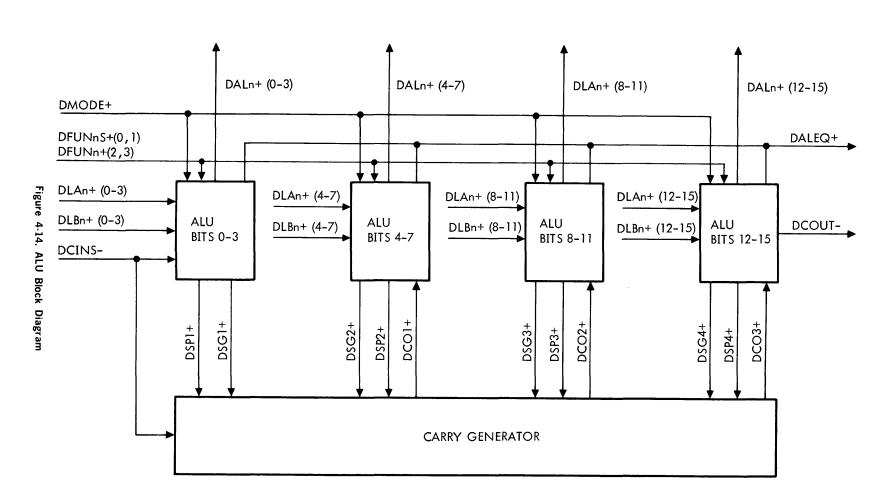

| Figure 4- | 14. ALU Block Diagram                           | 4-24 |

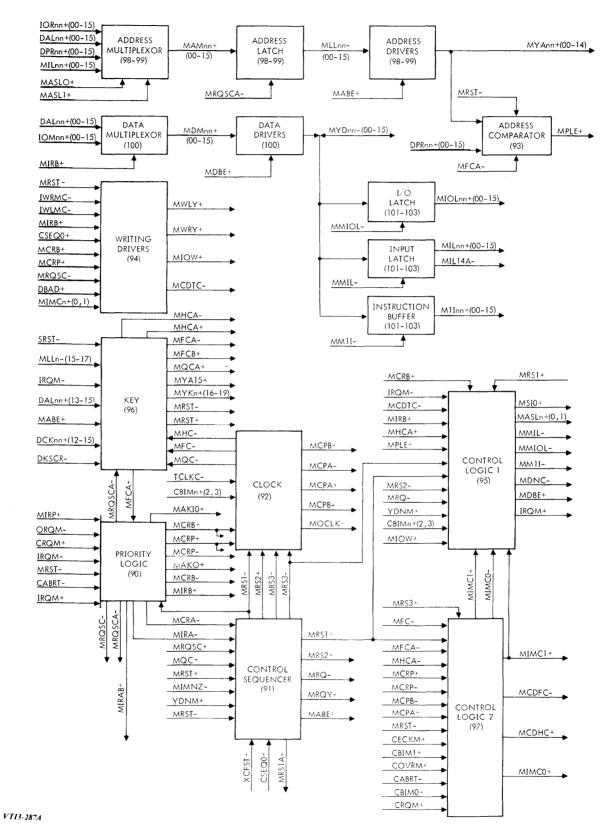

| Figure 4  | 15. Memory Control Block Diagram                | 4-31 |

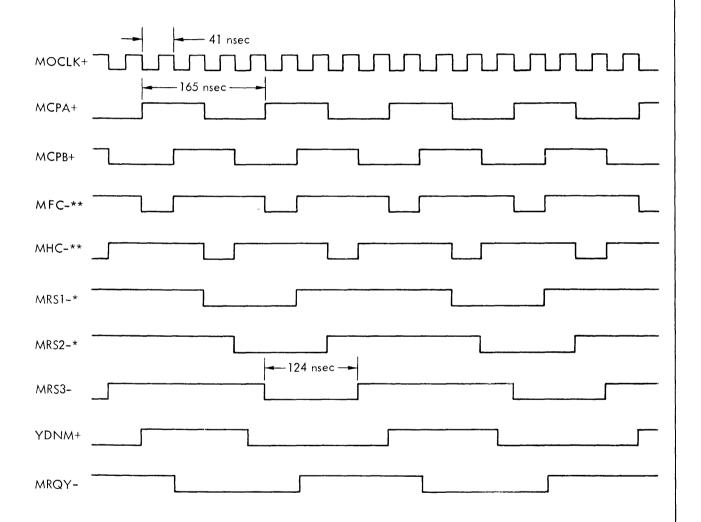

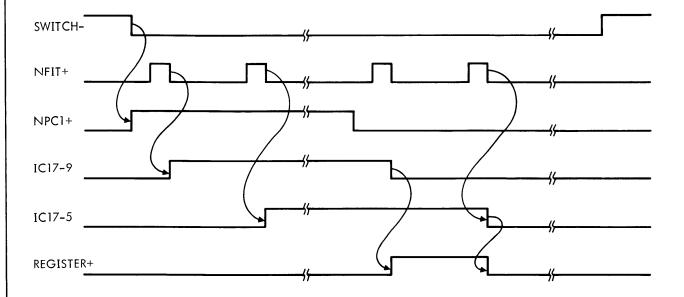

| Figure 4  | 16. Clock and Sequencer Waveforms               | 4-33 |

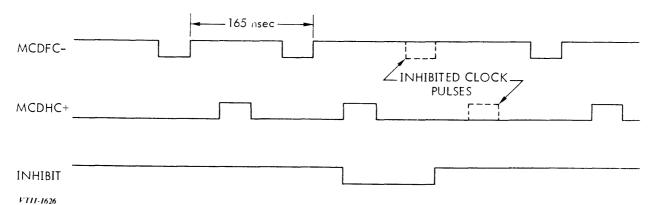

| Figure 4  | 17. Processor Clock Inhibiting                  | 4-35 |

|           | 18. I/O Data Loop Block Diagram                 |      |

|           | 19. I/O Multiplexor Block Diagram               |      |

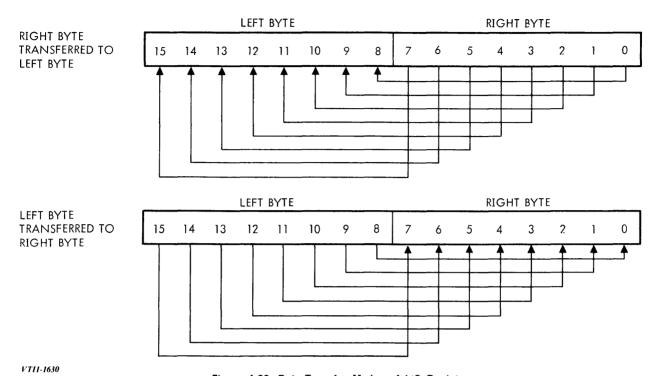

|           | 20. Byte Transfer Modes of I/O Register         |      |

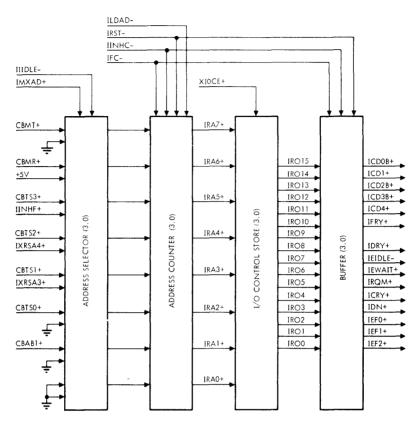

|           | 21. Microinstruction-Sequencing Circuits        |      |

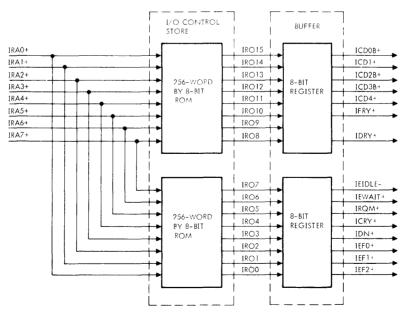

|           | 22. I/O Control Store and Buffer Block Diagram  |      |

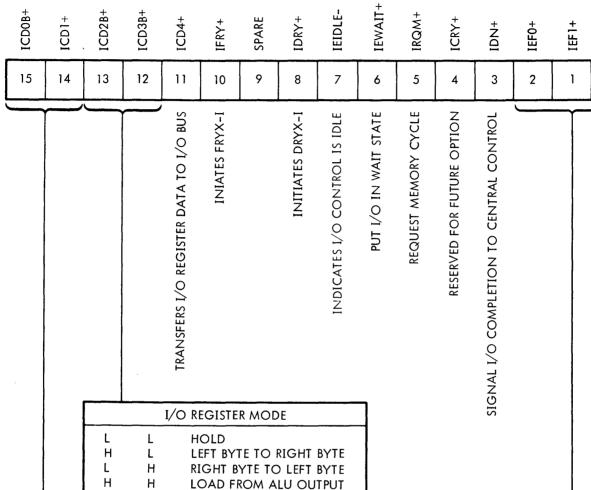

|           | 23. I/O Control-Store Word Format               |      |

|           | 24. Decoding and Sequencing Control             |      |

|           | 25. Interrupt and DMA Control                   |      |

|           | 26. I/O Data Loop Control                       |      |

|           | 27. Processor I/O Control                       |      |

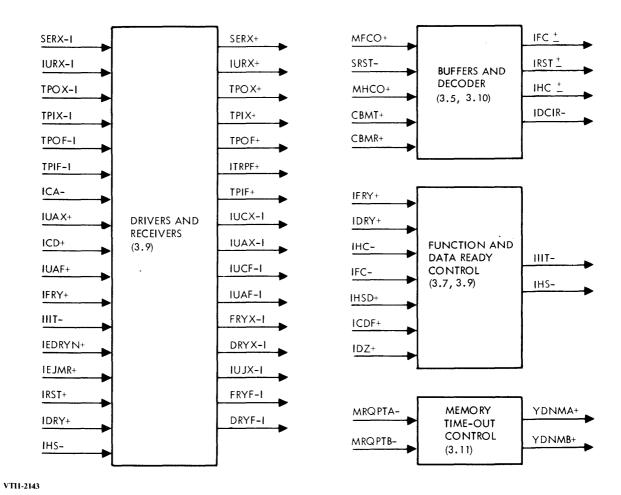

|           | 28. Drivers/Receivers and Miscellaneous Control |      |

|           | 29. Normal I/O Operations                       |      |

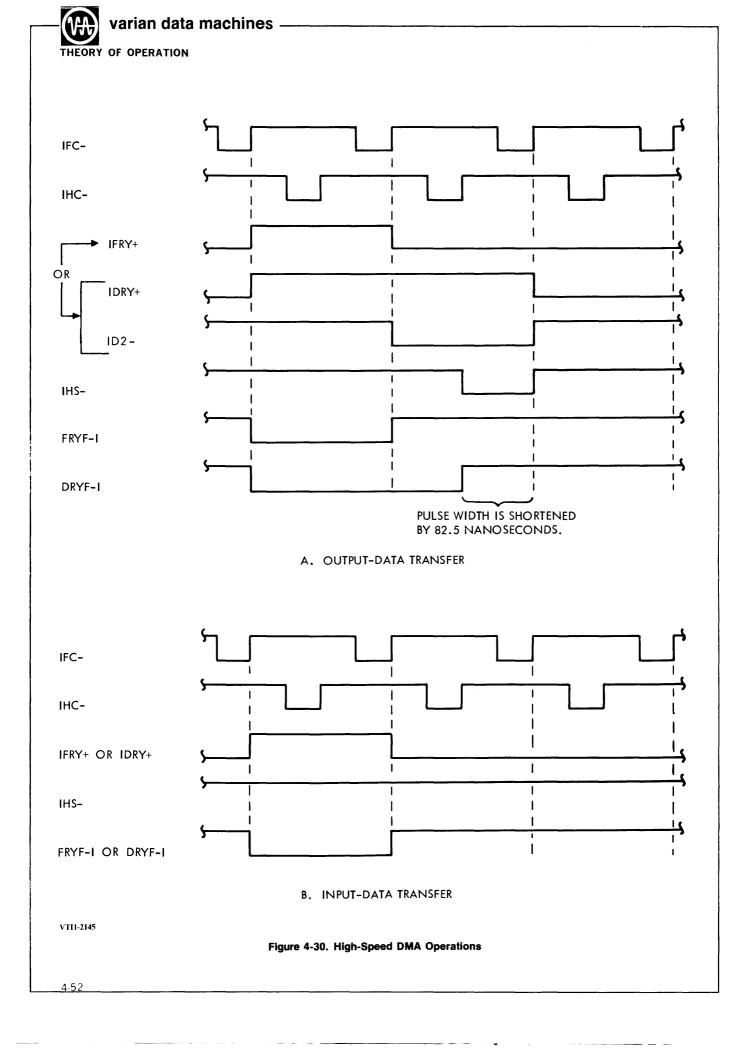

|           | 30. High-Speed DMA Operations                   |      |

|           | 31. Memory Time-Out Waveforms                   |      |

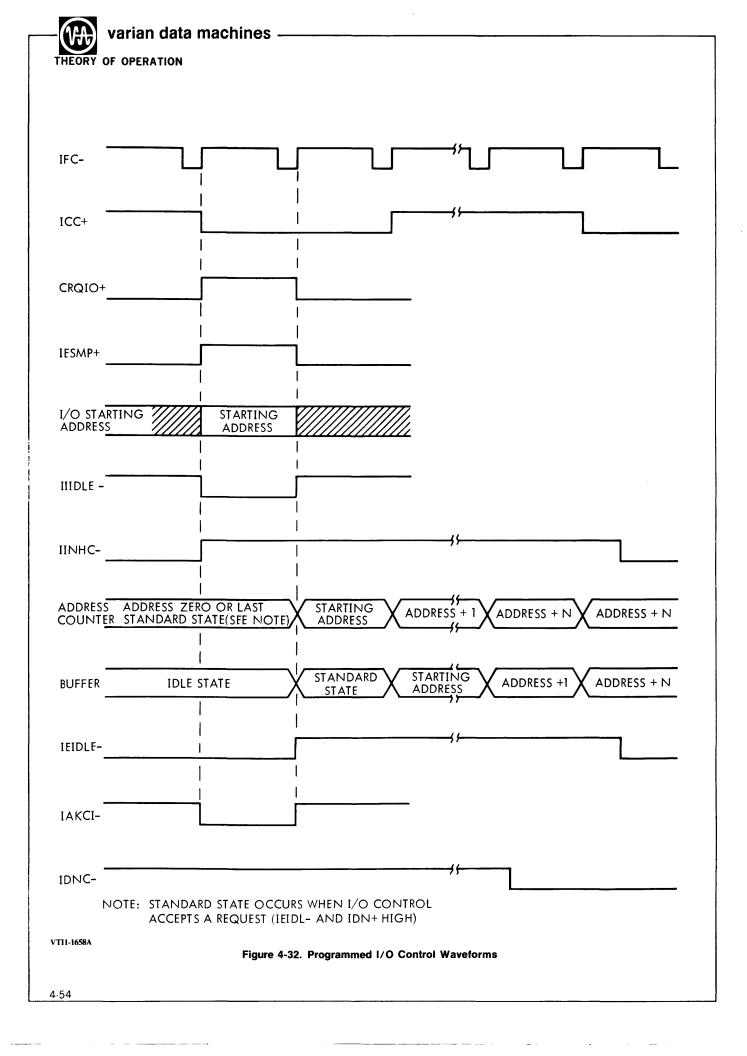

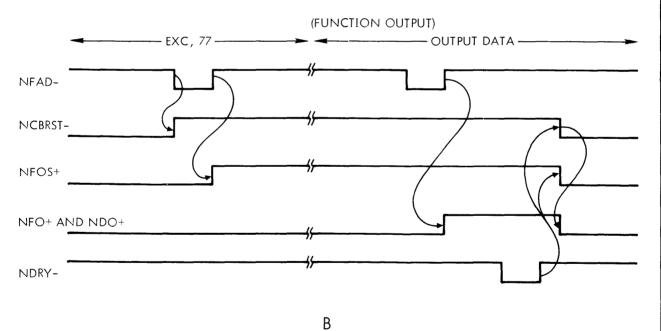

|           | 32. Programmed I/O Control Waveforms            |      |

|           | 33. Interrupt Flow Diagram                      |      |

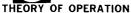

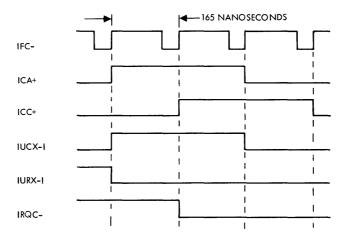

|           | 34. Interrupt Timing Waveforms                  |      |

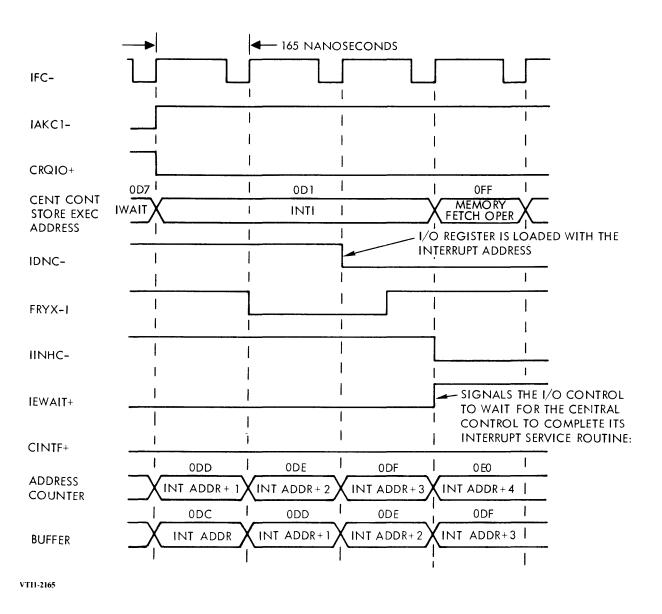

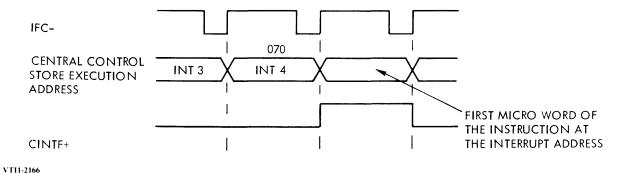

|           | 35. Sub-Operation 1 Timing Waveforms            |      |

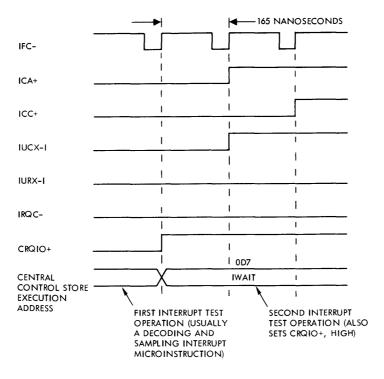

|           | 36. Sub-Operation 2 Timing Waveforms            |      |

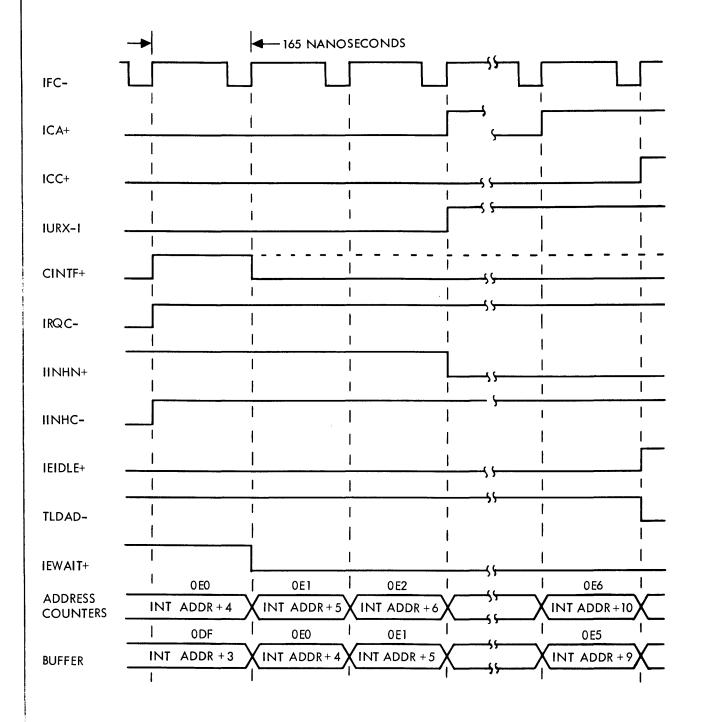

|           | 37. Sub-Operation 3 Timing Waveforms            |      |

|           | 38. Sub-Operation 4 and 5 Timing Waveforms      |      |

|           | 39. Sub-Operation 6 Timing Waveforms            |      |

|           | 40. Sub-Operation 7 Timing Waveforms            |      |

|           | 41. Normal DMA Waveforms                        |      |

|           | 42. High-Speed DMA Waveforms                    |      |

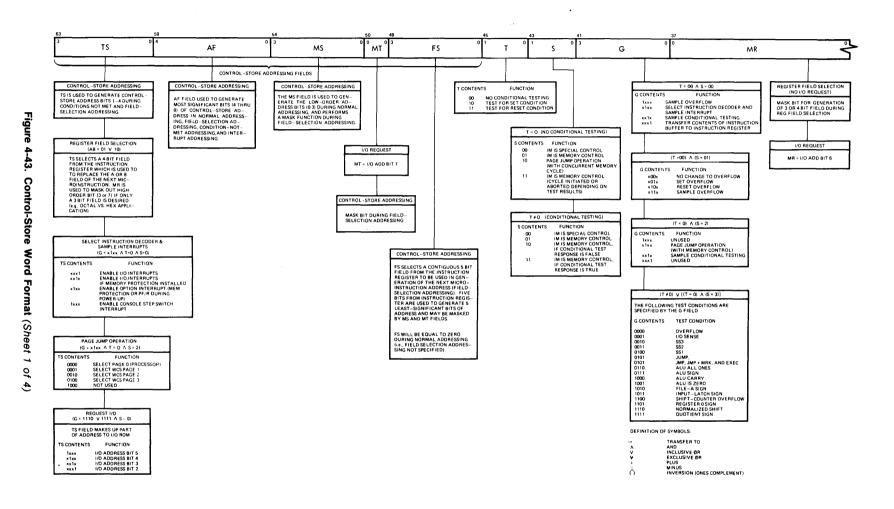

|           | 43. Control-Store Word Format (Sheet 1 of 4)    |      |

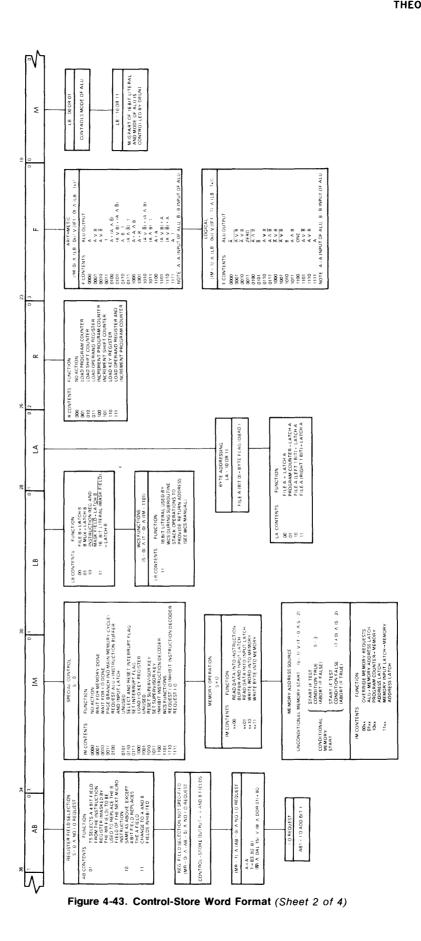

|           | 43. Control-Store Word Format (Sheet 2 of 4)    |      |

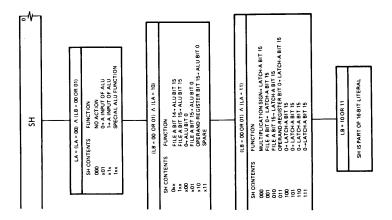

|           | 43. Control-Store Word Format (Sheet 3 of 4)    |      |

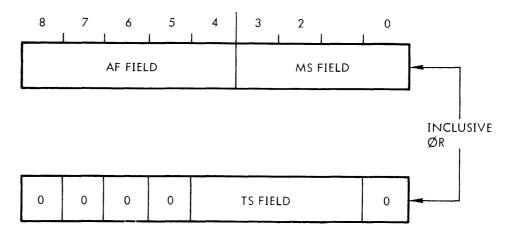

|           | 43. Control-Store Word Format (Sheet 4 of 4)    |      |

|           | 44. Normal Addressing                           |      |

|           | 45. Normal/TS Field Addressing                  |      |

|           | 46. Formation of Field-Selection Addressing     |      |

| _         | 47. Addressing When Condition is Not Met        |      |

|           | 48. Interrupt Addressing                        |      |

|           | 49. Output Formats of ROM Decoders              |      |

|           | 50. Decoding Address Components                 |      |

|           | 51. Control-Panel Circuits Block Diagram        |      |

|           | 52. Interrupt Control Waveforms                 |      |

|           | 53. I/O Control Buffer Waveforms                | 4-83 |

نن٧

# LIST OF ILLUSTRATIONS (continued)

| Figure 4-54. Pulse Register Waveforms                                         | 4-84         |

|-------------------------------------------------------------------------------|--------------|

| Figure 4-55. Flowchart for LDA Instruction                                    |              |

| Figure 4-56. Flow Diagram of LDA Instruction                                  |              |

| Figure 4-57. STA Instruction Timing Diagram                                   |              |

|                                                                               |              |

|                                                                               |              |

|                                                                               |              |

| LIST OF TABLES                                                                |              |

| LIST OF TABLES                                                                |              |

| Table 1-1. Processor Specifications                                           | 1-1          |

| Table 3-1. Binary Codes for Register Selection                                |              |

| Table 3-2. Automatic Bootstrap Programs for High-Speed and Teletype Readers . |              |

| Table 3-3. Automatic Bootstrap Program for Disc Memory                        |              |

| Table 3-4. Manual Bootstrap Programs                                          |              |

| Table 4-1. Instruction Multiplexor Truth Table (IC Type SN74151)              |              |

| Table 4-2. A2 ROM Truth Table                                                 | 4.7          |

| Table 4-3. A3 ROM Truth Table                                                 | 4-7          |

| Table 4-4. Register Multiplexor Truth Table (IC Type SN74151)                 | 4-12         |

| Table 4-5. T-Field Decoder Truth Table                                        |              |

| Table 4-6. S-Field Decoder Truth Table                                        | 4-14         |

| Table 4-7. IM-Field Decoder Truth Table                                       | 4-14         |

| Table 4-8. Register File Address Codes                                        | 4-19         |

| Table 4-9. Shifting Multiplexor Truth Table                                   |              |

| Table 4-10. B-Field Codes                                                     |              |

| Table 4-11. ALU Operations                                                    | 4-25         |

| Table 4-12. Register-Control Decoder Truth Table                              |              |

| Table 4-13. Shift-Left Multiplexors Truth Table                               | 4-27         |

| Table 4-14. Shift-Right Multiplexors Truth Table                              |              |

| Table 4-15. Operand Register Modes                                            | 4-28         |

| Table 4-16. Address Multiplexor Truth Table                                   | 4-30         |

| Table 4-17. I/O Multiplexor Truth Table                                       | 4-37         |

| Table 4-18. I/O Register Modes                                                | 4-37         |

| Table 4-19. Programmed I/O for SEN, EXC, and EXC2 Instructions                | 4-41         |

| Table 4-20. Programmed I/O, Input-Data Transfer                               | 4-41         |

| Table 4-21. Programmed I/O, Output-Data Transfer                              | 4-42         |

| Table 4-22. DMA, Trap-Out Operation                                           | 4-42         |

| Table 4-23. DMA, Trap-In Operation                                            | 4-43         |

| Table 4-24. High-Speed DMA, Trap-Out Operation                                | 4-43         |

| Table 4-25. High-Speed DMA, Trap-In Operation                                 | 4-44         |

| Table 4-26. I/O Interrupt Operation                                           | 4.44         |

| Table 4-27. Field-Selection Addressing Contribution                           | 4-73         |

| Table 4-28. Test Conditions                                                   | 4-75         |

| Table 4-29. TS-Field Interrupt Functions                                      | 4-75         |

| Table 4-30. Toggle Register Truth Table                                       | 4.79         |

| Table 4-31. Input Encoder Truth Table                                         | <b>4-8</b> 2 |

| Table 6-1. Mnemonics                                                          | 6-1          |

|                                                                               |              |

# SECTION 1 GENERAL DESCRIPTION

The Varian 70 Series Processor Manual describes the processor, I/O control, and control panel.

The manual is divided into six sections:

- Features and specifications of the processor, and related publications

- · Installation and interconnection data

- Operation

- · Theory of operation

- Maintenance

- Mnemonics list

Documents such as logic diagrams, schematics, and parts lists are supplied in a System Maintenance Manual. This manual is assembled when the equipment is shipped, and reflects the configuration of a specific system.

The following list contains the part numbers of other manuals pertinent to the Varian 70 series computers (the x at the end of each document number is the revision number and can be any digit 0 through 9):

High-speed logic and use of a 60-nanosecond access-time control store permits the Varian 73 processor to execute a single microinstruction in 165 nanoseconds. A processor interface is provided that permits the internal control-store to be disabled by a writable control store allowing for special applications through user microprograms. Other features of the processor are:

- · High performance through instruction pipelining

- · Extendable architecture through microprogramming

- Independent operation of memory, I/O, and processor functions

- Multiple-bus structure

- 16 general-purpose registers

- Comprehensive set of shift, arithmetic, and logical functions

Table 1-1 lists the specifications of the processor.

## Table 1-1. Processor Specifications

| Parameter                  | Specification                                                                                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Speed                      | 165 nanoseconds (microinstruction execution time)                                                                                                                      |

| Word length                | 16 bits                                                                                                                                                                |

| Logic levels<br>(internal) | High = $+2.4$ to $+5.0$ V dc<br>Low = $-0.4$ to $+0.8$ V dc                                                                                                            |

| Logic levels<br>(1/0 bus)  | High = $+2.8$ to $+3.6$ V dc<br>Low = $-0.4$ to $+0.8$ V dc                                                                                                            |

| Power                      | Processor board: 5V dc at 12A Option board (with all options): 5V dc at 11A Control-panel board: 5V dc at 2.1A Termination shoes (on back of mainframe): 5V dc at 3.2A |

| Environment                | 0 to 50 degrees C, 10 to 90 percent relative humidity without condensation.                                                                                            |

| Forced-air<br>cooling      | For each 3W dc power, one cubic foot of air per minute applied above and below each circuit board.                                                                     |

# SECTION 2 INSTALLATION

### 2.1 INSPECTION

The processor has been packed and inspected to ensure its arrival in good working order. To prevent damage, take care during unpacking and handling. Check the shipping list to ensure that all equipment has been received. Immediately after unpacking, inspect the equipment for shipping damage. Ascertain that wires and cables are neither loose nor broken, and that hardware is secure. If damage exists:

- a. Notify the transportation company.

- b. Notify Varian Data Machines.

- c. Save all packing material.

### 2.2 PHYSICAL DESCRIPTION

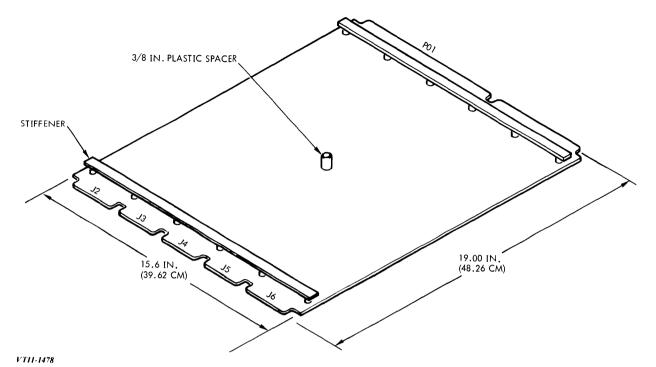

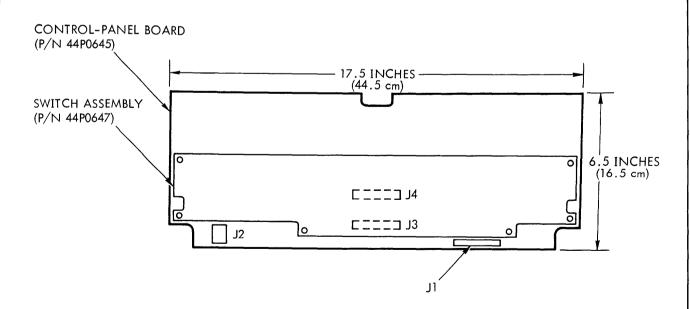

The processor circuits are on the 15.6 by 19 inch processor board (p/n 44P0614), the I/O control circuits are on a portion of the 15.6 by 19 inch option board (p/n 44P0619), and the control-panel circuits are on the 6.5 by 17.5 inch control-panel board (p/n 44P0645). On the control-panel board, is mounted a switch assembly (p/n 44P0647) containing control-panel switches. The printed-circuit (PC) boards are illustrated in figures 2-1 and 2-2.

Figure 2-3 shows the locations of the processor, option, and control-panel boards in a typical mainframe installation. The control panel can be hinged open (figure 2-3) or completely removed from the mainframe as follows:

- Pull out the control panel to the locked position (approximately 2 inches).

- b. Lift up on the control panel a fraction of an inch. The panel can now be hinged down to its open position.

- c. For complete removal of the control panel, unplug cables from connectors J1 and J2 on the control-panel board, press in the locking devices on sides of slides, and pull panel completely out of the mainframe.

- d. To install the control panel back into the mainframe, insert slides into slide rails and slide the panel toward the mainframe (the slide locking devices must be pressed to move panel past the locked position).

### 2.3 INTERCONNECTION

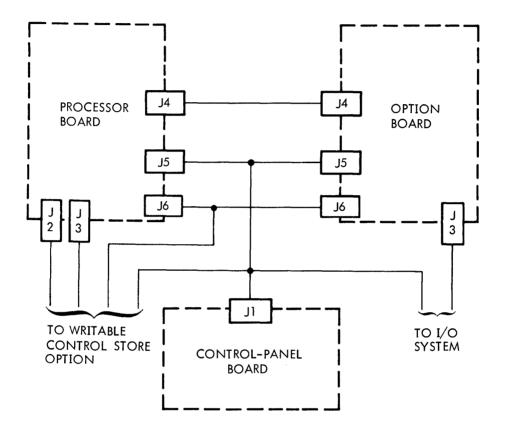

Circuit-board connector functions are listed as follows:

- a. Processor board

- P1, memory and power

- J2, writable control store

- J3. writable control store

- J4, option board

- J5, I/O lines

- J6, multiple processor and writable control store

- b. Option board

- P1, memory and power

- J2, not used

- J3, auxiliary I/O lines

- J4, processor board

- J5. I/O lines

- J6. writable control store and processor

- J7, priority memory access

- J8, Teletype

- c. Control-panel board

- J1, I/O lines

- J2, power

- J3, switch assembly

- J4, switch assembly

The pin assignments for these circuit-board connectors are given in the logic diagrams of each board (in System Maintenance Manual). Logic diagram part numbers are:

- a. Processor logic diagram, p/n 91B0378.

- b. Option logic diagram, p/n 91B0401.

- c. Control-panel logic diagram, p/n 91B0406.

Interconnection of the processor, option, and control-panel boards is shown in figure 2-4.

Figure 2-1. Processor or Option Board

NOTE: ELECTRICAL CONNECTIONS BETWEEN CONTROL-PANEL BOARD AND SWITCH ASSEMBLY ARE VIA J3 AND J4

Figure 2-2. Control Panel Board

POWER CABLE, TO POWER BACKPLANE

CONTROL-PANEL BOARD

I-O BUS CABLE

CONTROL PANEL

MAINFRAME

-111.18 CM

FAN (3)

13. 18 CHES .

20 11 CHES .

PROCESSOR BOARD

OPTION BOARD

VT11-1672

Figure 2-4. Interconnection Diagram

# SECTION 3 OPERATION

This section describes the operation of the Varian 70 series computers.

### 3.1 SWITCHES AND INDICATORS

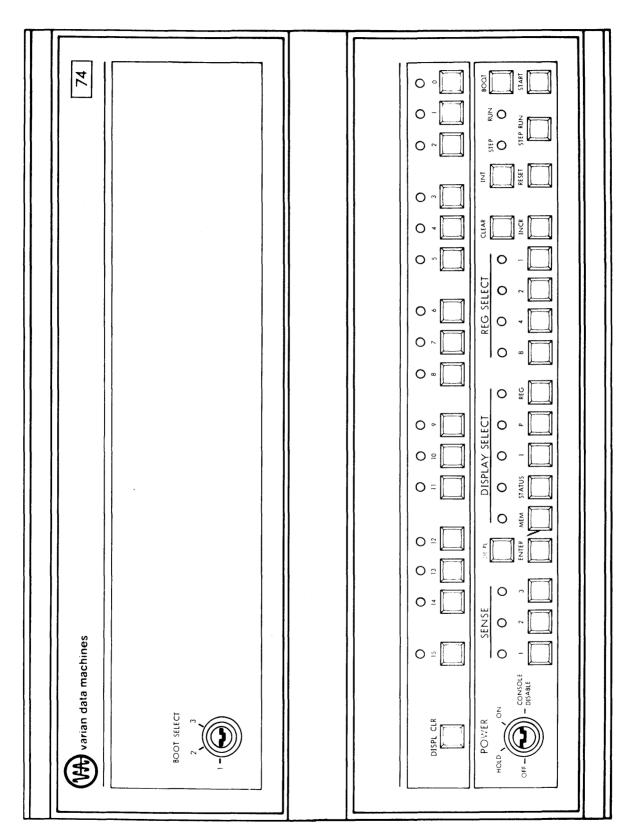

The Varian 74 control panel (figure 3-1) contains all of the switches and indicators needed for operating the system. Except for the POWER and BOOT SELECT switches, which are key-operated, all control-panel switches are pushbuttons. Control panels for the Varian 72 and 73 computers do not have the BOOT SELECT switch but otherwise have identical switches and indicators as shown in figure 3-1.

### 3.1.1 POWER Switch

The POWER switch is a key-operated, four-position switch that controls the ac line voltage to the computer power supply.

In the OFF position, the ac line voltage is removed from the input of the power supply and the optional data saver is disabled (if present). NOTE: When turning off power on systems with semiconductor memory, do not restore power for at least 30 seconds to ensure the refresher logic is operating.

In the HOLD position, the ac line voltage is applied to the power supply. All dc voltages are disabled except those required to maintain data in the semiconductor memory. Neither the computer nor the control panel is operational.

In the ON position, the ac line voltage is applied to the power supply. Both the computer and control panel are fully operational.

The CONSOLE DISABLE position is jumper-selectable to operate in two modes:

- a. All control-panel pushbutton switches are disabled.

- b. Only the STEP/RUN and RESET switches are disabled.

The jumper is factory-installed on the control-panel circuit board. With the POWER switch in the CONSOLE DISABLE position, the ac line voltage is applied to the power supply, the computer is operational, and the control-panel indicator lights are functional. The key can be removed from the POWER switch in any of the four positions.

To turn off the computer from the CONSOLE DISABLE position, turn the POWER switch ON, place the computer in the step mode (using STEP/RUN switch), and then turn the POWER switch to either HOLD (to maintain data in semiconductor memory) or OFF.

# 3.1.2 STEP/RUN Switch and STEP and RUN Indicators

The STEP/RUN switch is an alternate-action switch that switches the computer alternately to the step and run modes. In the step mode, the STEP indicator lights. In the run mode, the RUN indicator blinks until the START switch is pressed, at which time the RUN indicator comes on continuously.

When the computer is in the step mode, pressing the STEP/RUN switch places the computer in the run mode. The STEP indicator goes out and the RUN indicator blinks. When in the run mode, the computer is ready to be started (by pressing the START switch).

When the computer is in the run mode and has been started, pressing the STEP/RUN switch halts the computer after the current instruction has been executed and the next instruction fetched and loaded into the I register. The RUN indicator goes out and the STEP indicator lights. In addition, a halt instruction (after the computer has been started) halts the computer and causes the RUN indicator to blink.

### 3.1.3 START Switch

When the computer is in the run mode but has not been started, pressing the START switch starts the program at the location specified by the contents of the program counter. The RUN indicator stops blinking and comes on continuously.

When the computer is in the step mode, pressing the START switch executes the instruction in the instruction register. Then it fetches the next instruction from the memory address specified by the contents of the program counter and loads it in the instruction register. The STEP indicator remains on.

### 3.1.4 BOOT Switch

The BOOT switch allows the bootstrap program to be loaded into the computer memory automatically. The bootstrap program enables the loading of the binary load/dump program into memory. When BOOT is pressed, the RUN indicator lights. Refer to the program execution portion of this section for bootstrap program loading procedures.

VTII-2127

Figure 3-1. Varian 74 Control Panel

# 3.1.5 Register-Entry Switches and Register-Display Indicators

The top row of control-panel lights comprises the 16 register-dislay indicators. They display the contents of the display register. This register, located on the control-panel circuit board, can be loaded from the register-entry switches on the control panel just below the 16 indicators. In addition, 16-bit data words can be loaded into the display register under control of the DISPLAY SELECT and REG SELECT switches (sections 3.1.7 and 3.1.9), allowing visual inspection of the contents of various registers and memory addresses.

Any of the sixteen bits can be set by pressing the corresponding register-entry switch. With a bit set, the corresponding display indicator lights. Pressing a registerentry switch for a bit already set has no effect. Bits can be reset only to zero by pressing the DISPL CLR switch (section 3.1.6).

For negative data, the sign bit (bit 15) is set (one).

### 3.1.6 DISPL CLR Switch

The contents of the display register can be cleared (reset to zero) by pressing the DISPL CLR switch. This turns off all sixteen display indicators.

## 3.1.7 DISPLAY SELECT Switches and Indicators

The five DISPLAY SELECT switches are used to select one of several registers for displaying its contents on the register display indicators and altering them from the register-entry switches. Pressing any DISPLAY SELECT switch cancels any previous selection, turns off the indicators for the previous selection, and lights the indicators for the new selection. Pressing DISPL CLEAR (section 3.1.6) clears the display register and turns off the display indicators.

### 3.1.7.1 MEM Switch

The MEM switch selects the memory for data entry or display. For entering data into memory and displaying the contents of memory refer to the manual operations (section 3.2).

### 3.1.7.2 STATUS Switch

The STATUS switch displays the status of various signals from the processor. To display the status of these processor signals:

a. Turn the POWER switch ON.

- b. Place the computer in the step mode.

- c. Press STATUS.

The register-display indicators now indicate the following:

- Bit 15, Key register bit 15 (DCK15+)

- Bit 14, Key register bit 14 (DCK14+)

- Bit 13, Key register bit 13 (DCK13+)

- Bit 12, Key register bit 12 (DCK12+)

- Bit 11, Arithmetic and logic unit carry (DCNDC+)

- Bit 10, Arithmetic and logic unit sign (DSGN+)

- Bit 9, Arithmetic and logic unit output equals all ones (DEQ+)

- Bit 8, Arithmetic and logic unit overflow (DOVF + )

- Bit 7, Shift counter output bit 4 (DSC04+)

- Bit 6, Shift counter output bit 3 (DSC03+)

- Bit 5, Shift counter output bit 2 (DSC02+)

- Bit 4, Shift counter output bit 1 (DSC01 +)

- Bit 3, Shift counter output bit 0 (DSC00+)

- Bit 2, Arithmetic and logic unit output zero (DCNOZ+)

- Bit 1, Supervisor mode (CESK+)

- Bit 0. Not used

### 3.1.7.3 | Switch

The I switch selects the instruction (I) register for data display or entry. Pressing the I switch while the RUN indicator is off or blinking (step mode or halted) displays the contents of the instruction register on the register-display indicators. Changing the contents of the display register, by pressing the DISPLAY CLR switch and the register entry switches, automatically changes the contents of the instruction register. The instruction register contains the instruction to be executed next.

### 3.1.7.4 P Switch

The P switch selects the program (P) counter for data display or entry. Pressing the P switch while the RUN indicator is off or blinking (step mode or halted) displays the contents of the program counter on the register-display indicators. Changing the contents of the display register, by pressing the DISPLAY CLR and register-entry switches, automatically changes the contents of the program counter. The program counter contains the address of the next instruction to be fetched.

### **OPERATION**

### 3.1.7.5 REG Switch

The REG switch enables one of the registers designated by the REG SELECT switches (section 3.1.9) to be selected for data display or entry.

### 3.1.8 DISPL and ENTER Switches

The DISPL switch is used with the MEM switch (section 3.1.7.1) for displaying memory data on the register-display indicators.

The ENTER switch is used with the MEM switch to load data into memory from the register-entry switches.

The procedures for displaying memory data and entering data into memory are described under manual operations (section 3.2).

### 3.1.9 REG SELECT Switches and Indicators

When the REG switch (section 3.1.7.5) is pressed, any desired general-purpose register (including A, B, or X) can be selected for displaying its contents on the registerdisplay indicators or altering its contents from the registerentry switches. The register selection is accomplished by entering a binary code using the four REG SELECT switches designated 8, 4, 2, 1. A one bit is produced by pressing the appropriate REG SELECT switch; a zero bit is produced by not pressing the switch. A one bit causes the corresponding indicator to light. The binary codes for specific registers are listed in table 3-1. When the binary code has been entered, the register-display indicators automatically display the contents of the selected register. Changing the contents of the display register, using the DISPLAY CLR and registerentry switches (sections 3.1.5 and 3.1.6), automatically changes the contents of the selected register.

**Table 3-1.** Binary Codes for Register Selection

| REG | SEL | ECT | Sv | vitches | Selected Register |

|-----|-----|-----|----|---------|-------------------|

|     | 8   | 4   | 2  | 1       |                   |

|     | 0   | 0   | 0  | 0       | А                 |

|     | 0   | 0   | 0  | 1       | В                 |

|     | 0   | 0   | 1  | 0       | Х                 |

|     | 0   | 0   | 1  | 1*      |                   |

|     | 0   | 1   | 0  | 0*      |                   |

|     | 0   | 1   | 0  | 1*      |                   |

|     | 0   |     | 1  | 0*      |                   |

|     | 0   | 1   | 1  | 1*      |                   |

|     | 1   | 0   | 0  | 0*      |                   |

|     |     |     |    |         |                   |

continued

### **REG SELECT Switches**

Selected Register

| 1 | 0 | 0 | 1* |

|---|---|---|----|

| 1 | 0 | 1 | 0* |

| 1 | 0 | 1 | 1* |

| 1 | 1 | 0 | 0* |

| 1 | 1 | 0 | 1* |

| 1 | 1 | 1 | 0* |

| 1 | 1 | 1 | 1* |

\* These codes select registers that are not used for programming with the instruction set of a Varian 70 system. They are available for WCS microprogramming use. With two exceptions, the contents of these registers can be displayed and altered using the control panel. However, such alteration should be done only for maintenance purposes or special applications. The register selected with 0100 always contains the contents of the instruction register. The registers selected with 0011 and 0101 always contain all zeros and all ones, respectively; the contents of these two registers cannot be altered from the control panel.

### 3.1.10 CLEAR and INCR Switches

The binary code for a selected register (section 3.1.9) is cleared (set to zero) by pressing the CLEAR switch. Each time the INCR switch is pressed, the binary code for a selected register is incremented by one, selecting the subsequent register.

### 3.1.11 INT Switch

The INT switch is used to interrupt the computer and is functional only in the run mode (RUN indicator on). Pressing the INT switch interrupts to memory address zero.

### 3.1.12 RESET Switch

Pressing the RESET switch:

- a. Halts the computer

- b. Stops I/O operation

- c. Initializes both the computer and its peripheral devices

- d. Leaves the computer in step mode

- e. If the computer was in run mode, turn the RUN indicator off and the STEP indicator on.

- f. Resets the overflow indicator (bit-8 register-display indicator with STATUS switch pressed, section 3.1.7.2).

### 3.1.13 SENSE Switches and Indicators

The three alternate-action SENSE switches permit the execution of predetermined program branching by the operator. When the program contains jump, jump-andmark, or execution instructions that depend upon the setting of the SENSE switches, the jumps and executions occur only if the switch conditions are met.

Pressing a SENSE switch sets it and causes its associated indicator to light. Pressing the same switch again resets it, causing its indicator to go out.

For example, a program can be written so that the operator can obtain a partial total of a column of figures being added by use of the JSS1 (jump if SENSE switch 1 is set) instruction. The program writes individual entries as long as SENSE switch 1 is not set. When the operator wants a partial total, he sets the switch. The program then jumps to an instruction sequence that prints the desired information.

### 3.1.14 BOOT SELECT Switch

The BOOT SELECT switch is a key-operated switch available with the Varian 74 to select one of the three automatic bootstrap programs. After the selection is made, the bootstrap program is automatically loaded into memory by pressing the BOOT switch (section 3.1.4).

BOOT SELECT switch positions with corresponding automatic bootstrap programs are listed below:

Position 1 Teletype

Position 2 High-speed paper tape reader

Position 3 Disc memory

### 3.2 MANUAL OPERATIONS

Using the control-panel switches and indicators (section 3.1), data or instructions can be transferred manually to or from memory or a selected register, and stored programs can be executed manually.

Manual execution of a stored program is discussed in section 3.3.

### 3.2.1 Displaying Register Contents

To display the contents of the instruction register:

- a. Place the computer in step mode

- b. Press I

To display the contents of the program counter:

- a. Place the computer in step mode

- b. Press P

To display the contents of the A, B, or X or register:

- a. Place the computer in the step mode

- b. Press REG

- Using the four REG SELECT switches, enter the appropriate binary code (0000 for A register, 0001 for B register, or 0010 for X register)

### 3.2.2 Displaying Memory Contents

To display the contents of a memory address:

- a. Place the computer in step mode

- b. Press P

- c. Using the DISPL CLR and register entry switches, enter the desired memory address in the program counter

- d. Press MEM

- e. Press DISPL switch. The contents of the selected memory address are now displayed on the register-display indicators. The program counter is automatically incremented.

- f. Repeated actuation of the DISPL switch displays the contents of consecutive memory addresses

### 3.2.3 Displaying Overflow Status

To display the overflow status:

- a. Place the computer in step mode

- b. Press STATUS

- c. If register-display bit 8 is on, there is overflow.

### 3.2.4 Entering Data in Memory

To enter data in memory:

- a. Place the computer in step mode

- b. Press P

- c. Using the DISPL CLR and register-entry switches, enter the memory address in the program counter.

- d. Press MEM

- e. Using the DISPL CLR and register entry switches, enter the data in the display register.

continued

# varian data machines

### OPERATION

- Press ENTER to load the data in the previously addressed memory location. The program counter is automatically incremented.

- g. Repeat steps e and f to enter data in consecutive memory addresses.

### 3.2.5 Entering Data in a Register

To enter data or instructions in a register:

- a. Display the contents of the selected register as described in section 3.2.1.

- Using the DISPLAY CLR and register-entry switches, enter the desired data or instruction in the selected register.

### 3.3 PROGRAM EXECUTION

To make a cold start (i.e., when a new system is being initialized or the contents of memory are unknown):

- a. Turn the power on

- b. Load the bootstrap program

- c. Load the binary load/dump program

- d. Load the object program

Instructions for steps a and b are provided below. Loading the binary load/dump and object programs is discussed in the Binary Load/Dump Program section of the applicable system handbook, with manual execution of a stored program explained below in section 3.3.3.

### 3.3.1 Power On

Turn on computer power by placing the POWER switch to ON. When power is first turned on, the following conditions apply:

- a. Step mode (STEP indicator on)

- b. Sense switches not set (SENSE indicators off)

- c. Display register cleared (register display indicators off)

- d. Pswitch on (Pindicator on)

- e. REG SELECT switches off (REG SELECT indicators off)

When power is removed and reapplied without actuation of the POWER switch (by loss and recovery of the ac line voltage), the same conditions apply, except the computer will be in the run mode (RUN indicator on) instead of the step mode.

### 3.3.2 Loading the Bootstrap Program

The bootstrap program permits the loading of the binary load/dump program into memory. Various input devices such as Teletype paper tape reader, high-speed paper tape reader, or disc memory unit can be used to load the binary load/dump program. The computer is wired at the factory to allow it to operate with a specific input device.

The automatic bootstrap program for the Teletype is included as a standard feature with Varian 72 and 73 computers. With the Varian 74, three automatic bootstraps are included: Teletype paper tape reader, high-speed paper tape reader, and disc memory. The desired bootstrap is selected with the BOOT SELECT switch. Switch positions 1, 2, and 3 select the Teletype, high-speed paper tape reader, and disc memory, respectively. Before the bootstrap program is loaded, the binary load/dump tape (if paper tape input is being used) should be inserted into the paper tape reader with the first binary frame at the reading station.

Addresses and instruction codes (octal) for the automatic bootstrap programs are listed in tables 3-2 and 3-3. When loading a bootstrap program manually, refer to table 3-4.

To load the automatic bootstrap program:

- With the POWER switch in the ON position, place the computer in the run mode by pressing the STEP/RUN switch (RUN indicator blinking)

- Press BOOT (RUN indicator is now on). This transfers the bootstrap program from the processor's controlstore to computer memory. The binary load/dump program can now be loaded into memory automatically

To load the bootstrap program manually:

- a. With the POWER switch in the ON position, place the computer in step mode (STEP indicator on)

- b. Press P

- Using the DISPL CLR and register entry switches, enter the starting memory address (007756) of the bootstrap program in the program counter

- d. Press MEM

- e. Using the DISPL CLR and register entry switches, enter the appropriate code of the next instruction in the console register (table 3-2)

- f. Press ENTER to load instruction code into the memory address specified by the program counter. The program counter is incremented automatically.

- g. Repeat steps e and f for each of the remaining bootstrap instructions

**Instruction Code**

100020

100016

101416

001157

102516

151167

001016

001130

001000

000600

007760

Symbolic Coding

| Table 3-2.                              |

|-----------------------------------------|

| <b>Automatic Bootstrap Programs for</b> |

| <b>High-Speed and Teletype Readers</b>  |

| Address                                                                                                    | Instruction Code                                                                                                       | Symbolic Coding                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000200<br>000201<br>000202<br>000203<br>000204<br>000205<br>000206<br>000207<br>000200<br>000211<br>000212 | 102637* (102601)<br>004011<br>004041<br>004446<br>001020<br>000214<br>055000<br>001010<br>007000<br>0005144<br>0005101 | Symbolic Coding           READ         CIB         RDR           ASLB         NBIT           LRLB         1           LLRL         6           JBZ         SEL           (Memory address)         STA         0,1           JAZ         LHLT+1           (Memory address)         IXR           ENTR         INCR         1 |

| 000213                                                                                                     | 100537* (102601)                                                                                                       | SEL RDON                                                                                                                                                                                                                                                                                                                    |

| 000214                                                                                                     | 101537* (101201)                                                                                                       | SEL EXC IBFR,READ                                                                                                                                                                                                                                                                                                           |

| 000200                                                                                                     | 007000                                                                                                                 | (Memory address)                                                                                                                                                                                                                                                                                                            |

| 000211                                                                                                     | 0005144                                                                                                                | IXR                                                                                                                                                                                                                                                                                                                         |

| 000214                                                                                                     | 101537* (101201)                                                                                                       | SEL EXC IBFR,READ                                                                                                                                                                                                                                                                                                           |

| 000215                                                                                                     | 000200                                                                                                                 | (Memory address)                                                                                                                                                                                                                                                                                                            |

| 000216                                                                                                     | 001000                                                                                                                 | JMP *2                                                                                                                                                                                                                                                                                                                      |

| 000217                                                                                                     | 000214                                                                                                                 | (Memory address)                                                                                                                                                                                                                                                                                                            |

|                                                                                                            |                                                                                                                        | () ================================                                                                                                                                                                                                                                                                                         |

<sup>\*</sup>When using the Teletype reader, replace this code with the one in parentheses.

# Table 3-4. Manual Bootstrap Programs

Teletype

Reader

Code

**Address**

001155

001156

001157

001160

001161

001162

001163

001164

001165

001166

001167

High-Speed

Reader

Address

| Table 3-3.                         |     |

|------------------------------------|-----|

| <b>Automatic Bootstrap Program</b> | for |

| Disc Memory                        |     |

| Instruction Code |  |  |  |  |

|------------------|--|--|--|--|

| 100416           |  |  |  |  |

| 104016           |  |  |  |  |

| 100216           |  |  |  |  |

| 005001           |  |  |  |  |

| 103116           |  |  |  |  |

| 101016           |  |  |  |  |

| 001141           |  |  |  |  |

| 001000           |  |  |  |  |

| 001135           |  |  |  |  |

| 102516           |  |  |  |  |

| 151167           |  |  |  |  |

| 100021           |  |  |  |  |

| 001130           |  |  |  |  |

| 100021           |  |  |  |  |

| 100316           |  |  |  |  |

| 005102           |  |  |  |  |

| 103216           |  |  |  |  |

| 103120           |  |  |  |  |

| 006010           |  |  |  |  |

| 001130           |  |  |  |  |

| 103121           |  |  |  |  |

|                  |  |  |  |  |

| 007756                                         | 102637                                         | 102601                                         | READ CIB RDR                                                |

|------------------------------------------------|------------------------------------------------|------------------------------------------------|-------------------------------------------------------------|

| 007757                                         | 004011                                         | 004011                                         | ASLB NBIT - 7                                               |

| 007760                                         | 004041                                         | 004041                                         | LRLB 1                                                      |

| 007761                                         | 004446                                         | 004446                                         | LLRL 6                                                      |

| 007762                                         | 001020                                         | 001020                                         | JBZ SEL                                                     |

| 007763                                         | 007772                                         | 007772                                         | (Memory address)                                            |

| 007764                                         | 055000                                         | 055000                                         | STA 0,1                                                     |

| 007765                                         | 001010                                         | 001010                                         | JAZ LHLT + 1                                                |

| 007766                                         | 007000(a)                                      | 007000(a)                                      | (Memory address)                                            |

| 00//00                                         | 007000(a)                                      | 007000(a)                                      | (Wichioly address)                                          |

| 007767                                         | 005144                                         | 005144                                         | IXR                                                         |

|                                                | ` '                                            | ` '                                            | , ,                                                         |

| 007767                                         | 005144                                         | 005144                                         | IXR                                                         |

| 007767<br>007770                               | 005144<br>005101                               | 005144<br>005101                               | IXR<br>ENTR INCR 1                                          |

| 007767<br>007770<br>007771                     | 005144<br>005101<br>100537                     | 005144<br>005101<br>102601                     | IXR ENTR INCR 1 SEL RDON                                    |

| 007767<br>007770<br>007771<br>007772           | 005144<br>005101<br>100537<br>101537           | 005144<br>005101<br>102601<br>101201           | IXR ENTR INCR 1 SEL RDON SEL EXC IBFR,READ                  |

| 007767<br>007770<br>007771<br>007772<br>007773 | 005144<br>005101<br>100537<br>101537<br>007756 | 005144<br>005101<br>102601<br>101201<br>007756 | IXR ENTR INCR 1 SEL RDON SEL EXC IBFR,READ (Memory address) |

### NOTE

The bootstrap loader routine is always loaded into the highest address of the first 4K memory increment, regardless of available memory. BLD II relocation and adaptation to the specified input device are described in the Binary Load/Dump Program section of the applicable system handbook.

(a) Replace this code with 007600 if the test executive of MAINTAIN II document 98 A 9952 060) is to be loaded and executed.

## 3.3.3 Executing a Stored Program

To execute a stored program manually:

- a. Place the computer in step

- b. Press P

**OPERATION**

- c. Using the DISPL CLR and register entry switches, enter the address of the first program instruction in the program counter

- d. Press I

- e. Press DISPL CLR to clear the instruction register

- f. Press START. This loads the instruction specified by the program counter into the instruction register

- g. Press START again. This executes the instruction and loads the next program instruction into the instruction register

- h. Repeat step g for each instruction in the program

To execute a stored program automatically: perform steps a through e above, place the computer in the run mode by pressing the RUN/STEP switch, and press START.

# SECTION 4 THEORY OF OPERATION

### 4.1 GENERAL

This section describes the circuit operations of the processor board, I/O control portion of the option board, and control-panel board. Furthermore, the control-store word format and addressing are also described. For the most part, the circuit descriptions are written to functional block diagrams that accompany the text. In some cases, however, the reader may wish to refer to the appropriate logic diagram in the System Maintenance Manual. Logic diagram part numbers are:

- a. Processor board, 91B0378

- b. Option board, 91B0401

- c. Control-panel board, 91B0406

For ease of reading, some mnemonics are written with the variable n in place of the actual bit numbers. For example, ALU data mnemonics DAL00+ through DAL15+ are written DALn+(0.15). Mnemonic conventions and definitions are provided in section 6.

### 4.2 FUNCTIONAL DESCRIPTION

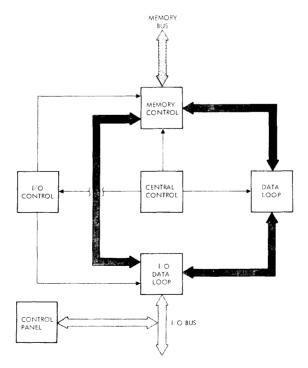

As illustrated in figure 4-1, the major functional sections of the processor are central control, data loop, memory control, I/O data loop, and I/O control. Except for the I/O control, which is located on the option board, these sections are on the processor board. Communication

between the processor and the control panel is via the I/O bus. The processor bus structure is illustrated in figure 4-2. A brief description of the five major sections is provided in the following subsections.

### 4.2.1 Central Control

The central control is the heart of the processor. It contains the instruction register, control store, control store buffer, and control sequencing logic. The following functions are performed by the central control:

- a. Initiates memory operations

- b. Initiates I/O operations

- c. Decodes instructions

- d. Controls data transfers and manipulations

- e. Tests internal data loop conditions

- f. Responds to interrupts

The 16-bit instruction register receives instructions from an instruction buffer which is then free to accept new instructions. This double buffering of instructions provides a pipelining technique that allows the next instruction to be fetched during an otherwise unused memory cycle. The output of the instruction register can then be routed to the arithmetic and logic unit (ALU) or further decoding may be performed.

VTII-1500A

Figure 4-1. Processor Functional Block Diagram

Figure 4-2. Processor Bus Structure

VT13-280A

### 4.2.2 Data Loop

The data loop provides data transfer paths, data manipulation circuits, storage registers, and counters (figure 4-2). The data loop performs the following functions:

- Selects both of the ALU inputs from the following sources:

- 1. 16 general purpose registers

- 2. Operand register

- 3. Memory input latch, in memory control section

- 4. I/O register, in I/O data loop section

- 5. Status word (signals displayed by control-panel STATUS switch)

- 6. Instruction register (masked), in central control section

- 7. Program counter

- 8. Control store literal which consists of a 16-bit mask field from the control store buffer.

- Performs arithmetical and logical operations on the ALU inputs.

- c. Performs single and double length, bidirectional, open or closed, arithmetical or logical shifts in accordance with the contents of the shift counter.

- Stores and selects the desired test conditions such as ALU output zero, overflow, carry, SENSE switches, etc.

The ALU performs arithmetic and logical functions under control of the control store buffer. The ALU output is applied to the memory control and I/O data loop sections.

### 4.2.3 Memory Control

The memory control performs tasks initiated by the central control, I/O control, or options (on option board). It acknowledges acceptance of these tasks to the requesting section and signals completion. Once a request is accepted, no further requests are acknowledged (one exception to this rule permits the central control to override a previous request before it has been completed). Priority memory access (PMA) requests have a higher priority than I/O requests, and I/O requests have a higher priority than central control requests.

The following functions are performed by the memory control:

- Accepts tasks from central control and stores the following information to complete the task:

- 1. Read/write

- Word/byte

- 3. Address source

- b. Accepts tasks from options

- c. Accepts tasks from I/O control

- d. Acknowledges receipt of tasks

- e. Resolves priority of simultaneous requests

- Defers requests if higher priority devices, such as PMA, request use of the memory bus.

- g. Provides asynchronous operation and drivers/receivers for the memory bus.

- h. Signals completion of scheduled task.

Since the memory control operates asynchronously, the central control is free to perform other non-memory operations while the scheduled task is being executed. The memory control's ability to accept tasks from the I/O control permits direct memory access (DMA) operations to cycle steal without interfering with non-memory operations in the remainder of the processor.

### 4.2.4 I/O Data Loop

The I/O data loop (see figure 4-2 for I/O data paths) contains a multiplexor, I/O register, and drivers and receivers. Three sources of data are applied to the I/O data loop: data from the I/O bus, data from the ALU, and data from the memory I/O latch. The input data is selected by the I/O multiplexor under control of I/O control signals and transferred onto the bidirectional I/O bus.

In addition to being applied to the I/O drivers, the output of the I/O register is applied to the data loop and memory control sections.

### 4.2.5 I/O Control

The I/O control operates under control of an independent I/O control store and performs I/O operations initiated either by the central control or peripheral device activity. This permits I/O operations to proceed with minimum impact on other internal processor functions. The I/O control performs the following functions:

- a. Programmed I/O initiated by the central control.

- b. DMA trap-in/trap-out operations (up to 372,900 words per second, with semiconductor memory).

- High-speed DMA trap-in/trap-out operations (up to 969,600 words per second, with semiconductor memory).

- d. I/O interrupts

### 4.3 CENTRAL CONTROL CIRCUITS

This section describes the hardware circuits of the central control. To understand the functions of the central control, one must also become familiar with the microprogramming

operations (firmware). Listed below are sections of this manual containing microprogramming information:

- a. Control-Store Word Format (section 4.8)

- b. Control-Store Addressing (section 4.9)

- c. Microprogramming Examples (section 4.11)

Other microprogramming documents to be used in conjunction with this manual are:

- a. The Microprogramming Guide (98 A 9906 07x) describes capabilities, techniques, and coding of microprogramming.

- The Micro-Word Flowcharts (98A0887) are contained in the System Maintenance Manual.

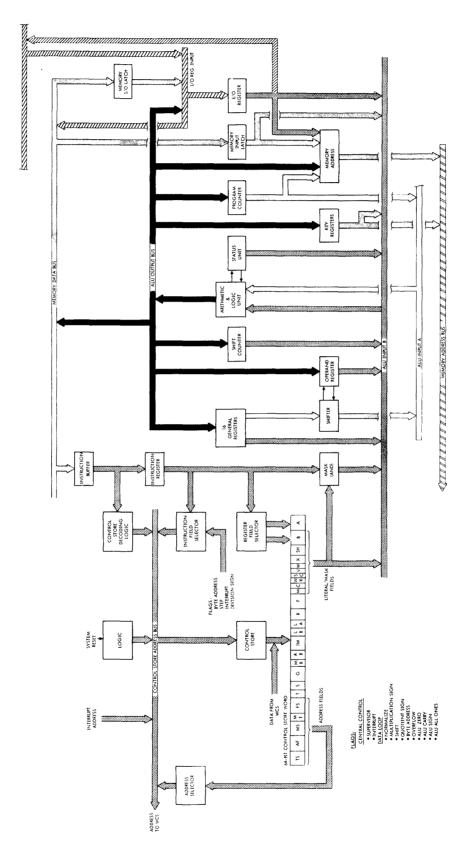

The circuits of the central control are shown in the block diagram of figure 4-3. Page numbers of the processor logic diagrams are provided in parentheses for each circuit block.

### 4.3.1 Instruction Register

The 16-bit instruction register receives instructions M1In + (0-15) from the instruction buffer (in the memory control section) which is then free to accept new instructions. This double buffering of instructions provides a pipelining technique that allows the next instruction to be fetched during an otherwise unused memory cycle. Refer to section 3 of Microprogramming Guide for further information on the instruction pipeline.

Data is clocked into the instruction register by clock signals that result from gating the full clock KKC2 + with CTEG0 +

and CBGO+. The register clocks occur whenever the control-store buffer T field contains 00 (CTEQ0+ is high) and the G field bit 0 is true (CBG0+ is high). The register generates instructions C2ln(0-15) in both true and complement form.

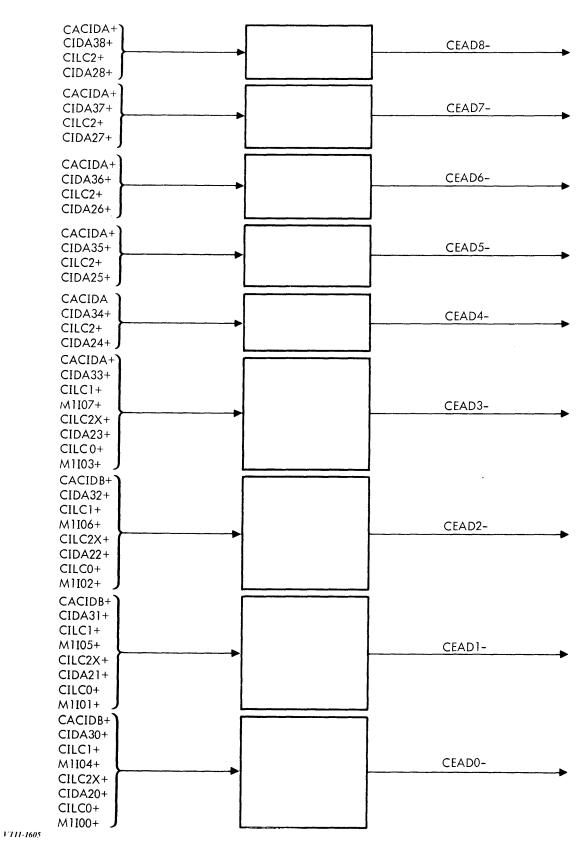

### 4.3.2 Instruction Field Selector

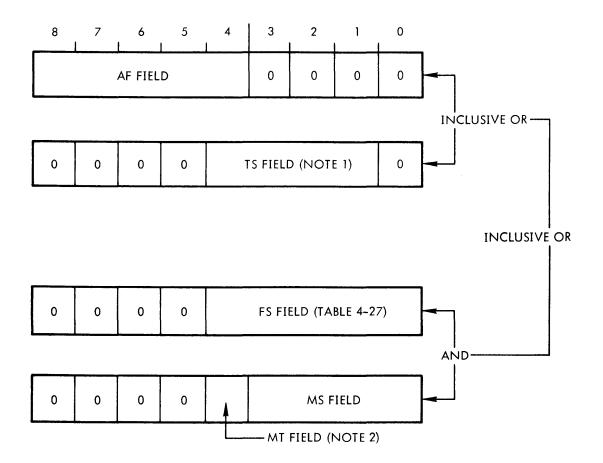

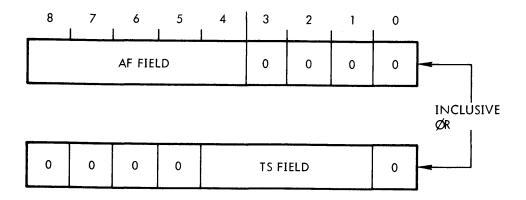

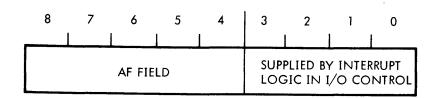

The instruction field selector consists of ten 8-input multiplexors which can select a field of up to five bits from the instruction register to form the low order bits of the control store address. This is accomplished by using the FS field of the control store buffer CBFSn + (0-3) to specify which of 16 possible fields are to be extracted and applied to the control store address lines CEADn- (0-8). Since there are not enough bits in the 16 bit instruction register to provide 16 5-bit fields, the remaining bits (multiplexor inputs) are either grounded to provide a source of logical ones to the control-store address or connected to various processor flags for conditional branching. All outputs from the instruction field selector are masked by bits in the MS and MT fields of the control store buffer, thus providing a generalized method for generating addresses. That is, addresses may be formed which either depend on the contents of the instruction register or may be arbitrarily specified by selecting a field position containing logical ones and then masking off the desired logical zero bits using the MS and MT fields.

Bits 0, 1, and 2 of the FS field select one input of each multiplexor. The bit-3 active low and high signals of the FS field (CBFS3– and CBFS3+) enable the five A multiplexors CFSAn + (0-4) or the five B multiplexors CFSBn + (0-4). The multiplexor truth table is shown in table 4-1.

Table 4-1. Instruction Multiplexor Truth Table (IC Type SN74151)

|          | BF Sr<br>(2-0) |    | CBFS3± | INPUT DATA |   |   |     |     |     |    | OUTPUT<br>CFSxn+ |   |

|----------|----------------|----|--------|------------|---|---|-----|-----|-----|----|------------------|---|

| PINS PIN |                |    |        |            |   |   | PIN | PIN |     |    |                  |   |

| 9        | 10             | 11 | 7      | 4          | 3 | 2 | 1   | 15  | 14  | 13 | 12               | 6 |

|          |                |    | Н      |            |   |   |     |     |     |    |                  | Н |

|          | L              | L  | L      | L          |   |   |     |     |     |    |                  | Н |

| L        | L              | L  | L      | Н          |   |   |     |     |     |    |                  | L |

| L        | L              | Ξ  | L      |            | L |   |     |     |     |    |                  | Н |

| L        | L              | Н  | L      |            | Н |   |     |     |     |    |                  | L |

| L        | Н              | L  | L      |            |   | L |     |     |     |    |                  | Н |

| L        | Н              | L  | L      |            |   | Н |     |     |     |    |                  | L |

| L        | Н              | Н  | L      |            |   |   | L   |     |     |    |                  | Н |

| L        | Н              | Н  | L      |            |   |   | Н   |     |     |    |                  | L |

| Н        | L              | L  | L      |            |   |   |     | L   |     |    |                  | Н |

| Н        | L              | L  | L      |            |   |   |     | Н   |     |    |                  | L |

| Н        | L              | Н  | L      |            |   |   |     |     | L   |    |                  | Н |

| Н        | L              | Н  | L      |            |   |   |     |     | _ н |    |                  | L |

| Н        | Н              | L. | L      |            |   |   |     |     |     | L  |                  | Н |

| Н        | Н              | L  | L      |            |   |   |     |     |     | Н  |                  | L |

| Н        | Н              | Н  | L      |            |   |   |     |     |     |    | L                | Н |

| Щ        | Н              | Н  | L      |            |   |   |     |     |     |    | Н                | L |

NOTE: 1. H = HIGH, L = LOW, AND NO H OR L = IRRELEVENT INPUT.

2. THE FIVE A MULTIPLEXORS CFSAn+(0-4) ARE ENABLED WITH.

THE FIVE A MULTIPLEXORS CFSAn+(0-4) ARE ENABLED WITH A LOW CBFS3-, AND THE FIVE B MULTIPLEXORS CFSBn+(0-4) WITH A LOW CBFS3+.

VTII-1601A

Figure 4-3. Central Control Block Diagram

### 4.3.3 Instruction Decoder

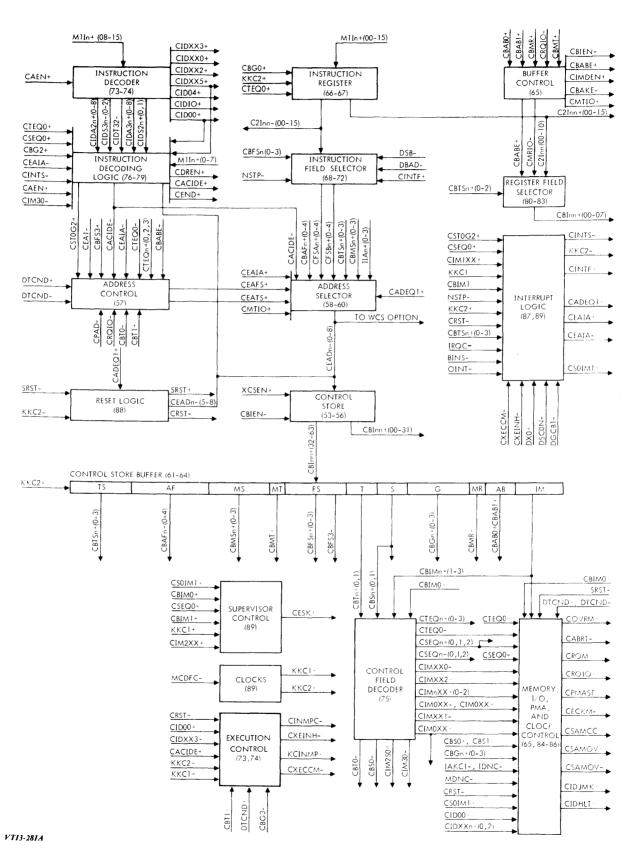

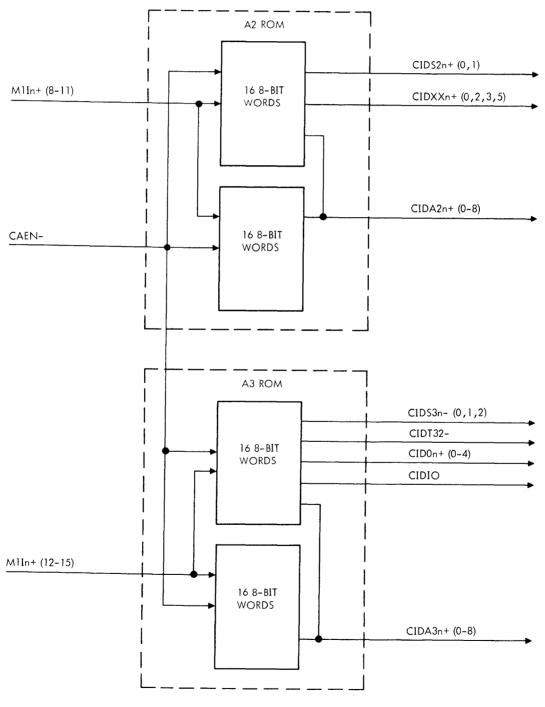

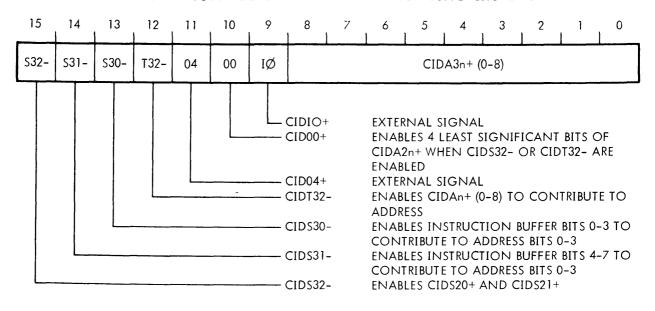

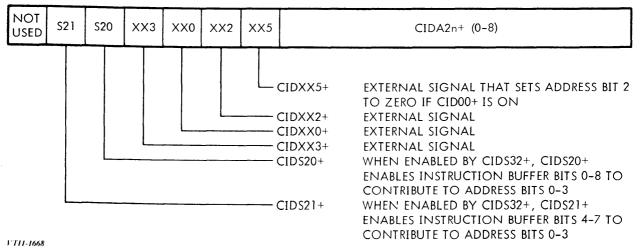

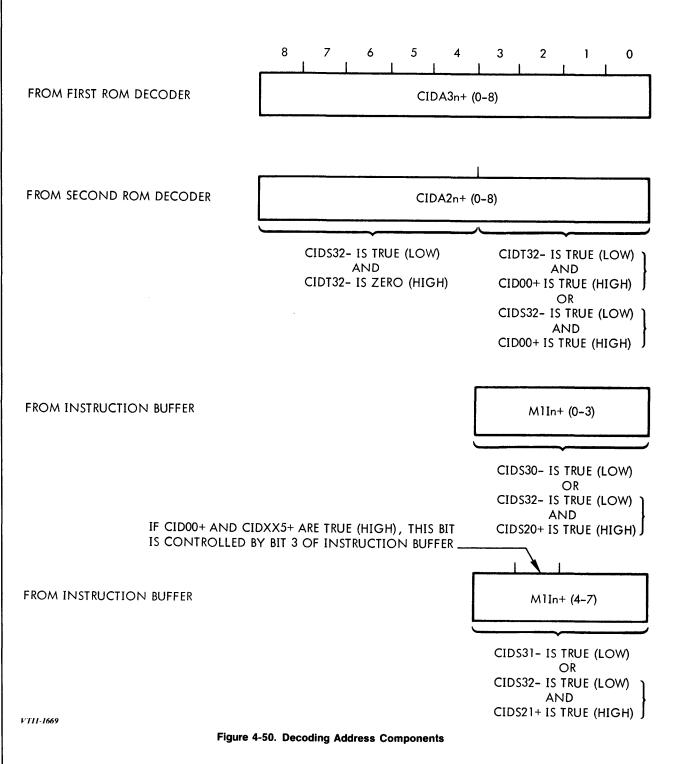

The instruction decoder provides preliminary decoding of the two most-significant 4-bit fields of the instruction buffer M1ln + (8-15). Decoding is accomplished with ROMs (read only memories) that are programmed for optimum performance. As illustrated in figure 4-4, the ROMs are divided

into two sections, A2 and A3. The A2 ROM decodes M1ln + (8-11) and produces 9-bits of output data CIDA2n + (0-8) plus control signals. The A3 ROM decodes M1ln + (12-15) and produces 9-bits of output data CIDA3n + (0-8) plus control signals. The two 9-bit data words are applied to the instruction decoding logic where they are combined with the two least-significant 4-bit fields of the instruction buffer.

Figure 4-4. Instruction Decoder ROMs Block Diagram

VT11-1602

A low CAEN- enables the ROMs. Decoded halt and jump-and-mark signals (CIDHLT+ and CIDJMK+) are derived from ROM control signals CID00+, CIDXX0, and

CIDXX2 + . Truth tables for the A2 and A3 ROMs are shown in tables 4-2 and 4-3.

Table 4-2. A2 ROM Truth Table

| INPUT BITS | OUTPUTS (CID)                                                                                                        |  |  |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 11 10 9 8  | S21+<br>S20+<br>XX3+<br>XX0+<br>XX2+<br>XX2+<br>A28+<br>A28+<br>A27+<br>A26+<br>A26+<br>A26+<br>A21+<br>A21+<br>A20+ |  |  |  |  |  |  |  |

|            |                                                                                                                      |  |  |  |  |  |  |  |

NOTE: L = LOW, H = HIGH

VT11-1603

Table 4-3. A3 ROM Truth Table